锁存器(Latch)是一种在数字电路中广泛使用的存储元件,它能够存储一位二进制信息。锁存器电路的触发方式有很多种,包括同步触发、边沿触发、电平触发等。

一、锁存器的基本概念

锁存器是一种具有记忆功能的电路,它可以在没有时钟信号的情况下保持输出状态不变。锁存器通常由一个或多个触发器(Flip-Flop)组成,触发器是锁存器的基本单元。触发器可以是SR(Set-Reset)、JK、D(Data)或T(Toggle)触发器等类型。

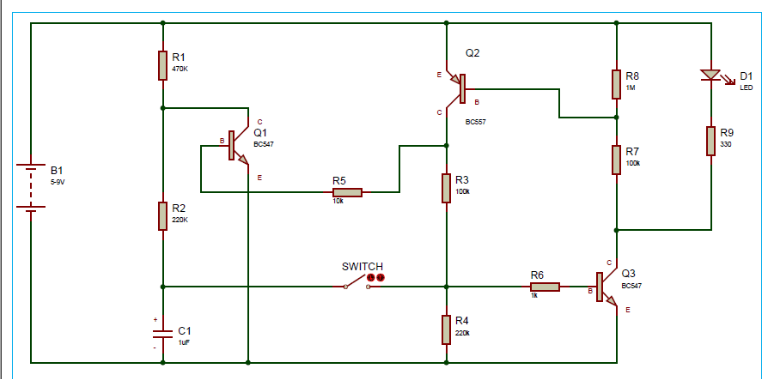

二、锁存器的工作原理

锁存器的工作原理主要依赖于触发器。触发器是一种具有两个稳定状态的电路,它们可以是“0”或“1”。触发器的状态转换依赖于输入信号,这些输入信号可以是同步信号、边沿信号或电平信号。

- SR触发器 :SR触发器有两个输入端,分别为S(Set)和R(Reset)。当S=1且R=0时,触发器的输出为1;当R=1且S=0时,触发器的输出为0;当S=1且R=1时,触发器的输出状态不确定。

- JK触发器 :JK触发器与SR触发器类似,但它具有更灵活的控制方式。当J=1且K=0时,触发器的输出为1;当J=0且K=1时,触发器的输出为0;当J=1且K=1时,触发器的输出状态翻转;当J=0且K=0时,触发器的输出保持不变。

- D触发器 :D触发器的输出仅依赖于输入D。当时钟信号上升沿到来时,D触发器的输出将与输入D同步。

- T触发器 :T触发器的输出在时钟信号的上升沿到来时翻转,如果输入T=1,则输出翻转;如果输入T=0,则输出保持不变。

三、锁存器的触发方式

锁存器的触发方式决定了触发器状态转换的时机,常见的触发方式包括同步触发、边沿触发和电平触发。

- 同步触发 :同步触发是指触发器的状态转换与时钟信号同步进行。在同步触发方式下,触发器的状态转换仅在时钟信号的上升沿或下降沿发生。同步触发的优点是易于实现同步操作,但可能存在时钟竞争问题。

- 边沿触发 :边沿触发是指触发器的状态转换仅在时钟信号的边沿(上升沿或下降沿)发生。边沿触发的优点是能够减少时钟竞争问题,但需要精确控制时钟信号的边沿。

- 电平触发 :电平触发是指触发器的状态转换依赖于输入信号的电平。在电平触发方式下,触发器的状态转换可以在任何时刻发生,只要输入信号满足触发条件。电平触发的优点是灵活性高,但可能存在稳定性问题。

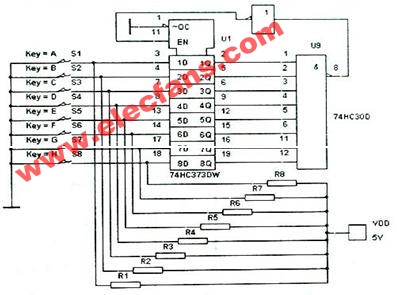

四、锁存器的应用

锁存器在数字电路中有广泛的应用,包括数据存储、状态控制、时序控制等。

- 数据存储 :锁存器可以用于存储数据,例如在计算机中存储指令和数据。

- 状态控制 :锁存器可以用于控制数字电路的状态,例如在有限状态机中控制状态转换。

- 时序控制 :锁存器可以用于实现时序控制,例如在数字钟表中控制时钟信号。

五、锁存器的设计

设计锁存器时,需要考虑以下几个方面:

- 触发方式 :根据应用需求选择合适的触发方式,如同步触发、边沿触发或电平触发。

- 稳定性 :确保锁存器在各种条件下都能稳定工作,避免出现不稳定状态。

- 功耗 :在设计锁存器时,需要考虑功耗问题,尽量降低功耗。

- 集成度 :在集成电路中,锁存器的集成度也是一个重要的考虑因素,需要在性能和成本之间找到平衡。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电路

+关注

关注

172文章

5901浏览量

172126 -

二进制

+关注

关注

2文章

795浏览量

41643 -

锁存器

+关注

关注

8文章

906浏览量

41494 -

数字电路

+关注

关注

193文章

1605浏览量

80577

发布评论请先 登录

相关推荐

锁存器电路通过什么触发的

锁存器电路通过什么触发的

评论