一、引言

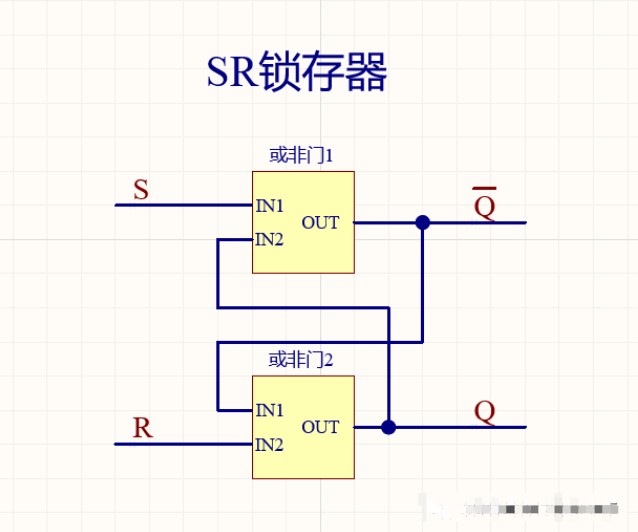

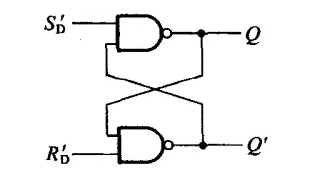

SR锁存器(Set-Reset Latch)是数字电路中的一种基本存储元件,用于存储一个比特(bit)的数据。它由两个互补的门电路组成,通常是两个非门(或非门、与非门)构成,通过两个输入端(S和R)来控制锁存器的状态。尽管SR锁存器结构简单且功能强大,但在特定输入条件下会进入一种被称为“不定状态”的特殊状态。

二、SR锁存器的基本工作原理

SR锁存器通过两个输入端S(Set)和R(Reset)来控制其输出状态。基本的工作原理如下:

- 置位(Set) :当S=1且R=0时,锁存器被置位,输出Q=1,Q'=0。此时,S端被称为置数端。

- 复位(Reset) :当S=0且R=1时,锁存器被复位,输出Q=0,Q'=1。此时,R端被称为清零端。

- 保持(Hold) :当S=0且R=0时,锁存器保持上一状态不变。

三、不定状态的产生原因

SR锁存器的不定状态主要源于其输入端S和R在同时有效(即同时为1)时的特殊行为。在理想情况下,当S和R均为1时,SR锁存器的输出状态应该是确定的。然而,在实际电路中,由于信号传输的延迟、器件间的差异以及时序问题等因素,当S和R同时由0变为1时,中间会引入短暂的“01”或“10”这样的中间状态。这些中间状态的具体表现取决于信号传输的先后顺序和电路的物理特性,因此无法预测和确定。

此外,当S和R同时由有效(1)变为无效(0)时,由于信号传播速度的差异和电路内部的寄生效应,也可能导致输出状态的不确定。这种由输入变化引起的输出状态不确定现象,就是SR锁存器的不定状态。

四、不定状态的表现形式

SR锁存器进入不定状态时,其输出Q和Q'的状态无法预测。具体来说,Q和Q'可能同时为高电平、同时为低电平,或者一个为高电平而另一个为低电平。这种不确定性会对电路的稳定性和可靠性产生严重影响。

在实际应用中,为了避免SR锁存器进入不定状态,通常会在设计时采取以下措施:

- 避免S和R同时有效 :在电路设计中,应确保S和R不会同时被置为高电平。这可以通过逻辑门电路的设计来实现,例如使用与门(AND gate)来确保S和R不会同时为1。

- 使用时钟信号控制 :在更复杂的电路中,可以使用时钟信号来控制SR锁存器的输入变化。这样,只有在时钟信号的特定边沿(如上升沿或下降沿)到来时,S和R的输入才会被锁存器接收并处理。这种方式可以有效避免不定状态的产生。

- 优化电路布局和布线 :合理的电路布局和布线可以减少信号传输的延迟和干扰,降低不定状态发生的可能性。

五、不定状态的影响与应对措施

SR锁存器的不定状态会对电路的稳定性和可靠性产生严重影响。在数字系统中,不确定的输出状态可能导致数据错误、逻辑混乱甚至系统崩溃。因此,必须采取措施来避免或减轻不定状态的影响。

除了上述的避免S和R同时有效、使用时钟信号控制以及优化电路布局和布线等措施外,还可以采取以下策略来应对不定状态:

- 增加状态检测电路 :在SR锁存器的输出端增加状态检测电路,用于检测输出是否处于不定状态。一旦发现不定状态,可以立即采取措施(如复位电路)来恢复正常的输出状态。

- 使用更稳定的锁存器类型 :在某些对稳定性要求极高的应用中,可以考虑使用更稳定的锁存器类型(如D锁存器、JK锁存器等),这些锁存器具有更复杂的控制逻辑和更高的稳定性。

六、结论

SR锁存器作为数字电路中的一种基本存储元件,在数字系统中发挥着重要作用。然而,其不定状态的存在对电路的稳定性和可靠性构成了威胁。通过深入理解SR锁存器的工作原理和不定状态的产生原因,我们可以采取有效的措施来避免或减轻不定状态的影响。

-

元件

+关注

关注

4文章

912浏览量

36688 -

锁存器

+关注

关注

8文章

906浏览量

41494 -

门电路

+关注

关注

7文章

199浏览量

40158 -

数字电路

+关注

关注

193文章

1605浏览量

80578

发布评论请先 登录

相关推荐

sr锁存器不定状态的产生原因

sr锁存器不定状态的产生原因

评论