源漏区嵌入SiC 应变技术被广泛用于提高90nm 及以下工艺制程 NMOS 的速度,它是通过外延生长技术在源漏嵌入 SiC 应变材料,利用硅和碳晶格常数不同,从而对沟道和衬底硅产生应力,改变硅导带的能带结构,从而降低电子的电导有效质量和散射概率。

硅的晶格常数是5.431A,碳的晶格常数是3.57A,硅与碳的不匹配率是34.27%,从而使得 SiC 的晶格常数小于纯硅,并且碳的晶格常数远小于硅的晶格常数,SiC只需很少的碳原子就可得到很高的应力。图2-7所示为在硅衬底上外延生长SiC应变材料外延。SiC会对横向的沟道产生张应力,从而使沟道的晶格发生形变,晶格变大。

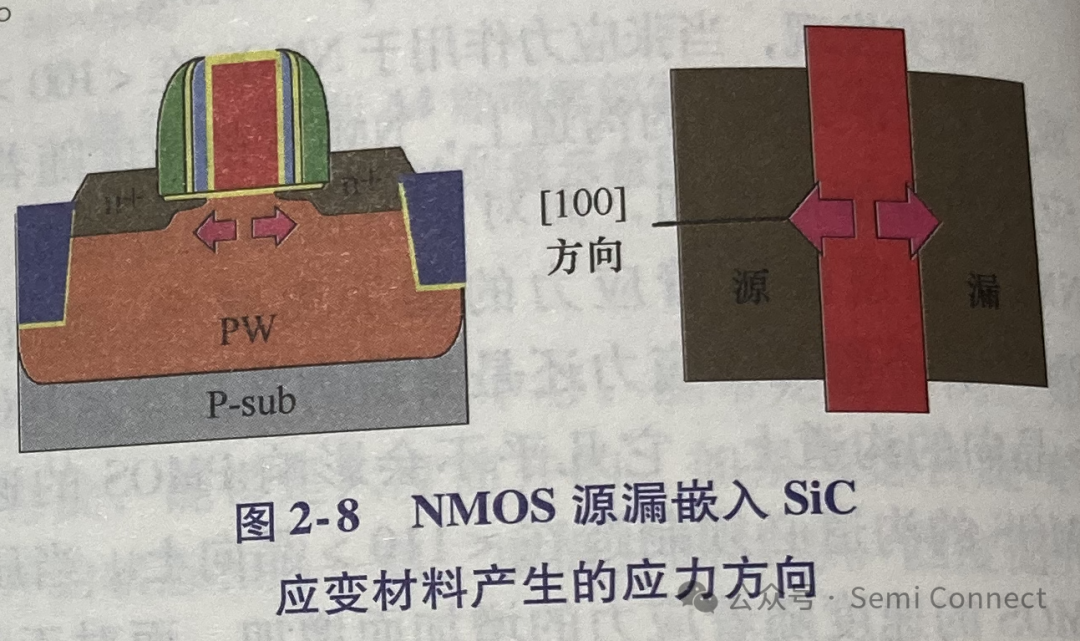

在 NMOS 的源漏嵌入SiC 应变材料,如图2-8所示,NMOS的沟道制造在[100] 方向上,SiC应变材料会在该方向产生单轴的张应力,得到的主能谷的等能面的轴向都是垂直于沟道分向,沿沟道方向单轴张应力会减小沟道方向的电子电导有效质量和散射概率,源漏嵌入SiC应变材料可以有效地提高NMOS 的速度。

源漏嵌入 SiC 应变材料是选择外延(Se-lective Epitaxial Growth,SEG)技术。选择外延技术是利用外延生长的基本原理,以及硅在绝缘体上很难核化成膜的特性,在硅表面的特定区域生长外延层而其他区域不生长的技术。外延生长的基本原理是根据硅在SiO2上核化的可能性最小,在Si3N4上比在SiO2上大一点,在硅上可能性最大的特性完成的。这是因为在硅衬底上外延生长硅层是同质外延,而在SiO2和Si3N4上是异质外延,所以落在绝缘体上的原子因不易成核而迁移到更易成核的硅单晶区内。

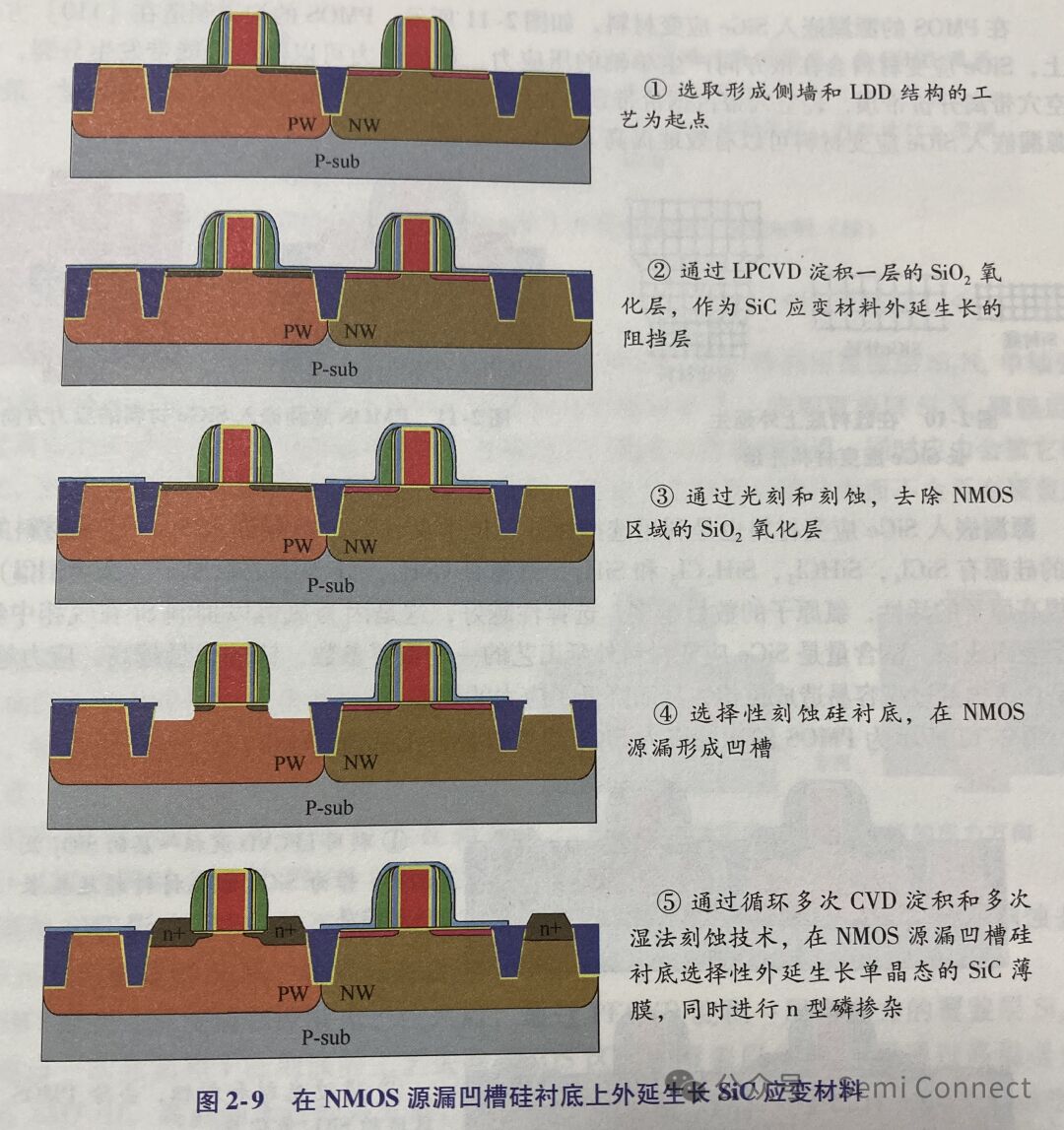

实现源漏嵌入 SiC 应变材料工艺具有一定的难度,因为SiC 应变材料外延生长工艺的选择性比较差,它在源漏凹槽衬底生长的同时,也会在氧化物等非单晶区域上生长,例如在侧壁和STI上生长 。可以通过CVD淀积和湿法刻蚀技术,进行多次淀积和多次刻蚀的方式来改善外延生长SiC 应变材料,因为利用CVD工艺可以在单晶硅衬底获得单晶态的SiC 薄膜,而在氧化物等非单晶区域上得到非晶态的SiC 薄膜,由于非晶态的SiC 薄膜具有较高的刻蚀率,所以可以通过多次淀积和多次刻蚀循环在源漏单晶硅衬底上选择性生长出一定厚度的单晶态SiC薄膜。

另外,SiC 应变材料在高温热退火的热稳定性比较差,在大于900°C的高温热退火中,SiC 应变材料中的部分碳原子会离开替位晶格的位置,一旦替位碳原子离开替位晶格,应力就会失去,离开的碳原子的数量与高温热退火的时间成正比。所以在 SiC 应变材料薄膜形成后,必须严格控制高温退火的时间,而先进的毫秒退火工艺可以改善这一问题。

图2-9所示为 NMOS 的源漏嵌入SiC 应变材料的工艺流程。

- NMOS

+关注

关注

3文章

281浏览量

33978 - SiC

+关注

关注

29文章

2612浏览量

61957 - 晶格

+关注

关注

0文章

93浏览量

9151

原文标题:源漏嵌入 SiC 应变技术

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

金属电阻应变片工作原理简介

浅析SiC-MOSFET

海飞乐技术现货替换IXFN50N120SIC场效应管

基于分布式光纤应变传感器技术的山体滑坡在线监测预警方案

漏源电压VDS相关资料下载

SiC碳化硅MOS驱动的PCB布局方法解析

SiCMOSFET的器件演变与技术优势

PNP与NPN哪个是“源”与”漏“的浑水

三菱PLC源型和漏型的区别

源漏嵌入SiC应变技术简介

源漏嵌入SiC应变技术简介

评论