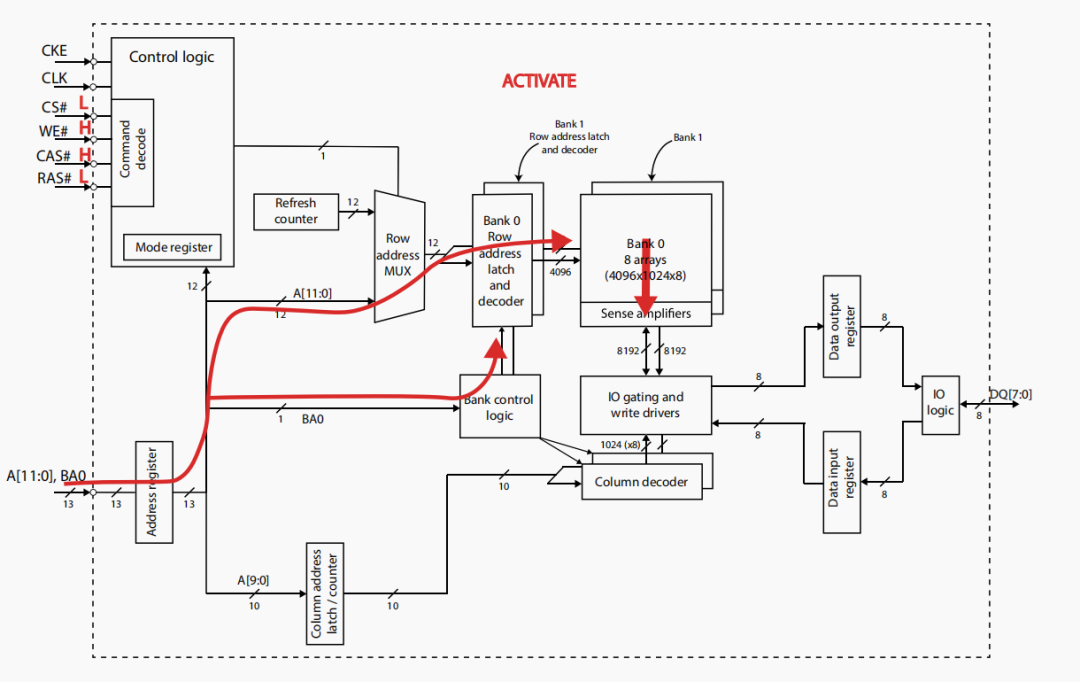

在向SDRAM 中的任何行发出 READ或 WRITE 命令之前,必须先打开该行。这是通过 ACTIVE 命令完成的。ACTIVE 命令的目的是打开或者说激活(active)bank中的一行并将数据从 DRAM 移动到bank的灵敏放大器。下图说明了 ACTIVE 命令的执行情况。

来自地址总线的地址 A11-A0存储在所选bank的行地址锁存器和译码器中。地址位BA选择bank及其行地址锁存器和解码器。

然后,将整个数据行读入灵敏放大器中。与 DRAM 类似,与ACTIVE 命令相关的两个timing是:行地址到列地址延迟 (tRCD)和行有效时间 tRAS。

tRCD是激活命令将数据从DRAM单元阵列移动到保持整个数据行的感测放大器所需的时间。在tRCD之后,可以发出某列读或写访问命令,通过输入/输出buffer和数据总线在感测放大器和内存控制器之间移动数据 。

行地址到列地址延迟tRCD,应除以时钟周期,向上取整到最接近的整数,以确定ACTIVE命令后读写的最早时钟边沿。例如,具有125 MHz 时钟(周期为8纳秒),20 纳秒的tRCD产生2.5 个时钟周期,四舍五入为 3。

向同一rank中不同行发出的ACTIVE 命令只能在先前激活的行被预充电后发出。

行激活时间,tRAS,是必须经过的最小时间,这之后才能向打开的行发出PRECHARGE命令。所以,tRAS也称为作为激活到预充电时间。

-

SDRAM

+关注

关注

7文章

423浏览量

55202 -

锁存器

+关注

关注

8文章

906浏览量

41493 -

命令

+关注

关注

5文章

683浏览量

22011

原文标题:SDRAM中的active命令介绍

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高分辨率视频图像处理中SDRAM控制器的设计

SDRAM的介绍及设计应用

SOPC中SDRAM controller 的Timing配置

【开源骚客】《轻松设计SDRAM控制器》第六讲—SDRAM写模块讲解

【开源骚客】《轻松设计SDRAM控制器》第八讲—命令解析模块讲解

SDRAM理论基础讲解

教程 | SDRAM读写时序介绍(配时序图)

SDRAM控制器的设备与VHDL实现

DRAM、SDRAM及DDR SDRAM之间的概念详解

如何操作SDRAM的自刷新命令而不影响正常读写操作?

如何操作SDRAM的自刷新命令

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

SDRAM中的active命令介绍

SDRAM中的active命令介绍

评论