当栅与衬底之间存在压差时,它们之间存在电场,静电边界条件使多晶硅靠近氧化层界面附近的能带发生弯曲,并且电荷耗尽,从而形成多晶硅栅耗尽区。该耗尽区会在多晶硅栅与栅氧化层之间产生一个额外的串联电容。当栅氧化层厚度减小到 2nm 以下,此电容的影响也会变得越来越严重,已经不再可以忽略。

多晶硅栅耗尽的宽度不像衬底量子效应那么复杂,它只需要采用简单的静电学就可以估算栅耗尽区的宽度。重掺杂的栅的掺杂浓度比轻掺杂的沟道的掺杂浓度要高,在亚阈值区,氧化层界面电位移的连续性意味着栅极的能带弯曲小于衬底的能带弯曲。考虑一个偏置到反型区的NMOS 的n型重掺杂的多晶硅,平带电压(VFB)和衬底电压降(Φs)、栅电压降(Φg)、氧化层电压降(Vox)之和等于栅压(Vg):

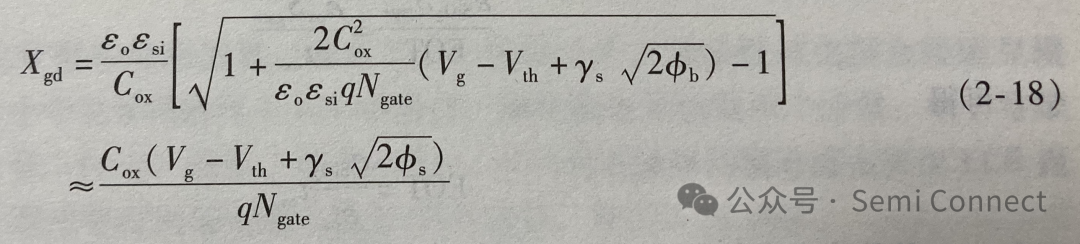

利用栅氧化层的边界条件和高斯定理对公式(2-17)进行化简求解,当Vg>Vth时,求得栅耗尽的宽度Xgd的公式如下:

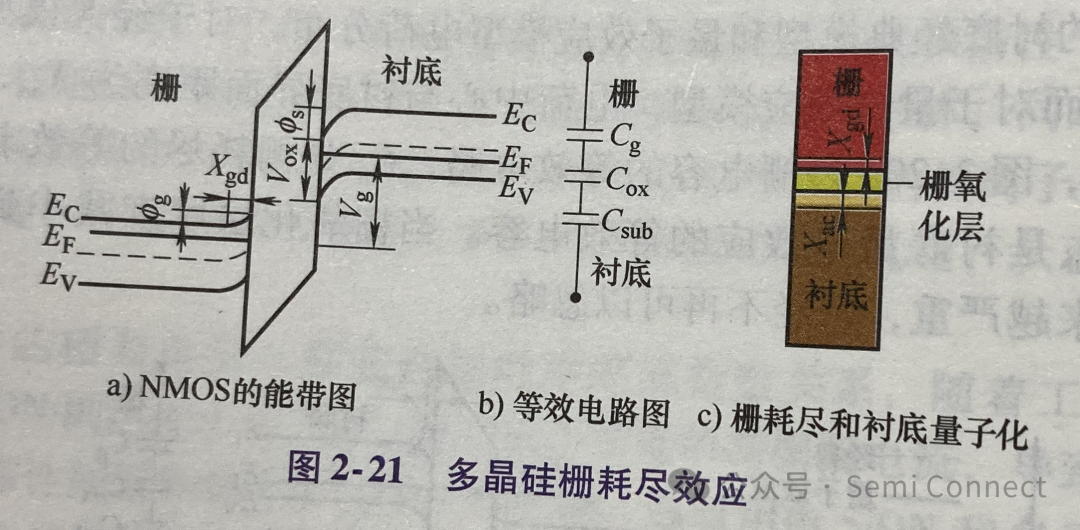

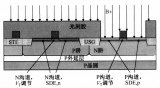

图2~21a所示为栅极耗尽层的宽度Xgd,图2-21b所示为栅耗尽的等效电容、栅氧化层的等效电容和衬底量子效应的等效电容的等效电路图,图2-21c所示为栅耗尽和衬底量子化的示意图。

-

多晶硅

+关注

关注

3文章

240浏览量

29266 -

静电

+关注

关注

1文章

505浏览量

36365 -

NMOS

+关注

关注

3文章

294浏览量

34345

原文标题:多晶硅栅耗尽效应

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【转】一文看懂MOS器件的发展与面临的挑战

分析MOS管未来发展与面临的挑战

低温多晶硅的工作原理是什么?

低温多晶硅,低温多晶硅是什么意思

多晶硅上市公司有哪些_国内多晶硅上市公司排名

多晶硅生产流程是什么_单晶硅与多晶硅的区别

多晶硅栅(Poly-Si Gate)

多晶硅栅工艺的制造流程

多晶硅栅耗尽效应简述

多晶硅栅耗尽效应简述

评论