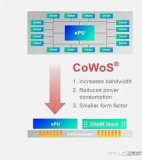

CoWoS(Chip-on-Wafer-on-Substrate)是一种先进的半导体封装技术,它结合了芯片堆叠与基板连接的优势,实现了高度集成、高性能和低功耗的封装解决方案。以下是对CoWoS封装技术的详细解析,包括其定义、工作原理、技术特点、应用领域以及未来发展趋势等方面。

一、定义

CoWoS封装技术是一种将芯片堆叠在晶圆上,并再将整个结构封装在基板上的先进封装方法。该技术可以细分为“CoW(Chip-on-Wafer)”和“WoS(Wafer-on-Substrate)”两个步骤:首先,通过CoW步骤将芯片堆叠在晶圆上;然后,通过WoS步骤将整个晶圆结构封装在基板上。这种封装方式不仅减少了芯片占用的空间,还显著降低了功耗和成本,是现代半导体封装技术的重要进展之一。

二、工作原理

CoWoS封装技术的工作原理主要基于芯片堆叠和基板连接技术。在CoW步骤中,多个芯片通过先进的连接技术(如微凸块、硅通孔等)堆叠在晶圆上,形成高度集成的芯片堆叠结构。然后,在WoS步骤中,这个堆叠结构被封装在基板上,通过基板与外部电路进行连接。整个封装过程中,CoWoS技术充分利用了硅通孔(TSV)等先进技术,实现了芯片间的高效互联和信号传输。

三、技术特点

- 高度集成 :CoWoS封装技术可以将多个芯片堆叠在同一晶圆上,形成高度集成的封装结构。这种集成方式不仅减少了芯片占用的空间,还提高了系统的整体性能。

- 高性能 :通过芯片堆叠和基板连接技术,CoWoS封装技术实现了芯片间的高效互联和信号传输。这种高效的互联方式使得系统能够处理更复杂、更高性能的任务。

- 低功耗 :由于芯片堆叠和基板连接技术的优化,CoWoS封装技术能够显著降低系统的功耗。这对于需要长时间运行的高性能系统来说尤为重要。

- 低成本 :相比传统的封装技术,CoWoS封装技术在提高集成度和性能的同时,还降低了制造成本。这主要得益于其高效的封装流程和优化的材料使用。

- 灵活性 :CoWoS封装技术可以根据不同的应用需求进行灵活设计。例如,可以根据需要选择不同的芯片堆叠方式和基板材料来满足不同的性能要求。

四、应用领域

CoWoS封装技术凭借其高度集成、高性能和低功耗等优点,在多个领域得到了广泛应用。以下是一些主要的应用领域:

- 高性能运算(HPC) :在高性能运算领域,CoWoS封装技术能够提供强大的计算能力和高效的数据传输能力,满足复杂计算任务的需求。

- 人工智能(AI) :在人工智能领域,CoWoS封装技术被广泛应用于AI芯片和服务器中。通过提高芯片的集成度和性能,CoWoS封装技术能够支持更复杂的AI算法和更高效的计算任务。

- 数据中心 :在数据中心领域,CoWoS封装技术能够提供高密度的计算能力和低功耗的解决方案,满足数据中心对高性能和低能耗的需求。

- 5G通讯 :在5G通讯领域,CoWoS封装技术被用于5G基站和核心网设备中。通过提高芯片的集成度和性能,CoWoS封装技术能够支持更高速的数据传输和更低的延迟。

- 物联网(IoT) :在物联网领域,CoWoS封装技术被用于各种智能设备和传感器中。通过提高芯片的集成度和低功耗特性,CoWoS封装技术能够支持更广泛的物联网应用场景。

五、未来发展趋势

随着半导体技术的不断发展和应用需求的不断增长,CoWoS封装技术将继续保持其领先地位并迎来更广阔的发展前景。以下是一些未来可能的发展趋势:

- 技术创新 :随着新材料、新工艺和新技术的不断涌现,CoWoS封装技术将不断进行创新和改进。例如,可以采用更先进的连接技术、更高效的散热方案以及更环保的材料来提高封装性能和降低成本。

- 市场扩展 :随着5G、物联网、人工智能等新兴技术的快速发展和应用场景的不断拓展,CoWoS封装技术的市场需求将持续增长。未来,CoWoS封装技术将广泛应用于更多领域和场景中,为各种高性能、低功耗的设备提供有力支持。

- 标准化与规范化 :随着CoWoS封装技术的广泛应用和市场竞争的加剧,标准化和规范化将成为行业发展的重要趋势。通过制定统一的标准和规范来指导技术研发和市场应用,可以促进CoWoS封装技术的健康发展和市场繁荣。

综上所述,CoWoS封装技术作为一种先进的半导体封装技术,在高度集成、高性能和低功耗等方面具有显著优势。随着技术的不断发展和应用需求的不断增长,CoWoS封装技术将继续保持其领先地位并迎来更广阔的发展前景。

-

半导体

+关注

关注

334文章

27286浏览量

218079 -

封装技术

+关注

关注

12文章

548浏览量

67981 -

CoWoS

+关注

关注

0文章

138浏览量

10485

发布评论请先 登录

相关推荐

全面详解CoWoS封装技术特点及优势

台积电第五代CoWoS封装技术即将问世 晶圆代工优势扩大

富士康进军Chiplet封装领域的三大挑战

主流的封装技术有哪些?如何区分?

什么是CoWoS封装技术?

什么是CoWoS封装技术?

评论