1. 偏移约束的作用

偏移约束(Offset Constraint)用来定义一个外部时钟引脚(Pad)和数据输入输出引脚之间的时序关系,这种时序关系也被称为器件上的Pad-to-Setup或Clock-to-Out路径这些约束对与外部元器件相连的接口十分重要,在这里,需要解释两个术语:

Pad-to-Setup:也被称为OFFSET IN BEFORE约束,是用来保证外部输入时钟和外部输入数据的时序满足FPGA内部触发器的建立时间要求的如下图TIN_BEFORE约束使得FPGA在进行DATA_IN和CLK_SYS布线时努力保证DATA_IN相对于CLK_SYS的延时小于TIN_BEFORE

Clock-to-Out:也被称为OFFSET OUT AFTER约束,是用来满足下游器件建立保持(setup/hold)要求或输出时钟和数据之间时序要求的

OFFSET IN BEFORE 或OFFSET OUT AFTER约束允许用户指定外部输入或输出引脚相对于时钟边沿到内部数据的延时

1.1输入偏移约束时序参考图

1.2输出偏移约束时序参考图

Xilinx FPGA有三个层次的约束:

Global OFFSET:为所有输入或输出指定相对某个特定时钟的约束;

Group OFFSET:为一组输入或者输出指定相对驱动他们的时钟的约束

Net-Specific OFFSET:为某个特定的输入或者输出指定相对其驱动时钟的约束;

在进行约束的详细讲解之前,必须明确两个概念:

建立时间setup time

指在触发器始终上升沿到来之前,数据必须保持稳定的时间,如果建立时间不够,数据将不能被打入触发器;

保持时间hold time

指触发器的时钟上升沿到来之后数据必须稳定不变的时间,如果保持时间不够,数据不能被打入触发器;

1.3建立保持时间时序图

2. OFFSET IN约束

OFFSET IN约束用来设定Pad-to-Setup时序要求OFFSET IN是对数据时钟关系的一种说明它当分析建立时间要求(data_delay+setup-clock_delay-clock_arrival要求满足约束条件)的时候,需要考虑时钟延时(clock delay)、时钟边沿(clock edge)、DLL/DCM引入的时钟相位

2.1. OFFSET IN BEFORE 约束

OFFSET IN BEFORE约束限定了数据从引脚传播到同步元件并在同步元件建立起来的所需的时间比如 “OFFSET = IN 2 ns BEFORE clock_pad”这个约束,限定数据必须在下一个时钟边沿到来之前2ns内读取,因此FPGA会规划使得数据相对时钟边沿的超前2ns之内

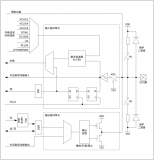

2.1OFFSET IN BEFORE约束带校准功能的电路

上图FPGA在布线时会尽力去满足如下不等式:

TData + TSetup - TClock 《= Toffset_IN_BEFORE;

2.1.1. VALID约束

OFFSET IN约束往往和VALID约束一起使用OFFSET IN约束在建立时间分析中作为建立时间要求使用,而VALID约束在保持时间约束中作为保持时间要求使用VALID约束指定了输入数据的持续时间在默认情况下,FPGA指定VALID和OFFSET的值相等,也即FPGA在默认情况下认为保持时间为0

2.2带有VALID约束的输入偏移约束

2.1.2. OFFSET IN约束的一个简单例子

FPGA的分析工具在综合时经常会用到一个词:Slack,即松弛时间,当Slack》0时,该路径设计满足时序要求;当Slack《0时,该路径不满足时序要求

Slack = (Requirement - (Data Path - Clock Path - Clock Arrival))

2.3OFFSET IN的简单例子时序

该约束为:

TIMESPEC TS_clock = PERIOD clock_grp 10 ns HIGH 50%;

OFFSET = IN 3 ns BEFORE clock;

2.4OFFSET IN约束时序报告

从时序约束报告的Slack的值可以看出,Data不能被Clock成功打入触发器FF0.

2.2. OFFSET IN AFTER约束

OFFSET IN AFTER和OFFSET IN BEFORE在本质上是一样的,只是形式上不一样,其约束效果是完全一样的OFFSET IN AFTER的约束公司如下:

TData + TSetup - TClock 《= TPeriod – Toffset_IN_AFTER;

3. OFFSET OUT约束

OFFSET OUT约束用来定义clock-to-pad时序要求OFFSET OUT约束是对外部clock-to-data的说明并且必须考虑clock_delay、clock edge和DLL/DCM时钟相位等

3.1. OFFSET OUT AFTER约束

OFFSET OUT AFTER约束定义了数据从同步元件传播到管脚最长允许时间可以形象地理解为时钟边沿到达器件边界时数据离开器件边界的时间“OFFSET = OUT 2 ns AFTER clock_pad”约束意思是从FPGA数据端口传输到下游器件的数据在参考时钟2ns之后一定可读

3.1OFFSET OUT AFTER约束带校准功能的电路

下面公式规定了数据时钟的这种关系:

TQ + TClock2Out + TClock 《= Toffset_OUT_AFTER;

OFFSET OUT AFTER约束沿着参考时钟路径和数据路径的最大延时不超过偏移值

3.1.1. OFFSET OUT AFTER约束的一个简单例子

同样的,OFFSET OUT的Slack也定义了输出约束的松弛时间:

Slack = (Requirement - (Clock Arrival + Clock Path + Data Path))

3.2OFFSET OUT 约束的简单例子

其约束应写为:

TIMESPEC TS_clock = PERIOD clock_grp 10 ns HIGH 50%;

OFFSET = OUT 3 ns AFTER clock;

3.3OFFSET OUT 时序约束报告

时序报告中Slack=-0.865ns,不满足时序约束要求

3.2. OFFSET OUT BEFORE约束

同样地,OFFSET OUT BEFORE和OFFSET OUT AFTER约束本质上没有什么不同,只是形式上的不一样的,其约束效果完全一样

-

FPGA

+关注

关注

1629文章

21729浏览量

602960 -

fpga编程

+关注

关注

0文章

4浏览量

4626

发布评论请先 登录

相关推荐

Xilinx FPGA编程技巧之常用时序约束详解

Xilinx FPGA编程技巧之常用时序约束详解

添加时序约束的技巧分析

什么是输入输出模块_输入输出模块有什么作用

STM32的8种GPIO输入输出模式

GPIO通用输入输出

一文详解FPGA编程技巧输入输出偏移约束

一文详解FPGA编程技巧输入输出偏移约束

评论