Model4芯片是一款高性能的全高清显示和智能控制SOC,采用国产自主 64 位高算力RISC-V内核,提供了丰富的互联外设接口,具备大容量存储和极强的扩展性。片内存储BROM 32KB、SRAM96KB以及DRAMSiP 16bit KGD(两种规格可选:DDR2 512Mb、 DDR3 1Gb),存储接口QSPI 支持 SPI NAND Flash / SPI Nor Flash,支持eMMC5.0接口。

如此多的存储器和存储接口,究竟有何区别?本文将以半导体存储类型为主线,带大家了解各个存储器的特点、优势以及联系。

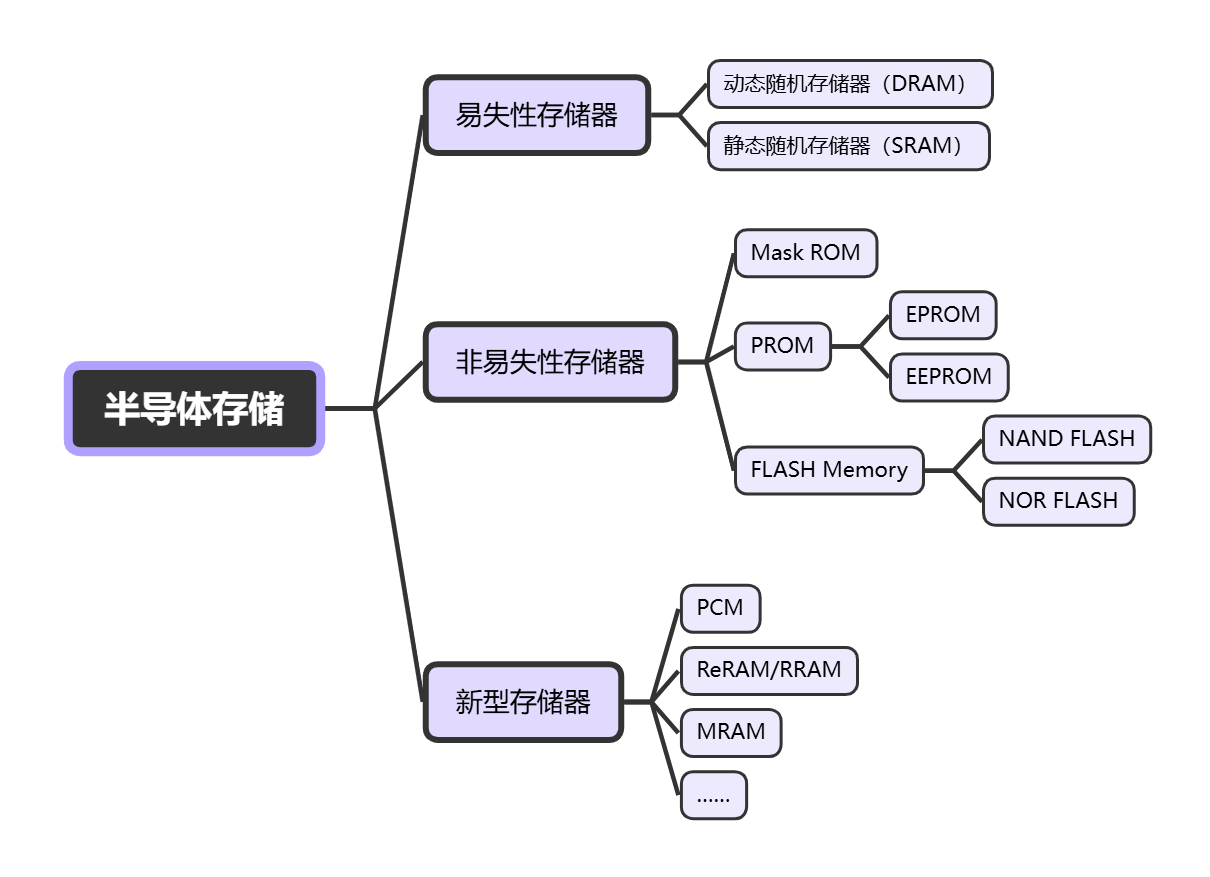

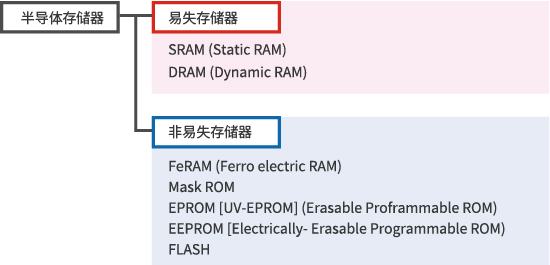

一、半导体存储分类

在介绍之前,我们先看一张图,以便理解。

现代存储技术,概括起来分为三部分:磁性存储(磁带、软盘等)、光学存储(DVD、蓝光光盘等)、半导体存储。我们今天要介绍的就是以“半导体集成电路”作为存储媒介的存储器——半导体存储。

半导体存储主要分为易失性(VM)存储器与非易失性(NVM)存储器。

(一)易失性存储器(VN)

易失性存储器主要分为DRAM和SRAM两种。

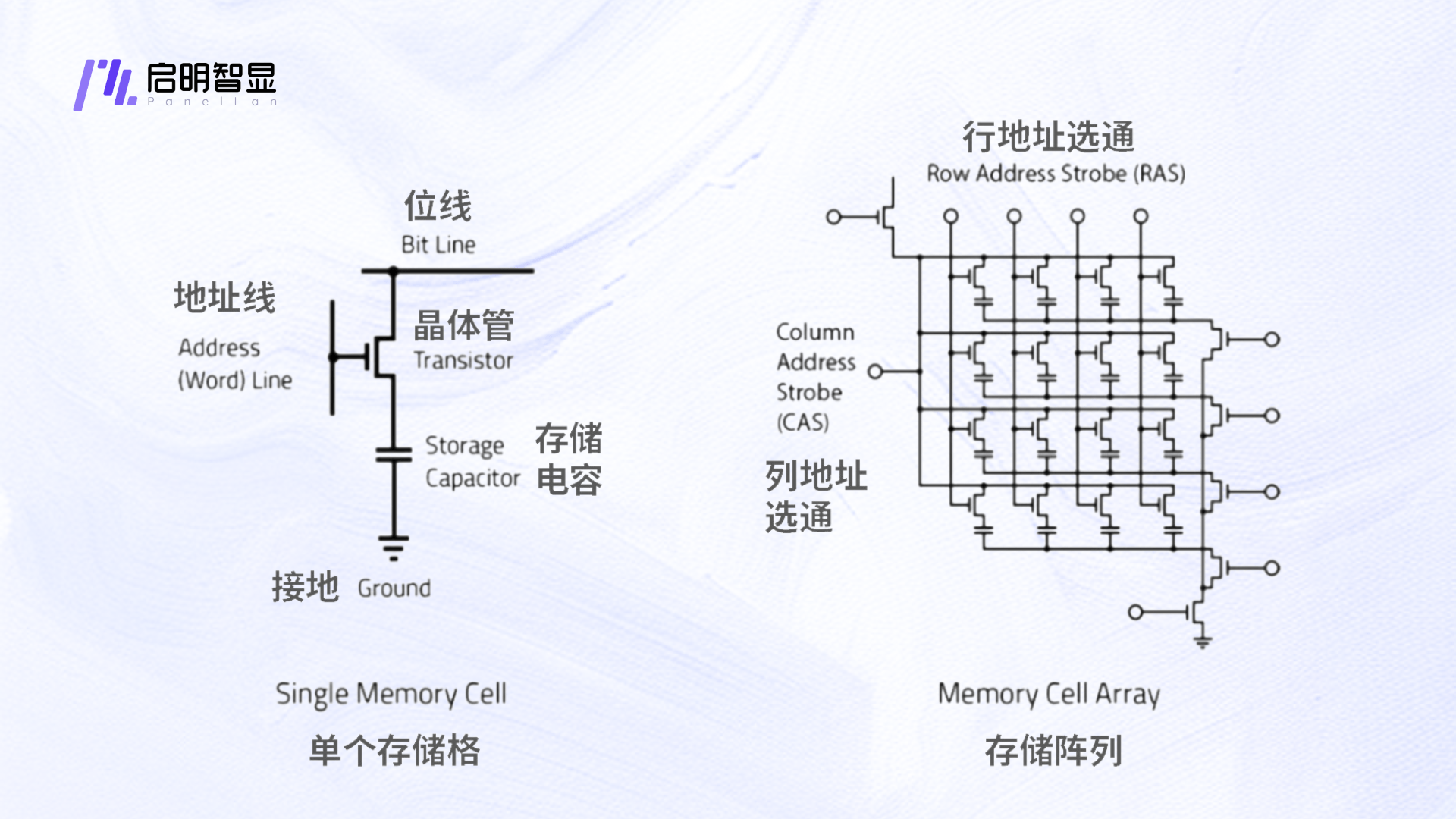

1.DRAM

DRAM由许多重复的位元格(Bit Cell)组成,每一个基本单元由一个电容和一个晶体管构成(又称1T1C结构)。电容中存储电荷量的多寡,用于表示“0”和“1”。而晶体管,则用来控制电容的充放电。

由于电容会存在漏电现象。所以,必须在数据改变或断电前,进行周期性“动态”充电,保持电势。否则,就会丢失数据。因此,DRAM才被称为“动态”随机存储器。

DRAM一直是计算机、手机内存的主流方案。计算机的内存条(DDR)、显卡的显存(GDDR)、手机的运行内存(LPDDR),都是DRAM的一种。(DDR基本是指DDRSDRAM,双倍速率同步动态随机存储器。)

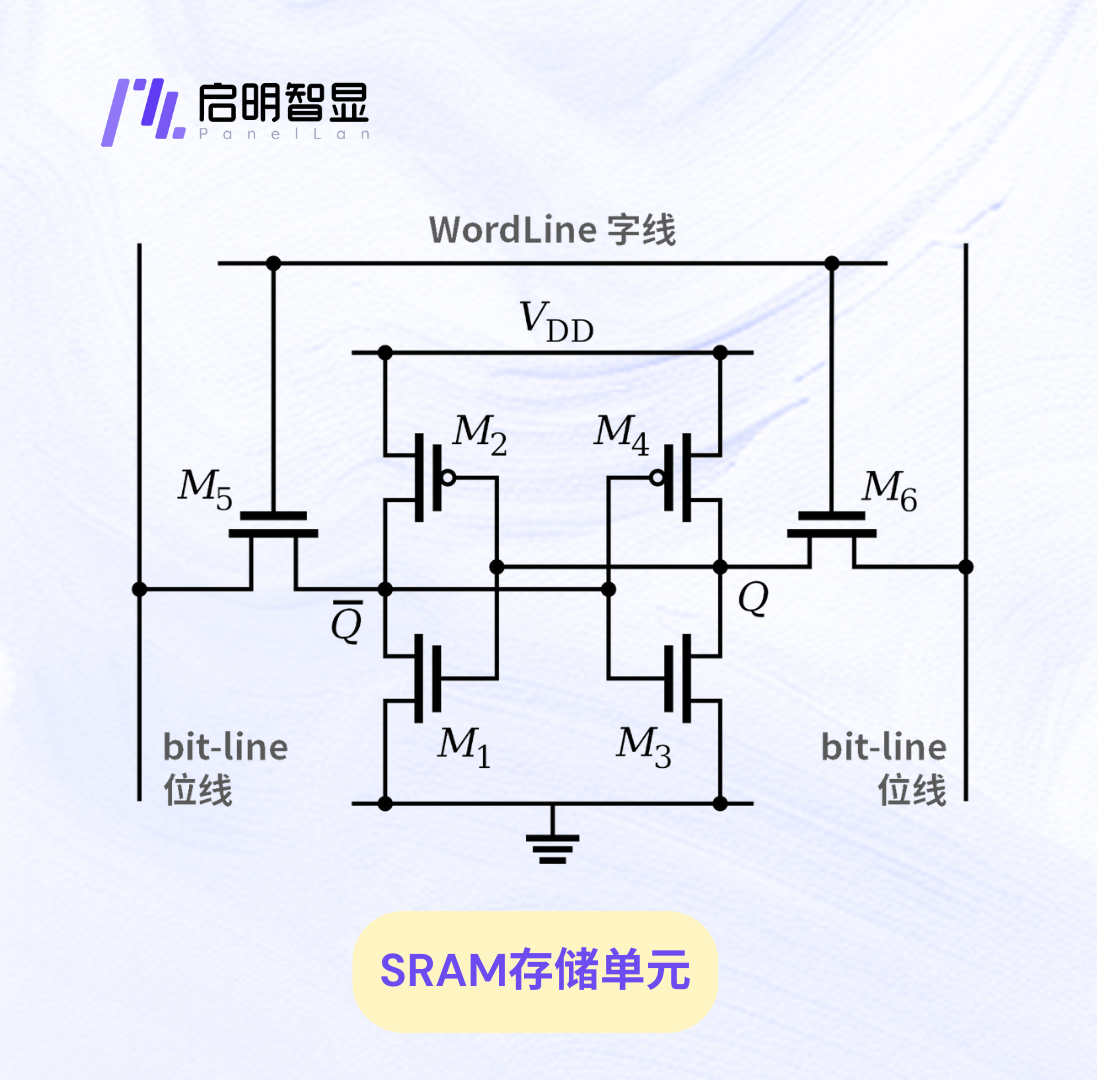

2.SRAM

SRAM是CPU缓存所使用的技术,它的架构相较于DRAM要复杂很多。

SRAM的基本单元,则最少由6管晶体管组成:4个场效应管(M1, M2, M3, M4)构成两个交叉耦合的反相器,2个场效应管(M5, M6)用于读写的位线(Bit Line)的控制开关,通过这些场效应管构成一个锁存器(触发器),并在通电时锁住二进制数0和1。因此,SRAM被称为“静态随机存储器”。

SRAM不需要定期刷新,响应速度非常快,但价格昂贵,用于CPU的一级缓冲、二级缓冲。Model4中也有SRAM,具备96KB的SRAM,用于程序运行时变量、堆栈的暂存等,非常适用于需要大量数据计算的场合。

(二)非易失性存储器(NVM)

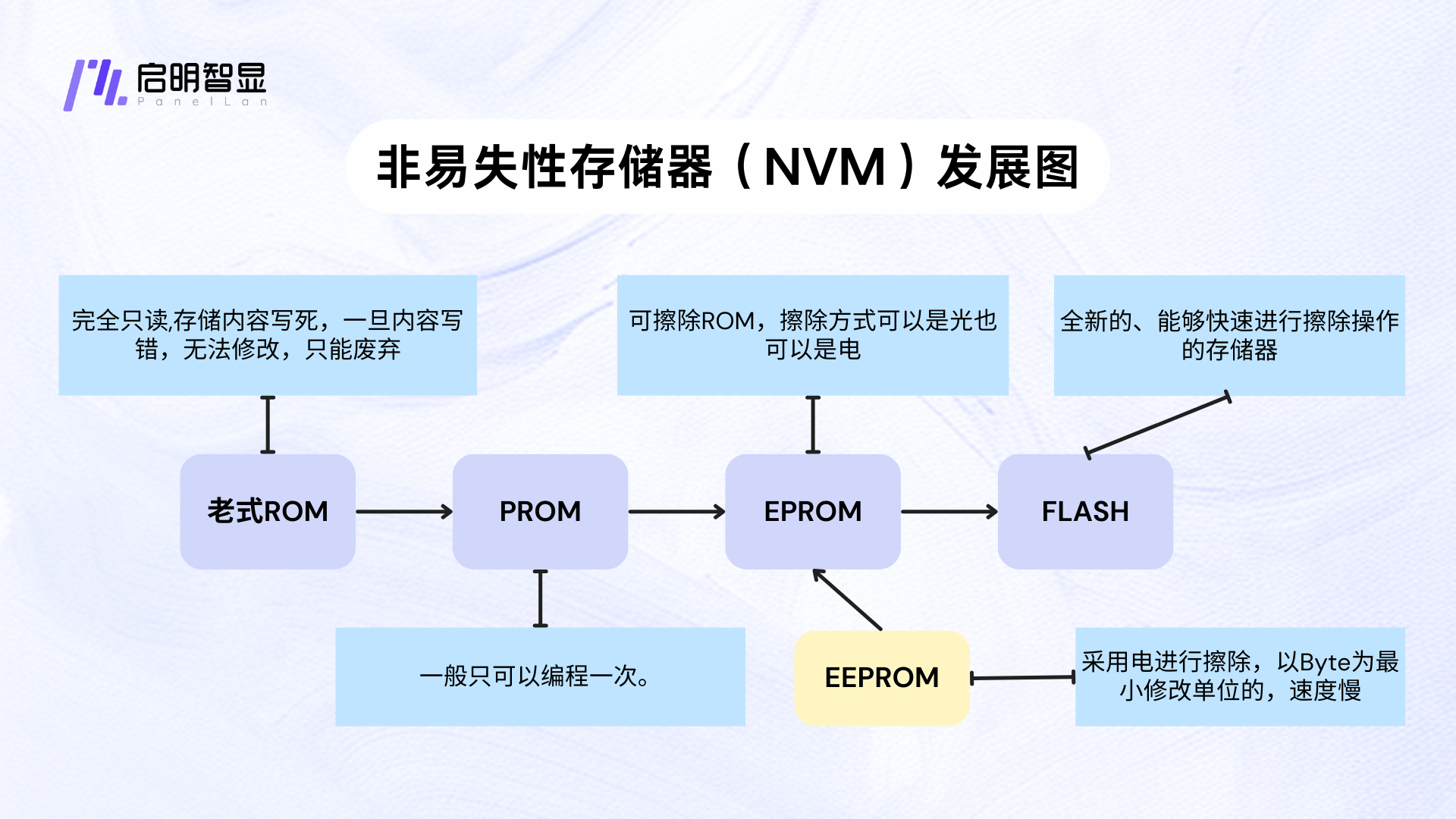

非易失性存储器产品的技术路线比较多,早起NVM的发展可以简要概括为下图:

早期的这些NVM要不就是无法修改,要不就是修改方式都太慢。直到上世纪80年代,日本东芝的技术专家——舛冈富士雄,发明了一种全新的、能够快速进行擦除操作的存储器,也就是——Flash(闪存)。

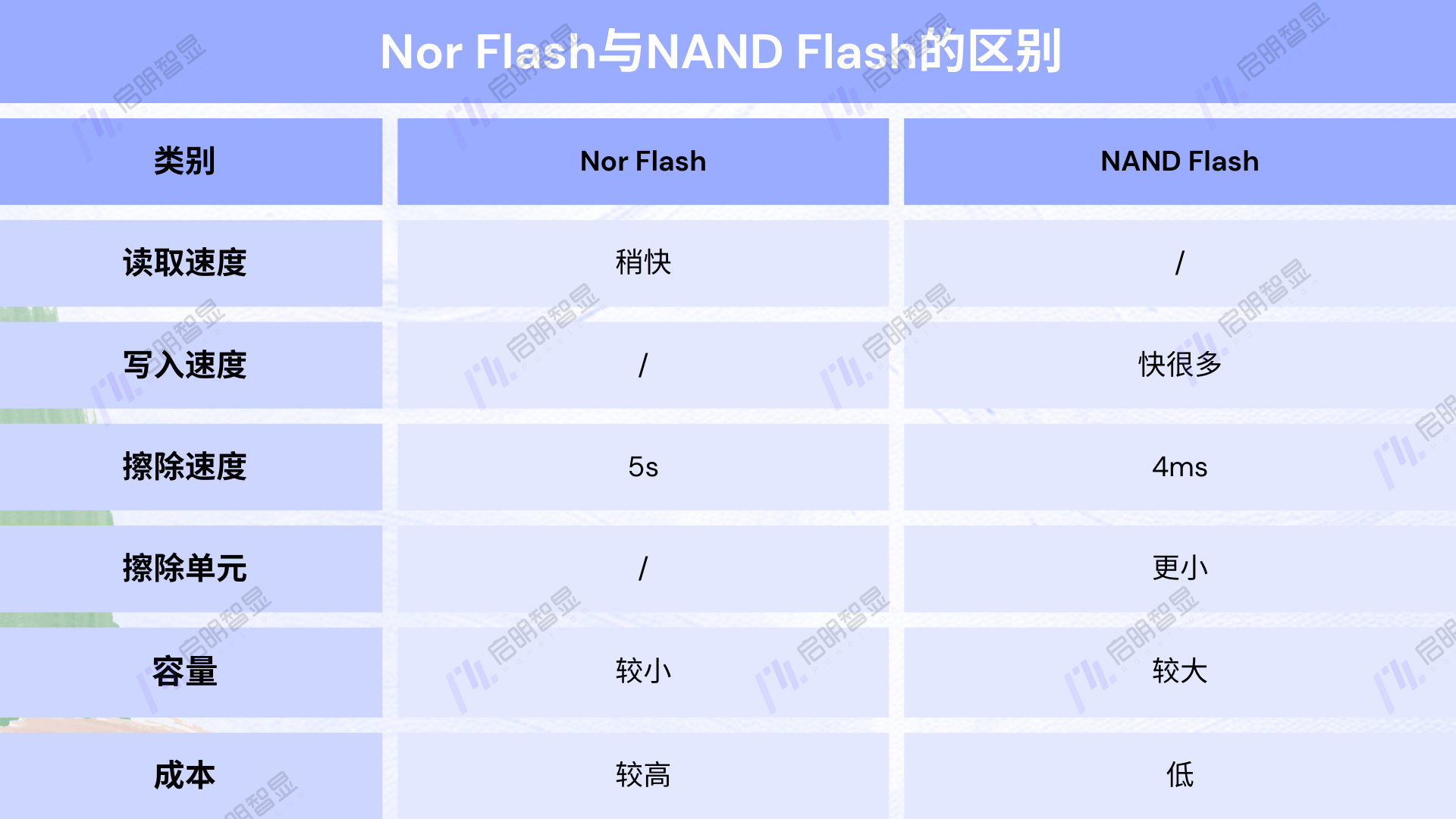

Flash存储是以“块”为单位进行擦除的。常见的块大小为128KB和256KB。1KB是1024个bit,比起EEPROM按bit擦除,快了几个数量级。目前,FLASH的主流代表产品也只有两个,即:NOR Flash和NAND Flash。

1. NOR Flash

NOR Flash属于代码型闪存芯片,其主要特点是芯片内执行(XIP,ExecuteIn Place),即应用程序不必再把代码读到系统RAM中,而是可以直接在Flash闪存内运行。

所以,NOR Flash适合用来存储代码及部分数据,可靠性高、读取速度快,在中低容量应用时具备性能和成本上的优势。

但是,NOR Flash的写入和擦除速度很慢,而且体积是NAND Flash的两倍,所以用途受到了很多限制,市场占比比较低。

近年来,NOR Flash的应用有所回升,市场回暖。低功耗蓝牙模块、TWS耳机、手机触控和指纹、可穿戴设备、汽车电子和工业控制等领域,使用NOR Flash比较多。

2. NAND Flash

NAND Flash属于数据型闪存芯片,可以实现大容量存储。它基于浮栅晶体管设计,通过浮栅来锁存电荷,由于浮栅是电隔离的,所以即使在去除电压之后,到达栅极的电子也会被捕获。这就是闪存非易失性的原理所在。数据存储在这类设备中,即使断电也不会丢失。

NAND Flash以页为单位读写数据,以块为单位擦除数据,故其写入和擦除速度虽比DRAM大约慢3-4个数量级,却也比传统的机械硬盘快3个数量级,被广泛用于eMMC/EMCP、U盘、SSD等市场。

相对于机械硬盘等传统存储介质,采用NAND Flash 芯片的SD 卡、固态硬盘等存储装置没有机械结构,无噪音、寿命长、功耗低、可靠性高、体积小、读写速度快、工作温度范围广,是未来大容量存储的发展方向。随着大数据时代的到来,NAND Flash 芯片将在未来得到巨大发展。

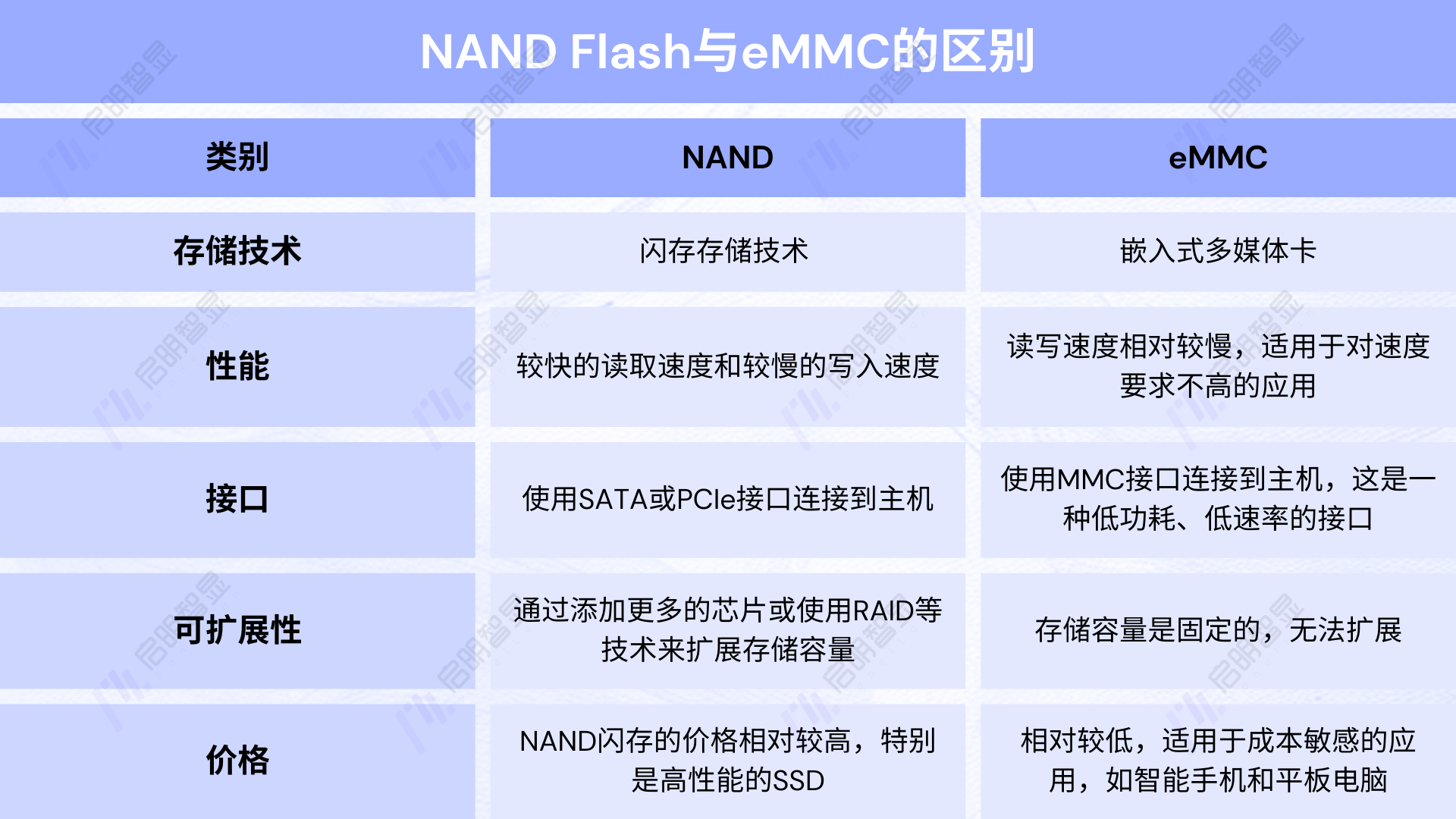

3. Nor Flash与NAND Flash的区别

二、eMMC与UFS

(一)eMMC

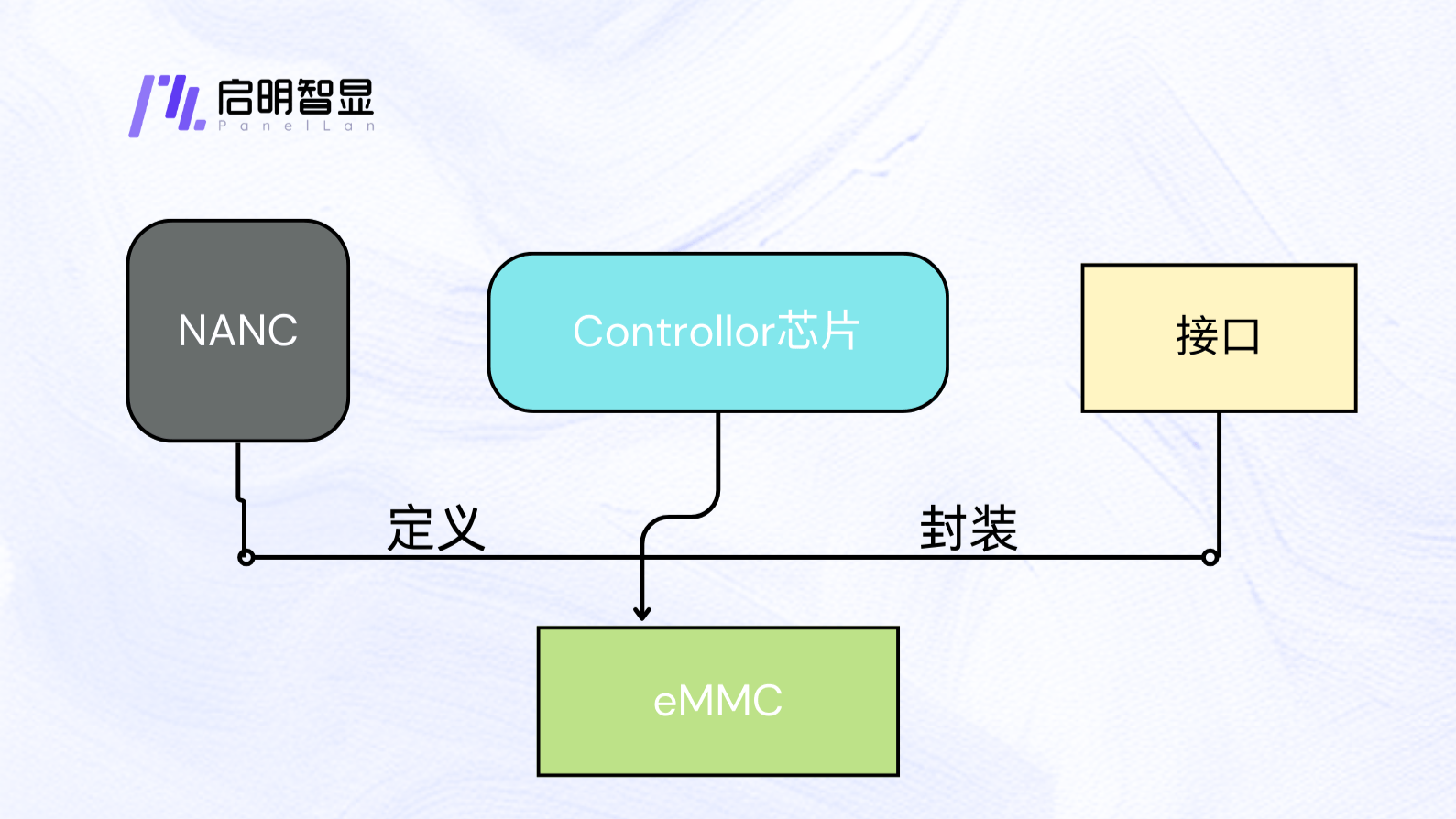

eMMC ( Embedded Multi Media Card) 采用统一的MMC标准接口, 把高密度NAND Flash以及MMC Controller封装在一颗BGA芯片中。针对Flash的特性,产品内部已经包含了Flash管理技术,包括错误探测和纠正,flash平均擦写,坏块管理,掉电保护等技术。用户无需担心产品内部flash晶圆制程和工艺的变化。同时eMMC单颗芯片为主板内部节省更多的空间。

简单地说,eMMC=Nand Flash+控制器+标准封装。

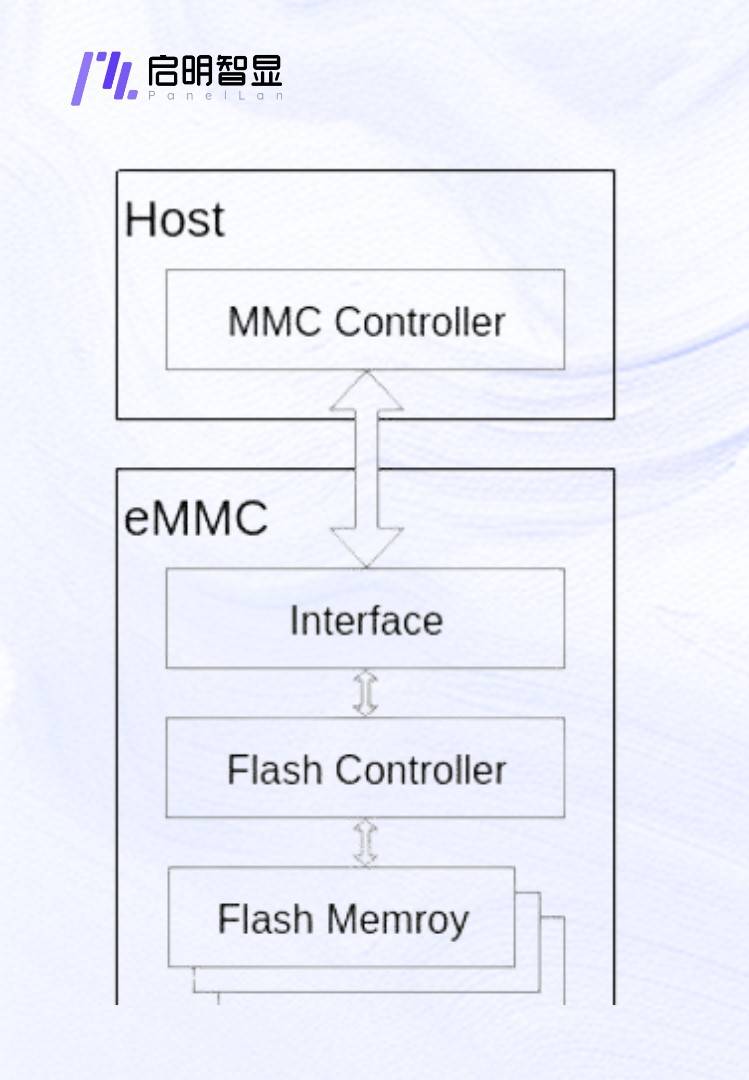

eMMC的整体架构如下图片所示:

eMMC 则在其内部集成了 Flash Controller,用于完成擦写均衡、坏块理、ECC校验等功能,让 Host 端专注于上层业务,省去对 NAND Flash 进行特殊的处理。

eMMC具有以下优势:

1.简化类手机产品存储器的设计。

2.更新速度快。

3.加速产品研发速度。

它与NAND Flash有何区别?

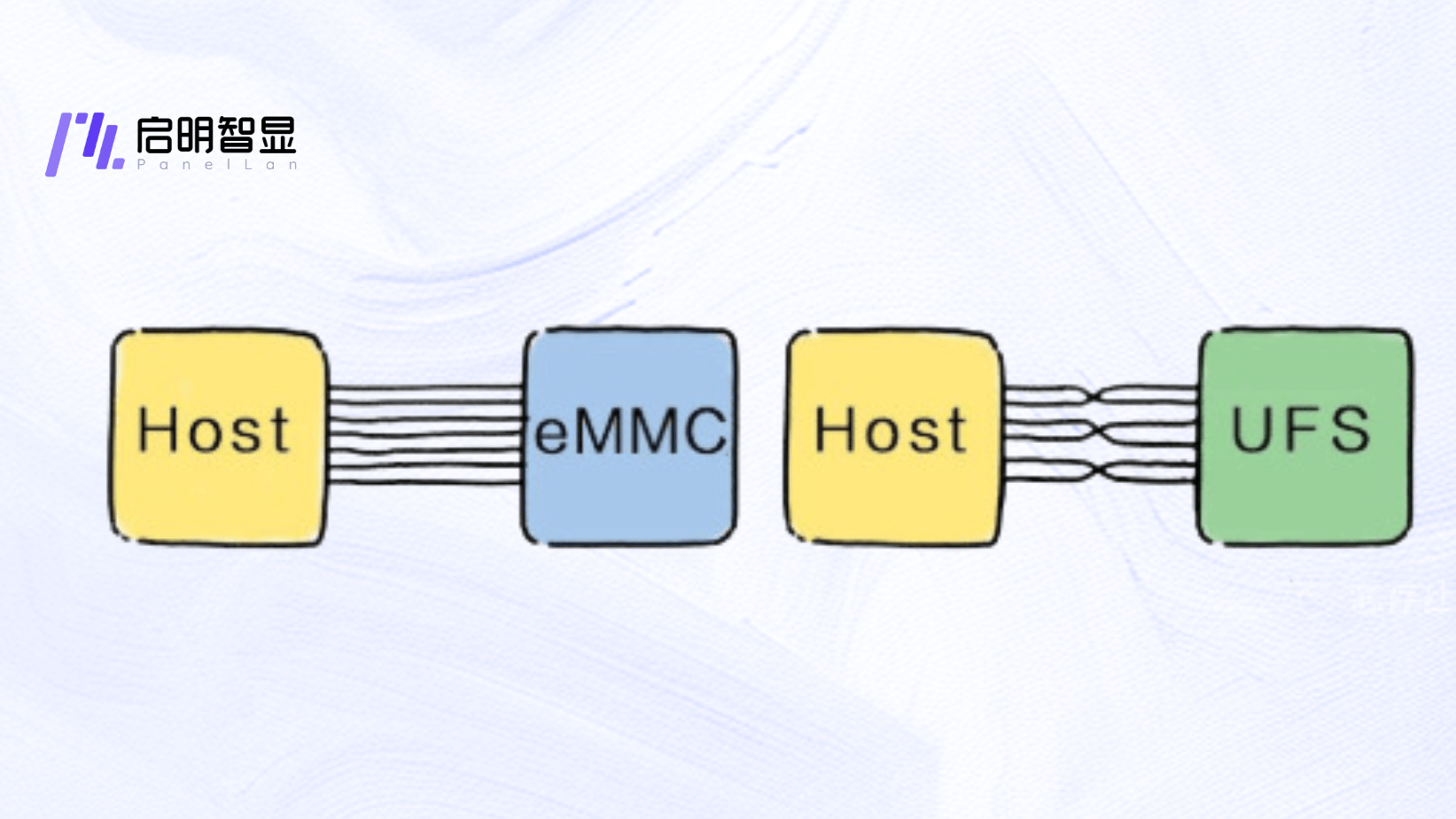

(二)UFS

UFS:Univeral Flash Storage,我们可以将它视为eMMC的进阶版,是由多个闪存芯片、主控、缓存组成的阵列式存储模块。UFS弥补了eMMC仅支持半双工运行(读写必须分开执行)的缺陷,可以实现全双工运行,所以性能得以翻番。

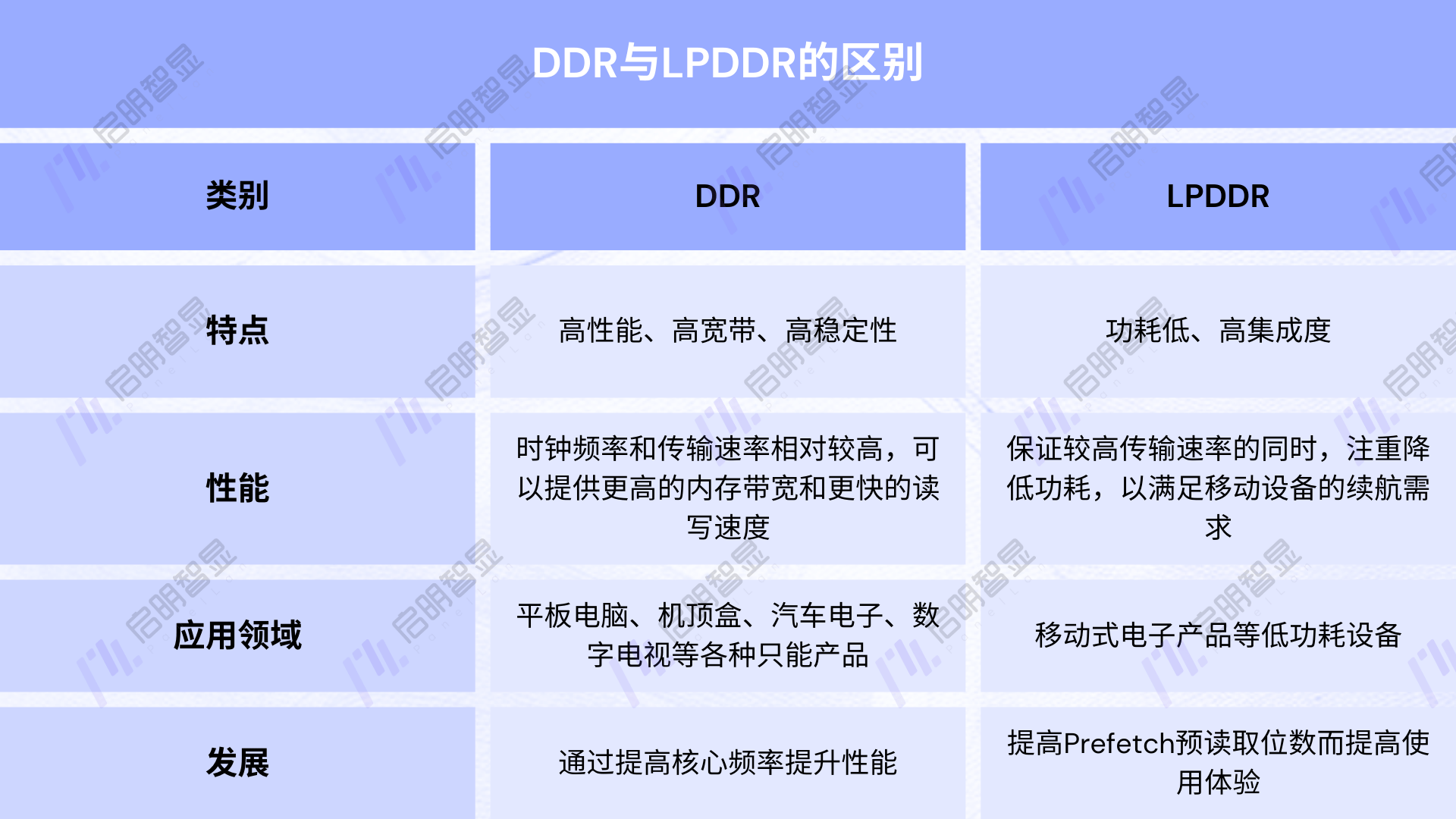

三、DDR、LPDDR

DDR全称Double Data Rate双倍速率同步动态随机存储器,严格的来讲,DDR应该叫DDR SDRAM。虽然美国固态技术协会2018年宣布正式发布DDR5标准,但实际上最终的规范要到2020年才能完成,其目标是将内存带宽在DDR4基础上翻倍,速率3200MT/s起,最高可达6400MT/s,电压则从1.2V降至1.1V,功耗减少30%。

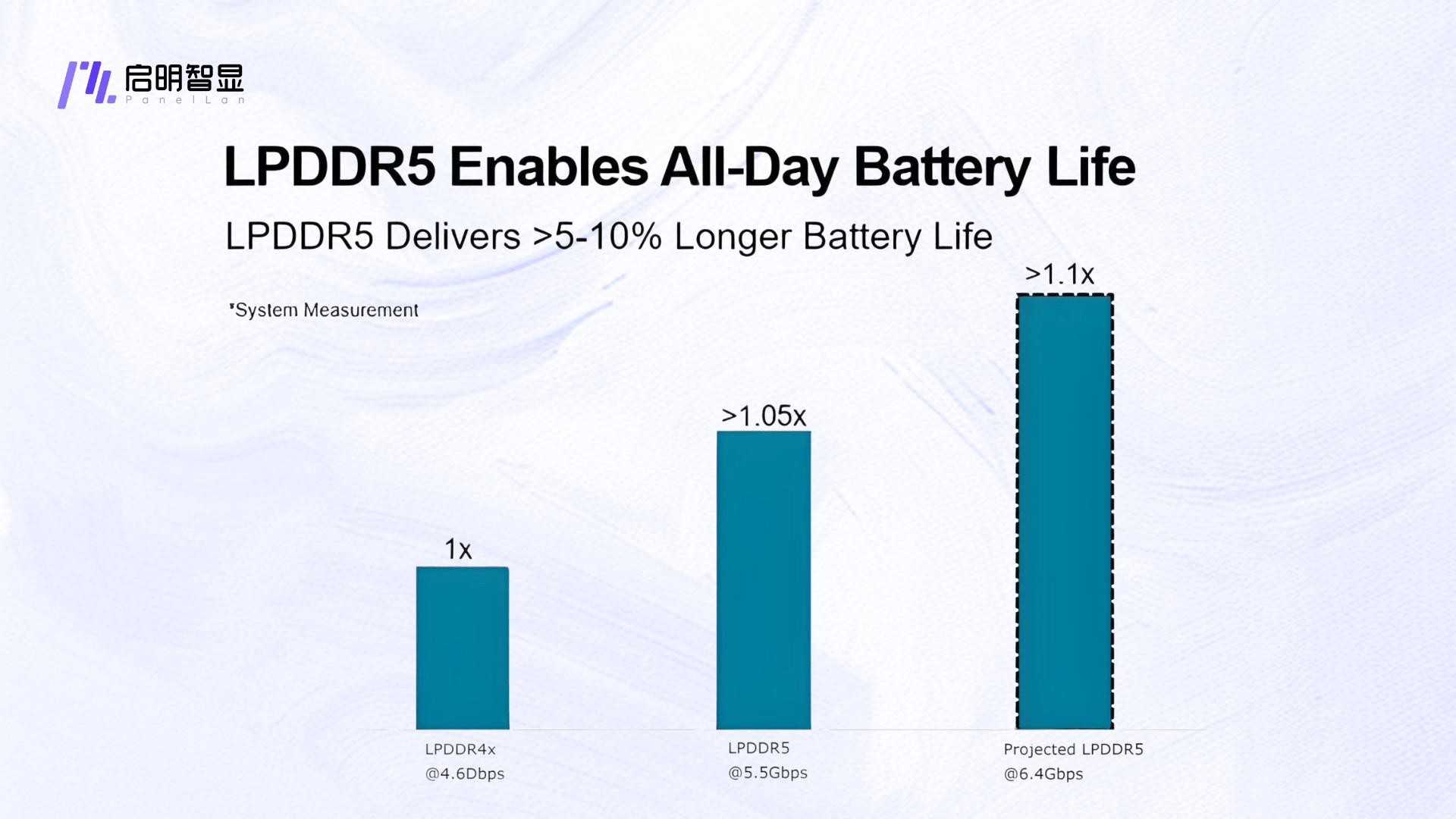

LPDDR是在DDR的基础上多了LP(Low Power)前缀,全称是Low Power Double Data Rate SDRAM,简称“低功耗内存”是DDR的一种,以低功耗和小体积著称。目前最新的标准LPDDR5被称为5G时代的标配,但目前市场上的主流依然是LPDDR3/4X。

DDR与LPDDR的区别:

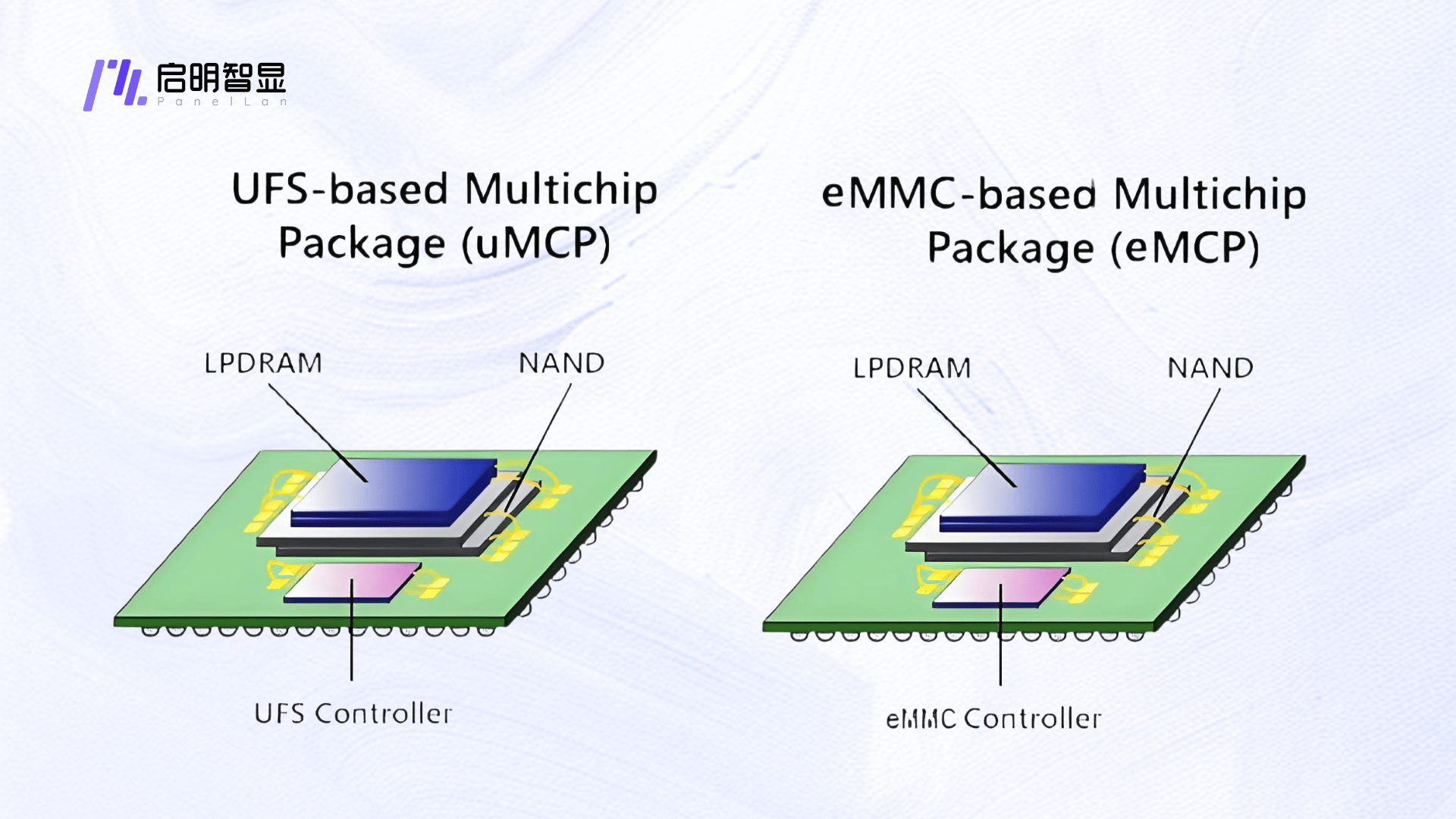

四、eMCP与uMCP

eMCP是结合eMMC和LPDDR封装而成的智慧型手机记忆体标准,与传统的MCP相较之下,eMCP因为有内建的NAND Flash控制晶片,可以减少主晶片运算的负担,并且管理更大容量的快闪记忆体。以外型设计来看,不论是eMCP或是eMMC内嵌式记忆体设计概念,都是为了让智慧型手机的外型厚度更薄,更省空间。

uMCP是结合了UFS和LPDDR封装而成的智慧型手机记忆体标准,与eMCP相比,国产的uMCP在性能上更为突出,提供了更高的性能和功率节省。

总结

综上,我们能看到内存和存储器不断地向着低功耗、高性能发展,也理解了各个内存、存储器的特点与优势。从而我们也能得出一个结论:Model4芯片充分融合了高性能内存、存储以及存储接口,结合高响应速度的96KB的SRAM以及64MB DDR2存储,支持接入NAND Flash 和Nor Flash,支持eMMC5.0接口,具备高性能、高稳定性的特点。

- 芯片

+关注

关注

450文章

49379浏览量

415880 - 存储器

+关注

关注

38文章

7321浏览量

162912 - 内存

+关注

关注

8文章

2861浏览量

73391

发布评论请先登录

相关推荐

半导体存储器科普|从内存、存储器看国产工业级HMI芯片Model4性能

半导体存储器科普|从内存、存储器看国产工业级HMI芯片Model4性能

评论