CMOS(互补金属氧化物半导体)和TTL(晶体管-晶体管逻辑)是两种广泛应用于数字电路设计中的逻辑门技术。它们在性能、功耗、速度、成本和抗干扰能力等方面存在显著差异。

- CMOS技术概述

CMOS技术是一种使用互补型金属氧化物半导体场效应晶体管(MOSFET)的数字逻辑技术。CMOS逻辑门由n型和p型MOSFET组成,它们在逻辑门的输入端形成互补结构。CMOS技术具有以下特点:

1.1 低功耗:CMOS逻辑门在静态状态下几乎不消耗功率,只有在输入信号变化时才消耗少量功率。这使得CMOS技术在低功耗应用中具有优势。

1.2 高集成度:CMOS技术可以实现高密度的集成电路设计,使得单个芯片上可以集成更多的逻辑门。

1.3 抗干扰能力:CMOS逻辑门具有较高的噪声容限,可以在一定程度上抵抗外部干扰。

1.4 速度:CMOS逻辑门的速度受到晶体管尺寸和电源电压的限制,通常比TTL逻辑门慢。

- TTL技术概述

TTL技术是一种使用双极型晶体管(BJT)的数字逻辑技术。TTL逻辑门由NPN和PNP晶体管组成,它们在逻辑门的输入端形成互补结构。TTL技术具有以下特点:

2.1 高速度:TTL逻辑门的开关速度较快,适用于高速数字电路设计。

2.2 功耗:TTL逻辑门在静态状态下消耗一定的功率,这使得其在低功耗应用中的性能不如CMOS技术。

2.3 抗干扰能力:TTL逻辑门的噪声容限较低,对外部干扰较为敏感。

2.4 成本:TTL逻辑门的制造成本相对较低,适用于成本敏感的应用场景。

- CMOS和TTL的抗干扰能力比较

3.1 噪声容限

CMOS逻辑门具有较高的噪声容限,通常在0.7V至1.2V之间。这意味着CMOS逻辑门可以在一定程度上抵抗外部干扰,如电源波动、电磁干扰等。相比之下,TTL逻辑门的噪声容限较低,通常在0.4V左右,对外部干扰较为敏感。

3.2 电源波动

CMOS逻辑门对电源波动的抗干扰能力较强。由于CMOS逻辑门在静态状态下几乎不消耗功率,因此电源波动对其影响较小。而TTL逻辑门在静态状态下消耗一定的功率,电源波动可能导致其输出不稳定。

3.3 电磁干扰

CMOS逻辑门对电磁干扰的抗干扰能力较强。CMOS逻辑门的输入端由互补型MOSFET组成,其输入阻抗较高,对电磁干扰的敏感度较低。而TTL逻辑门的输入端由双极型晶体管组成,其输入阻抗较低,对电磁干扰的敏感度较高。

3.4 温度影响

CMOS逻辑门对温度变化的抗干扰能力较强。CMOS逻辑门的阈值电压与温度变化关系较小,因此温度变化对其性能影响较小。而TTL逻辑门的阈值电压与温度变化关系较大,温度变化可能导致其输出不稳定。

- CMOS和TTL在不同应用场景下的抗干扰能力

4.1 低功耗应用

在低功耗应用中,CMOS技术具有明显优势。由于CMOS逻辑门在静态状态下几乎不消耗功率,因此在低功耗应用中具有较高的抗干扰能力。而TTL逻辑门在静态状态下消耗一定的功率,其抗干扰能力相对较弱。

4.2 高速数字电路设计

在高速数字电路设计中,TTL技术具有优势。TTL逻辑门的开关速度较快,适用于高速数字电路设计。然而,由于TTL逻辑门的噪声容限较低,因此在高速应用中可能需要采取额外的抗干扰措施。

4.3 成本敏感应用

在成本敏感的应用场景中,TTL技术具有优势。TTL逻辑门的制造成本相对较低,适用于成本敏感的应用场景。然而,由于TTL逻辑门的抗干扰能力较弱,可能需要在设计中考虑额外的抗干扰措施。

- 结论

综上所述,CMOS和TTL技术在抗干扰能力方面存在显著差异。CMOS技术具有较高的噪声容限、对电源波动和电磁干扰的抗干扰能力较强,以及对温度变化的抗干扰能力较强。然而,CMOS逻辑门的速度受到晶体管尺寸和电源电压的限制,通常比TTL逻辑门慢。相比之下,TTL逻辑门的开关速度较快,但在抗干扰能力方面相对较弱。

-

CMOS

+关注

关注

58文章

5710浏览量

235407 -

TTL

+关注

关注

7文章

503浏览量

70231 -

晶体管

+关注

关注

77文章

9682浏览量

138079 -

逻辑技术

+关注

关注

0文章

3浏览量

5726

发布评论请先 登录

相关推荐

电动工具直流调速专用集成电路GS069,具有电源电压范围宽、功耗小、抗干扰能力强等特性

如何提升无线模块的抗干扰能力

VK1S68C是带键盘扫描接口的点阵LED驱动控制专用芯片适用于要求可靠/稳定/抗干扰能力强的产品。

M451系列的抗干扰能力比M481几乎强吗?

LoRa模块的抗干扰能力怎样

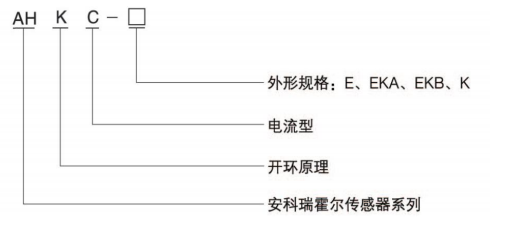

AHKC-EKBDA霍尔传感器 响应快精度高 抗干扰能力强

cmos和ttl哪个抗干扰能力强

cmos和ttl哪个抗干扰能力强

评论