SR锁存器是一种基本的数字逻辑电路,用于存储一位二进制信息。它由两个触发器(Set和Reset)组成,分别控制输出Q和Q非。在这篇文章中,我们将探讨SR锁存器的Q非和Q*之间的关系,以及它们在数字电路设计中的应用。

- SR锁存器的基本概念

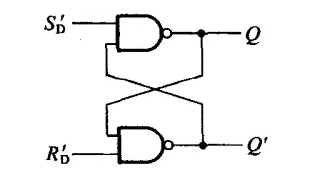

SR锁存器是一种具有两个输入(Set和Reset)和两个输出(Q和Q非)的存储单元。其中,Set输入用于将Q置为高电平,Reset输入用于将Q置为低电平。Q非是Q的反相输出,即当Q为高电平时,Q非为低电平;当Q为低电平时,Q非为高电平。

- SR锁存器的工作原理

SR锁存器的工作原理可以通过以下步骤来理解:

2.1. 当Set输入为高电平时,触发器将Q置为高电平,Q非置为低电平。此时,SR锁存器存储了一位二进制信息“1”。

2.2. 当Reset输入为高电平时,触发器将Q置为低电平,Q非置为高电平。此时,SR锁存器存储了一位二进制信息“0”。

2.3. 当Set和Reset输入都为低电平时,触发器保持当前的Q和Q非状态不变。这意味着SR锁存器可以保持其存储的信息。

- Q非和Q*的关系

Q非是Q的反相输出,而Q是Q的互补输出。在SR锁存器中,Q非和Q具有以下关系:

3.1. 当Q为高电平时,Q非为低电平,Q*也为低电平。

3.2. 当Q为低电平时,Q非为高电平,Q*也为高电平。

3.3. 当Q保持不变时,Q非和Q*的状态也保持不变。

- SR锁存器的应用

SR锁存器在数字电路设计中有广泛的应用,以下是一些常见的应用场景:

4.1. 数据存储:SR锁存器可以用于存储一位二进制数据,例如在寄存器、计数器等电路中。

4.2. 信号同步:在数字系统中,信号可能在不同的时钟域中传输。使用SR锁存器可以实现信号的同步,确保数据在正确的时钟周期内被读取。

4.3. 状态机设计:在有限状态机(FSM)设计中,SR锁存器可以用于实现状态的存储和转换。

4.4. 寄存器设计:在寄存器设计中,SR锁存器可以用于实现寄存器的读写控制。

- SR锁存器的优缺点

5.1. 优点:

5.1.1. 结构简单:SR锁存器由两个触发器组成,结构简单,易于实现。

5.1.2. 存储能力强:SR锁存器可以存储一位二进制信息,对于简单的存储需求足够使用。

5.1.3. 应用广泛:SR锁存器在数字电路设计中有广泛的应用,如数据存储、信号同步等。

5.2. 缺点:

5.2.1. 存储容量有限:SR锁存器只能存储一位二进制信息,对于需要存储大量数据的应用场景,可能不够使用。

5.2.2. 易受干扰:由于SR锁存器的Set和Reset输入是独立的,当它们同时为高电平时,可能导致锁存器进入不确定状态,从而影响数据的稳定性。

5.2.3. 功耗较高:由于SR锁存器需要两个触发器,其功耗相对于其他存储单元(如D触发器)可能较高。

- 结论

SR锁存器是一种基本的数字逻辑电路,具有结构简单、应用广泛的特点。Q非和Q*是SR锁存器的两个重要输出,它们之间的关系是互补的。虽然SR锁存器在存储容量和抗干扰能力方面存在一定的局限性,但在许多应用场景中,它仍然是一种有效的解决方案。

-

二进制

+关注

关注

2文章

795浏览量

41643 -

触发器

+关注

关注

14文章

2000浏览量

61130 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15812

发布评论请先 登录

相关推荐

SR锁存器的Q非和Q*是什么关系

SR锁存器的Q非和Q*是什么关系

评论