在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。第1步:验证通信第一步是验证PLL响应编程的能力。如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。一种方法是通过软件(而非引脚)调节PLL的通电断电寻找引脚的可预测电流变化或偏置电压电平变化。许多PLL在其输入(OSCin)引脚的电平在通电时为Vcc/2,在断电时为0V。如果PLL集成了压控振荡器(VCO),则查看低压差(LDO)输出引脚电压是否对通电和断电命令做出反应。还可能可以切换输入/输出 (I/O)引脚,比如许多LMX系列PLL的MUXout引脚。如果采用上述方法能够验证通信,就可以继续尝试进行锁定。如果无法验证通信,则查找常见的原因,例如以下原因:

-

编程串行

-

锁存使能(也称为芯片选择条(CSB))过高

-

对软件输入的低通滤波过多

-

与串行外围设备接口总线(SPI)存在时序问题

-

电源引脚焊接有误

第2步:建立锁定验证通信后,下一步就是尝试对PLL进行锁定。下面是PLL无法锁定的一些更常见的原因:

如果配置有误,锁定检测引脚会在实际已经锁定的情况下显示出PLL未锁定。可以通过查看频谱分析仪输出或VCO调谐电压验证这一情况。

向PLL发送错误的信息会很容易导致无法锁定。一些常见的编程错误包括:VCO编程频率超出范围、VCO校准设置不正确或寄存器时序有误。

对于集成VCO的PLL而言,频率范围通常分成几个不同的频段。错误的编程会导致VCO锁定错误的频段。对特定寄存器的编程通常会启动VCO校准;因此必须确定在编程此寄存器时,其他软件和硬件(尤其是基准输入)状态正确,以确保校准正常工作。

如果VCO输入或基准输入因电源水平较低、压摆率较低、匹配较差或谐波较高而存在问题,会导致PLL打开锁定。大多数PLL有方法输出内部频率计数器的实际频率输出,将其发送到引脚。

可以通过查看调谐电压或切换鉴相器两极,根据频率变化确定连接或短路。

如果降低电荷泵电流导致PLL锁定通常是不稳定的表现,但是仅凭这项技术不起作用不能排除不稳定这一因素。导致环路滤波器不稳定的产检原因有忽略考虑VCO输入电容;使用过度限制环路带宽的集成滤波器;或者使用与PLL初始设计不同的PLL设置(电荷泵增益、VCO频率或鉴相器频率)。

遵循系统的方法,不作出草率的假设能够使PLL锁定调试程序变得简单许多。下图为指导此程序的流程图。

图:PLL调试流程图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:锁相环无法锁定,应该这样处理…

文章出处:【微信号:eet-china,微信公众号:电子工程专辑】欢迎添加关注!文章转载请注明出处。

相关推荐

锁相环(PLL)是一种反馈控制系统,用于锁定输入信号的相位和频率。它在现代电子系统中扮演着至关重要的角色,从无线通信到数字信号处理,PLL的应用无处不在。然而,由于其复杂性,PLL也可能出现各种故障

![的头像]() 发表于

发表于 11-06 10:52

•551次阅读

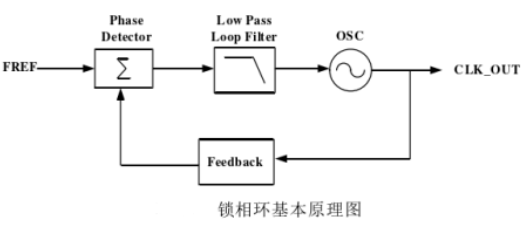

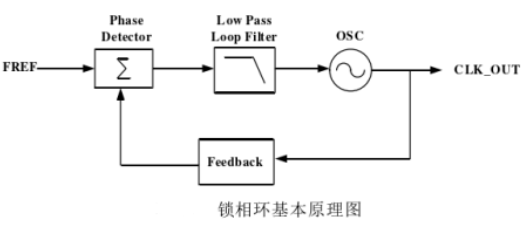

、锁相环(PLL)的基本原理 锁相环是一种电子电路,能够锁定到输入信号的相位,并产生一个与输入信号频率和相位一致的输出信号。PLL由三个主要部分组成:相位检测器(PD)、环路滤波器(LF)和压控振荡器(VCO)。 相位检测器(P

![的头像]() 发表于

发表于 11-06 10:46

•313次阅读

锁相环(Phase-Locked Loop, PLL)和锁相放大器(Lock-in Amplifier)是两种在电子学和信号处理领域广泛应用的技术,它们各自具有独特的工作原理、组成结构以及应用场景。以下将从定义、组成、工作原理、性能特点及应用领域等方面详细阐述

![的头像]() 发表于

发表于 07-30 15:51

•1217次阅读

锁相环(Phase Locked Loop, PLL)相位噪声是评估锁相环性能的重要指标之一,它描述了输出信号相位的不稳定性。相位噪声的存在会直接影响系统的性能,如降低信号的信噪比、增加误码率、影响雷达系统的目标分辨能力等。以下将详细分析

![的头像]() 发表于

发表于 07-30 15:31

•1319次阅读

我在配置AD9694的过程中发现AD9694的采样率对应的线速率只有在6.75Gbps-13.5Gbps之间时,204b接口的锁相环才能锁定,现在想配置200M采样率,但是204B接口的锁相环无法

发表于 07-03 06:18

我在配置AD9694的过程中遇到了AD9694输入时钟低于337.5MHz时,内部的serdes锁相环无法锁定的问题;但输入时钟高于337.5MHz时,如400M、600M就能锁定;0x56e寄存器

发表于 06-21 14:27

基本锁相环通常由锁相检测器(Phase Detector)、低通滤波器(Loop Filter)和令牌圈振荡器(VCO)组成。它是最简单的锁相环形式,用于频率和相位同步。

![的头像]() 发表于

发表于 01-31 16:00

•1777次阅读

锁相环是保证相位一致,还是相位差一致?锁相环的输入输出相位一致吗? 锁相环(PLL)是一种回路控制系统,用于保持输出信号的相位与参考信号的相位之间的恒定关系。简单来说,锁相环的目的是保

![的头像]() 发表于

发表于 01-31 15:45

•1138次阅读

锁相环锁定后一定不存在频差吗? 锁相环是一种常用的控制系统,用于将输入信号与参考信号之间的相位误差维持在一个可接受的范围内。它通过调节输出信号的相位和频率来实现这个目标。然而,

![的头像]() 发表于

发表于 01-31 15:25

•828次阅读

锁相环到底锁相还是锁频? 锁相环(PLL)是一种常用的控制系统,主要用于同步时钟。它通过将被控信号的相位与稳定的参考信号进行比较,并产生相应的控制信号,使被控信号的相位保持与参考信号同

![的头像]() 发表于

发表于 01-31 15:25

•1948次阅读

锁相环路(PLL)。锁相环是一种控制系统,它可以将一个信号锁定到参考频率上,保持相位一致。它由一个相位检测器、一个低通滤波器、一个压控振荡器和一个分频器组成。 锁相环首先将输入信号与参

![的头像]() 发表于

发表于 01-31 15:24

•1134次阅读

锁频环为什么锁定后又发生失锁现象? 锁频环是一种非常重要的电子电路,常见于通信设备、数字信号处理、时钟恢复和频率合成等领域。锁频环的作用是将输入信号与输出信号的频率

![的头像]() 发表于

发表于 01-31 11:31

•1182次阅读

,也称为追踪带。它的主要功能是锁定输入信号与VCO(电压控制振荡器)输出信号的相位,使输出信号与输入信号保持相位一致。 - 锁相环捕获带:捕获带是锁相环的另一种工作模式,也称为拉住带。它的主要功能是在输入信号发生较大偏差时,将输

![的头像]() 发表于

发表于 01-31 11:31

•1389次阅读

环路的跟踪状态是指锁相环锁定后的状态,即环路中的压控振荡器(VCO)的输出信号的相位能够自动跟踪输入信号的相位,从而保持恒定的稳态相位差。

![的头像]() 发表于

发表于 01-30 14:18

•1120次阅读

本人在使用ADF4372芯片时,运用RF16输出口,锁相环正常锁定,但是输出幅度只有-28dbm,这是为什么,请求解答谢谢。没有在VDDX1加7.4nH电感。

发表于 01-03 07:39

用验证通行与建立锁定的程序来进行锁相环锁定

用验证通行与建立锁定的程序来进行锁相环锁定

评论