周立功教授新书《面向AMetal框架与接口的编程(上)》,对AMetal框架进行了详细介绍,通过阅读这本书,你可以学到高度复用的软件设计原则和面向接口编程的开发思想,聚焦自己的“核心域”,改变自己的编程思维,实现企业和个人的共同进步。经周立功教授授权,即日起,致远电子公众号将对该书内容进行连载,愿共勉之。

第二章为ADC 信号调理电路设计,本文为 2.1 应用背景和2.2 电路设计。

本章导读:

对于开发者来说,最难的是vwin 电路的设计。不仅需要投入大量的仪器设备,而且还需要理论水平很高且实践经验很丰富的指导老师,才有可能设计出符合要求的模拟电路。通过分析用户设计的模拟电路,发现大多数开发者对模拟电路的设计细节知之甚少。

虽然很多半导体公司提供了琳琅满目的设计参考资料,但介绍到某些关键之处时还是让人感到语焉不详,这就是大部分开发者对模拟电路仍然心有余悸的原因。就拿MCU 供应商来说,其提供的资料更多的是数字电路的设计和基本的软件资料。几乎所有的MCU 供应商都不提供具有一定价值的应用电路设计参考,各个厂商提供的资料可以说千篇一律,你想要的没有。其实这些知识对于开发者来说都属于非核心域知识,却要花费很多时间投入其中。

基于此,我们对MCU 内部提供的各种各样的ADC 所需的外围电路进行了标准化的设计,期望推动整个行业的设计水平。因为无论任何需求都存在共性和差异性,所以只要掌握正确设计方法,就能够达到举一反三的效果。

2.1 应用背景

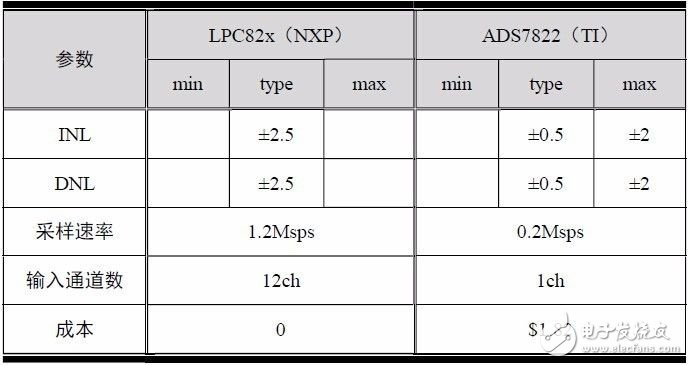

>>> 2.1.1 标称精度

LPC824 内部有一个12 位SAR 型ADC,多达12 个输入通道以及多个内部和外部触发器输入,其采样率高达1.2MS/s。与独立12 位ADC 芯片相比,手册标注的关键参数非常接近,理论上可以实现比较好的采集精度,详见表2.1。在实际的应用中,用户测试结果和标称值相差很远,表现出内部ADC 精度差,这是ADC 外部电路设计不合理所造成的。

表2.1 LPC82x 内部ADC 关键参数

>>> 2.1.2 外围电路

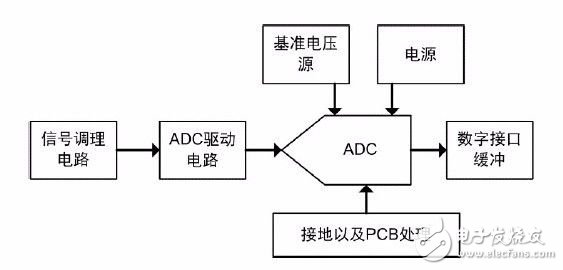

如图2.1 所示使用LPC82x 内部ADC 的采样系统,所需外围支持电路包含基准源、供电电源、驱动电路、信号调理电路等几部分,从原理上看这几部分都影响ADC 的性能指标。

图2.1 内部ADC 所需的外围支持电路

>>> 2.1.3 干扰源

绝大多数MCU 内部集成的ADC 几乎都是逐次逼近(SAR)型,因为它使用开关电容结构,半导体工艺容易实现。由于SAR 型ADC 有多个有效输入端口,因此也容易受到干扰。典型SAR 型ADC 内部结构详见图2.2,分析它的工作原理有助于理解干扰的引入路径。

图2.2 SAR 型ADC 内部结构

它通过两个阶段确定ADC输出码,由于采集阶段开关SW+和SW-最初是关闭的,所有开关均连接到IN+和IN-模拟输入,因此各电容用作采样电容,实现采集输入端的模拟信号。在转换阶段SW+和SW-是打开的,模拟输入与内各部电容断开,电容作用到比较器输入时,将导致比较器不稳定。AR 算法从MSB 开始,切换REF 与REFGND 之间的权电容阵列的各元件,使比较器重新回到平衡状态,由此将产生代表模拟输入的输出数字代码。

转换过程中代表被测输入信号的总电量,在权电容阵列中的各电容两端不断重复分布,每bit 的转换数据都根据与基准源的比较结果产生,从而决定输出代码是0 还是1,基准源上的任何噪声都会对输出代码产生直接影响。如果比较过程中电源端、地回路存在干扰,使得内部比较器的结果变动,同样也会间接导致ADC 输出数据位不稳定,详见图2.3。

图2.3 SAR 型ADC 有多个有效输入端口

SAR 型ADC 这种多次反复比较结构,基准源、电源、地、或数字接口都有可能串入干扰信号,等效于存在多个有效输入端口,而不仅仅只有一个信号输入端。防止外部干扰信号,从ADC 信号输入端以外的引脚耦合进来,才能得到到稳定的数据输出。

2.2 电路设计

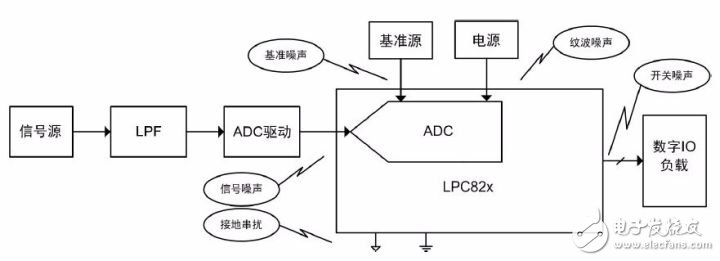

提高内部SAR 型ADC 精度的要点在于逐一排除各有效输入端口上的干扰,详见图2.4。

图2.4 消除ADC 外围支持电路干扰的方法

根据对精度的影响程度,电压基准源电路的设计占80%的工作量,低噪声模拟电源占5%,输入端瞬态驱动占5%,其它抗干扰措施占10%。

>>> 2.2.1 基准源

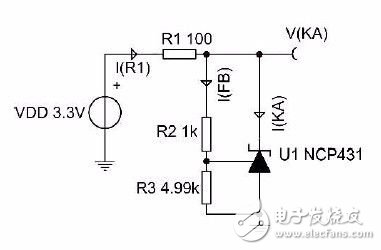

基准电压直接影响ADC 数字输出,要求低噪声、低输出阻抗、温度稳定性良好,标准化电路详见图2.5。

图2.5 低噪声与低输出阻抗基准电压源电路

其中,C2、C1 是内部ADC 参考源管脚的储能电容,R2、R3 用于设定参考源芯片NCP431的输出电压,R1 用于设定NCP431 的静态工作电流,磁珠FB1 与R1 串联,与C2 形成低通滤波器,滤除基准源供电3.3V 上可能存在的高频干扰。

1. 低噪声和低输出阻抗

基准电压源芯片使用低成本NCP431,输出噪声10uVpp,输出阻抗0.2Ω。噪声值用于12 位精度已经足够低,但动态输出阻抗0.2Ω 偏大。利用图2.5 中储能或去耦电容C2、C1的低高频阻抗,提供ADC 转换时基准源管脚上的瞬间高频电流,能非常好地解决基准源高频输出阻抗问题。

需要注意VREF 管脚上的10uF电容C2 不是旁路电容,而是SAR型ADC 的一部分,这个大电容不适合放在硅片上。在位判断期间,由于各输出位会在数十纳秒或更快的时间内建立,因此该储能电容是用来补充开关电容阵列的,从而与内部电容阵列上已有电荷一起平衡比较器。此大容值储能电容需要满足ADC 位判断建立时间要求。为了降低它的高频ESR,C2 优先选用X5R 材质贴片陶瓷电容,确保靠近基准源管脚VREFP 放置,并且在接近VREFN 模拟地管脚处接地,详见图2.6。

图2.6 VREF 管脚储能电容与芯片在/不在同一面的放置方法

2. 静态工作电流

NCP431 是并联型基准,原理类似稳压二极管,只能吸收电流,详见图2.7。在提供负载电流时,维持基准源两端电压不变,使流过限流电阻R1 的总电流不变,调节基准源自身的静态电流减小,使得负载上的电流增加。需计算R1 取值,保证在最大负载电流情况下,有最够的剩余静态电流。

图2.7 并联型的静态工作电流

NCP431 手册中的最小静态电流I(KA)min 为1mA,NCP431 输出电压调节电阻R2、R3 所吸收电流I(FB)为0.5mA,LPC82x 的REF 管脚所吸收平均电流I(REF),约为100uA,留出裕量取1.5mA。总的静态电流取3mA,算得决定静态工作电流R1 的阻值:

3. 输出电压选择

根据LPC82x 手册,为了获得最佳性能,VREFP 和VREFN 应当选择与VDD 和VSS 相同的电压电平。若VREFP 和VREFN 选择不同于VDD 和VSS 的值,则应当确保电压中间值是相同的:

实际测试发现基准电压设置到3.0V 精度最理想,若再升高至接近LPC82x 的电源电压3.3V,因为接近电源轨,ADC 的INL 实测值开始下降,因此标准电路中使用R2、R3 将NCP431的输出电压调整到此值,计算如下:

4. 温漂与直流精度

温漂和初始直流精度是基准源芯片的固有参数,温漂越低初始精度越高,成本越高,温漂25ppm 以下的基准几乎都已经超过LPC82x 芯片自身成本,详见表2.2。

表2.2 基准电压源参数与成本

综合考虑NCP431 是相对合适的选择,它是ONSemi 对TL431 的改进版本,最大温漂由原92 ppm/℃改进为50 ppm/℃,初始准确度优于0.5%。以25℃为参考温度,在-40℃~+85℃范围内,该温漂值引入的误差约为0.3%,基本符合12 位ADC 采集精度的应用。

需要注意标准化电路中R2、R3 影响NCP431 的温漂,应该选择低温漂系数25ppm以下电阻。如果考虑节省成本或者没有可选电阻,为了不影响基准温漂,使用如图2.8 所示的2.5V 输出电路替代。

图2.8 不使用外部电阻的NCP431 基准源电路

基准电压由3V 下降至2.5V 之后,对LPC82x 内部ADC 的INL 会有轻微影响。

>>> 2.2.2 低噪声模拟电源

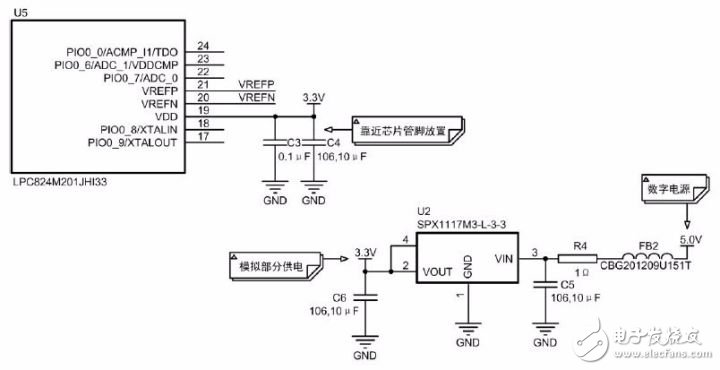

为避免从电源端口串入干扰,需要低噪声的供电电源。利用线性稳压器的纹波抑制比,可以从通常的数字环境开关电源获得此低噪声电源,详见图2.9。

图2.9 低噪声模拟电源电路

使用FB2、R4、C5 所组成的无源滤波网络,可以有效改善1117 在高频段纹波抑制比下降的问题,实现从低频至高频的纹波噪声抑制。其中R3 与C5 形成截止频率1.59KHz 的低通滤波器,使得3.3V 电源上常见的100kHz 以上开关电源纹波干扰衰减10dB 以上。磁珠FB2 在高频时呈现高阻抗,结合C5 在高频时形成更高衰减倍数的低通滤波器,有效滤除3.3V电源上尖峰毛刺噪声。

线性稳压器使用SPX1117,纹波抑制比曲线详见图2.10,在低频至10kHz 频段有接近-60dB 的良好纹波抑制比,100kHz 之后快速下降。

图2.10 SPX1117 的纹波抑制比

线性稳压器U2 应该靠近LPC82x 放置,其他数字电路不共用MCU 的3.3V 电源,如果考虑成本需要共用,数字部分电源单独用LC 滤波电路隔离。

>>> 2.2.3 瞬态驱动

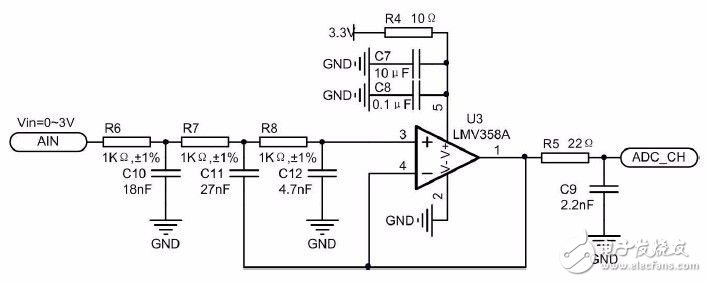

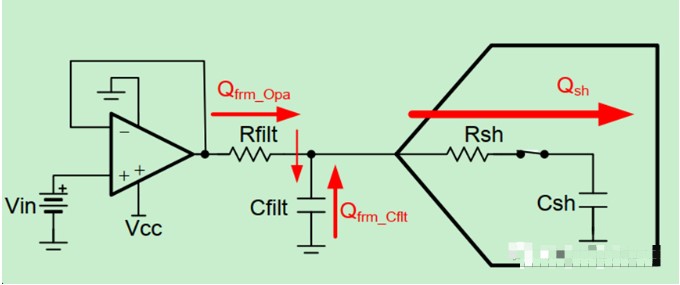

SAR 型ADC 输入端在采样期间具有瞬间充电过程,如果不处理信号源阻抗与内部采样电容的建立时间问题,不管是微处理器中内置的还是外置的ADC,都得不到最好的输出精度。标准化电路中使用运放加RC 组合电路详见图2.11。

图2.11 内部ADC 输入端瞬态驱动电路

通过典型SAR 型ADC 输入端等效电路,有助于理解瞬态驱动电路。如图2.12 所示输入端等效为一个开关S1 连接一个接到地的电容CSH,在电压采样之前,采样电容CSH 通过开关S2 连到电源、电压参考或地进行预充电,预充电电压值由ADC 内部电路决定。电压采样开始时,S2 打开S1 闭合。

图2.12 SAR 型ADC 输入端等效电路

当S1 闭合时,驱动电路从CSH 注入或吸出电荷,而ADC 需要一定的时间来采样信号。在这个采样时间里,ADC 需要从驱动电路汲取足够的电荷量给CSH,使得系统达到1/2-LSB 的精度范围之内。

如果信号源阻抗RO 过大,RO、Rs1RS1、CSH 组成的RC 网络时间常数过大,导致采样时间内CSH 上的电压建立时间不足,采集到的电压值将下降。比较好的解决方法详见图2.12,添加运放缓冲降低信号源内阻,无论信号源阻抗RO 高或者低都不会影响精度。

直接使用运放驱动ADC 输入端时,S1 闭合瞬间的充电电流会干扰运放的输出电压,从而导致ADC 输出结果不准确。为了使设计的电路精度到达更高,应该在运放与ADC 之间添加一个电阻Rin 电容Cin,Cin 是作为一个电荷存储器,在采样瞬间为ADC 的输入端提供足够的电荷,而Rin 用于避免运放驱动容性负载,使得运放工作更加稳定。

>>> 2.2.4 输入信号滤波

输入信号自身可能包含有不期望的干扰信号,在输入电路上添加滤波器抑制干扰,是必要的硬件抗干扰措施。如果通过采样数据的后期数据处理滤除干扰,根据采样定理,必须在硬件上设置抗混叠滤波器,限制输入信号带宽至1/2 采样频率以下。

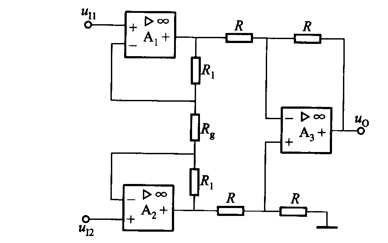

1. 有源滤波器

标准化电路中复用ADC 驱动运放,实现三阶有源低通滤波器,详见图2.13。

图2.13 三阶低通有源滤波器

滤波器的低通截止频率设置为9kHz,类型为三阶贝塞尔,具有良好的衰减特性。并且使用图2.13 中的3 阶电路形式,避免了常规单运放实现二阶Sallen-Key 型滤波器拓扑,由于运放带宽不够,出现的高频馈通问题。即使用带宽不高的运放LMV358A,也不会出现高频信号穿透滤波器,详见图2.14。

图2.14 三阶滤波器的频率响应

2. 电阻噪声与运放的电源抑制比

一般来说,有源滤波器自身可能产生噪声,通常称之为器件噪声,其分别为电阻的热噪声、运放的电压输出噪声。电阻值越大所引入的电阻噪声越大,1kΩ 电阻的Johnson 噪声大约是4nV/(Hz)1/2,这个数值以电阻的平方根规律变化。若考虑到电阻噪声,推荐的阻值是1~10kΩ。电阻噪声最后可以归结到的滤波电路中被滤除,但是它和运放输出噪声是电路中噪声产生的源头,在设计时要予以考虑,适当的采用低阻值电阻和低噪声运放。

此外需考虑运放的电源抑制比。电源上的噪声会随着每个有源器件的电源引脚传导到信号通路中,作为ADC 驱动放大器的运放,其自身的电源抑制比若不能抑制这些噪声的话,噪声就会叠加到运放的输出中。特别是电路中采用了开关电源供电时,电源上会有高频尖峰电压噪声,而运放的电源抑制比在高频时通常下降得厉害,对它们没有抑制作用。以标准电路图中所用的运放LMV358A 为例,其电源抑制比详见图2.15。

图2.15 LMV358A 电源抑制比

解决这个问题简单方法是采用RC 低通滤波器对运放电源进行滤波,滤除其电源抑制比较低的高频成分,如图2.13 所示的R4、C7。若将运放的电源端视为高阻抗(其工作电流小),算得RC 滤波器的截止频率约为:1.6kHz,可以对高频干扰信号起到有效衰减。

3. 运放选型

使用LPC82x 内部ADC 的采集应用,通常对器件成本的要求非常严酷,标准化电路设计考虑使用最低成本运放——LM358 系列。

经典运放器件通常存在两个问题,单电源条件下输入和输出信号范围不能达到电源电压(输入输出不能轨至轨),信号测量范围窄;输入失调电压与偏置电流比较大,直流精度影响大,因此不能使用。但现在已经有不少厂家生产LM358 兼容或改进产品,详见表2.3。

表2.3 低成本运放参数选型

表中的数据表明,只有3peak 公司的改进型器件LMV358A,同时支持轨至轨输入与输出,FET 输入级并且失调电压比较低,成本与原LM358 一致,能够符合应用需求,因此标准化电路最终选用LMV358A。

>>> 2.2.5 模拟地与数字地

具有内部ADC 的MCU 一般有独立AGND管脚,以及普通GND 管脚。如何把AGND 连接到GND 往往模糊不清,避免二者相互干扰的最优设计方法是,AGND 和GND 管脚都就近接到地平面,详见图2.16。

图2.16 AGND 与GND 的连接处理

了解混合信号IC 内部的接地管脚结构,有助于理解IC 设置独立模拟地、数字地管脚的意图,详见图2.17。使接地管脚保持独立,可以避免将数字信号耦合至模拟电路内。在IC 内部,将硅片焊盘连接到封装引脚的邦定线难免产生线焊电感LPLP 和电阻RPRP,IC 设计人员对此是无能为力的。如果共用地管脚,快速变化的数字电流在B 点产生电压,对于模拟电路无法接受,IC 设计人员意图分开接地管脚,排除此影响。

图2.17 IC 内部模拟与数字地的连接情况

但是,分开之后B 点电压还会通过杂散电容CSTRAYCSTRAY 耦合至模拟电路的A 点。IC封装每个引脚间约有0.2 pF 的寄生电容,是无法避免的。为了防止进一步耦合,AGND 和DGND 应通过最短的引线在外部连在一起,并接到模拟接地层。DGND 连接内的任何额外阻抗将在B 点产生更多数字噪声;继而使更多数字噪声通过杂散电容耦合至模拟电路。

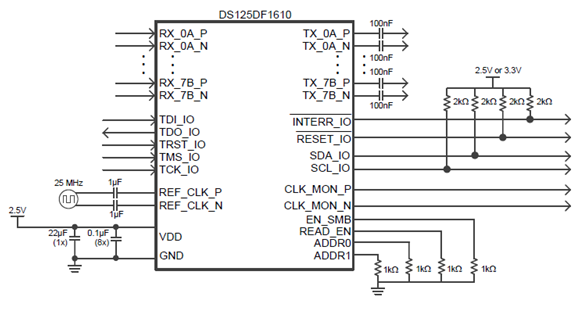

>>> 2.2.6 I/O 扇出电流

由于LPC82x 只有一个电源管脚,即MCU 数字电源与内部ADC 模拟电源共用。虽然这样设计可以在小封装中提供尽可能多的I/O 口,但是对模拟部分会带来干扰问题:MCU工作时在电源上产生数字开关电流,通过共用管脚产生噪声电压,干扰内部ADC。下面的优化建议可以很大程度上避免干扰:

-

避免I/O 口直接驱动大电流,使用三极管或逻辑芯片间接驱动,详见图2.18;

-

若条件允许,则切换到低功耗模式下执行ADC 采集。

图2.18 使用驱动电路减小I/O 扇出

-

电路设计

+关注

关注

6673文章

2451浏览量

204125 -

adc

+关注

关注

98文章

6495浏览量

544446

发布评论请先 登录

相关推荐

信号调理产品电路设计与寄存器配置

振动信号调理硬件电路设计

测控、信号调理电路、小信号源功率电路设计。

混合信号电路设计技术研究

心电信号调理电路设计

ADC 信号调理电路设计——应用背景和电路设计

ADC 信号调理电路设计——应用背景和电路设计

评论