由于芯片设计复杂度的提升、集成规模的扩大,以及产品上市时间要求的缩短,使得设计验证变得更加困难。特别是在多FPGA环境中,设计调试和验证的复杂性进一步增加,传统的调试手段难以满足对高性能、高效率的需求。因此,高效的调试(Debugging)手段在原型验证中显得尤为重要。今天,我们将探讨设计调试的常见方法,涵盖从简单到复杂的多种调试。

1. 原型验证为什么重要?随着大规模集成电路设计复杂性的增加,芯片验证面临着巨大的资金和时间挑战。早期开发者只能通过vwin

或流片来验证设计,耗时且成本高。原型验证通过在流片前尽可能还原芯片的实际使用场景,确保功能模块的可靠性和稳定性,同时评估性能。这不仅能缩短芯片上市时间,还可以向客户演示产品并提前预售。此外,原型验证还可以显著降低成本。在通过功能验证后,原型验证使得驱动开发能够提前展开,无需等待芯片流片(Tape Out)。当芯片回片后,应用程序可以基于原型验证时开发的驱动进行简单适配,迅速应用于SoC上,进一步缩短上市周期。

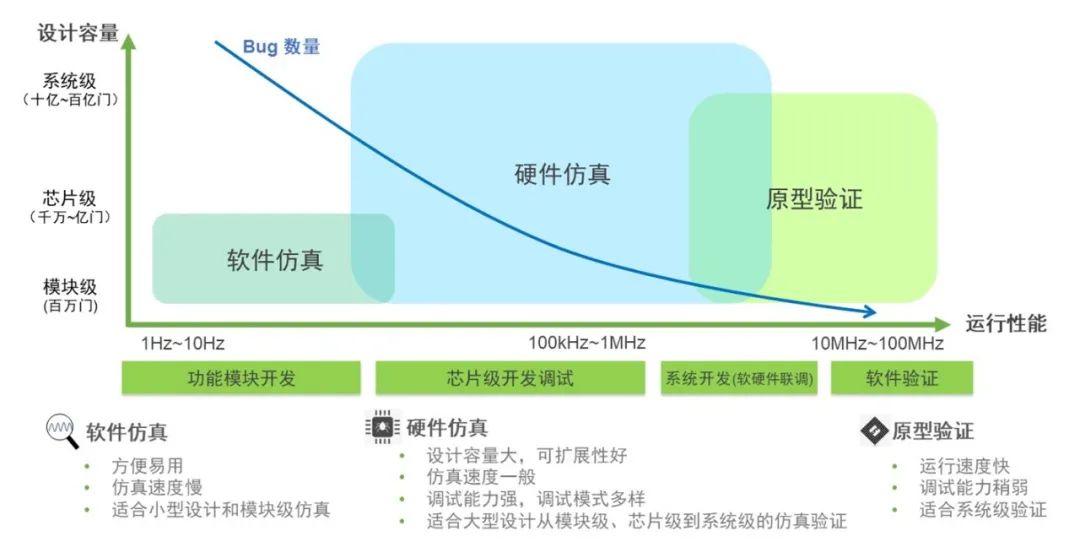

与软件仿真和硬件仿真相比,原型验证的最大优势在于其高性能。当前有多种验证方法可供选择,如软件仿真、硬件仿真和原型验证。三者在芯片前端设计的功能验证阶段发挥着重要作用。相比之下,软件仿真操作简便,但速度较慢,适合小型设计和模块级验证;硬件仿真容量大,扩展性好,调试能力强,适合大型设计的模块、芯片级和系统级验证;而原型验证则运行速度快,但调试能力相对较弱。如今许多用户依赖FPGA芯片供应商提供的调试工具,但这些调试手段相对单一且有限。接下来,我们将详细介绍如何应对这些调试挑战,并介绍思尔芯在这一领域的调试方案。

在调试与观测工具方面,思尔芯的芯神瞳 Prodigy原型验证解决方案就提供了全面且灵活的调试手段,配备了实时控制软件(Player Pro-RunTime)、设计调试软件(Player Pro-DebugTime)、深度调试套件 Multi-Debug Module(MDM)、协同仿真软件ProtoBridge等完整工具链,极大提升了用户效率。这些功能的增加主要是由于思尔芯面向广泛的客户需求,而这是其他厂商可能未能提供的。

2. 设计调试有哪些手段?

在原型验证中,调试的核心任务是定位和解决设计中的故障,以确保系统功能的正确性。特别是在大规模复杂的SoC设计原型验证过程中,工程师需要确保设计中的问题是可调试的,最大程度地减少开发过程中花费在调试上的时间。通常,用户将设计下载到FPGA后,第一次运行时总会遇到各种失败情况。这些失败的原因可能是FPGA原型的网络不正确、设计本身存在问题,或是设计在编译过程中引入的错误(如由于设计分割和引脚复用引起的时序错误)。因此,开发人员需要有效的软件调试和观测工具,来确认硬件是否正常运行,所有功能模块是否按照预期工作,以快速定位和解决问题。这就需要借助外部逻辑分析仪或内嵌逻辑分析仪来探测故障的根源。

目前,常见的设计调试手段包括:基本I/O、AXI总线事务、信号级调试以及基于协议的连接等。多数用户还习惯于使用FPGA厂商提供的内嵌逻辑分析仪,进行原型验证系统上板测试阶段的调试。然而,这些工具在面对复杂的多FPGA设计,即大规模复杂设计时,可能会面临资源消耗过大以及管理难度较高的问题。

思尔芯为工程师们提供了一套全面且灵活的调试解决方案,涵盖从简单到复杂的多种调试方法,满足不同客户在原型验证中的多样化需求,确保调试过程顺利进行。

- 基本I/O调试(Basic I/Os)

FPGA厂商在其软件生态系统中也提供了多种信号级探测工具,常见的解决方案包括VIO IP核、信号源和探针编辑器,这些工具通常通过JTAG进行监控和驱动网络。而思尔芯的I/O调试功能更加丰富,不仅在原型验证系统上集成了多个基本的I/O接口,如按键、DIP开关、GPIO和UART等,使设计中的交互操作更加直观便捷。此外,思尔芯的Player Pro软件通过虚拟接口增强了远程诊断能力,使调试过程更加高效便捷。

- 总线事务调试(Bus Transaction Debugging)

在复杂SoC设计中,AXI总线事务调试是一种非常有效的手段,特别是在AXI已成为主流协议的设计中。思尔芯的ProtoBridge解决方案通过PCIe提供约4GB/s的高带宽,实现AXI事务的高性能桥接。该解决方案包括一个AXI桥接的RTL接口,便于与测试设计连接,同时还提供PCIe设备驱动程序和API,支持开发基于软件的激励,很适合软硬件协同开发。此外,思尔芯的原型验证已内建大约10Mbps的以太网调试,支持设计中存储器映射AXI从设备的快速读写访问,可以满足低带宽的AXI调试需求。

- 信号级调试(Signal Level Debugging)

信号级调试是原型验证中最基础且常用的调试方法,主要通过探测设计中的内部信号来诊断问题。思尔芯的Player Pro软件在此领域表现尤为出色,能够帮助设计人员轻松将内部信号引出并分配给I/O,从而更有效地进行调试。思尔芯还提供了多种扩展卡,方便用户进行针脚连接、3.3V电压转换,此外还增加了额外的按钮和开关接口以及外部逻辑分析仪的连接接口,进一步提高了调试的灵活性和效率。

- 基于协议的调试(In-System Protocol Debugging)

当FPGA原型与真实世界的数据进行交互时,基于协议的调试尤为重要。思尔芯提供了超过90种现成的扩展卡和参考设计,帮助用户实现多种协议的系统内测试。如果用户有更为特殊的需求,思尔芯还可以提供定制化的解决方案,以优化系统级的测试和调试,确保用户的原型验证过程顺利完成。

强大的调试工具包括逻辑分析仪、协议分析仪和实时监控工具等。这些工具必须能够与原型验证平台无缝集成,提供实时的调试信息和可视化的数据分析功能。此外,还需要支持远程调试,以便在不同地理位置的团队之间进行协作。主要挑战在于如何在不影响系统性能的情况下,提供详尽的调试信息,以及设计直观高效的调试界面。确保这些工具能够快速、准确地反馈系统状态和数据,以便开发人员及时发现和解决潜在问题。通过这些多样化的调试方法,思尔芯不仅帮助用户在原型验证中快速定位问题,还极大地提升了调试效率和系统稳定性,确保设计能够顺利进入下一个开发阶段。

- 深度逻辑分析调试方案

FPGA厂商的嵌入式逻辑分析仪(如SignalTap和ChipScope)通常用于在FPGA的片上RAM块中采样和存储信号,随后通过JTAG读取这些信号。目前,大多数用户已经习惯使用FPGA厂商提供的嵌入式逻辑分析仪(ILA)来进行单颗FPGA的原型验证系统调试。

然而,对于需要进行深度调试或多FPGA级联的用户来说,常遇到的问题是需要更多内存来存储信号,以及跨FPGA的调试需求。由于FPGA内部资源有限,且多FPGA级联的原型验证系统规模庞大,多个模块通常分散在不同的FPGA中。此时就需要具备cross-trigger功能,即当某颗FPGA中的调试模块触发时,能够同时抓取多颗FPGA中的调试模块的trace数据。一些FPGA厂商提供的ILA可以实现同一颗FPGA内不同的时钟域以及不同FPGA之间的ILA内核的交叉触发。

为了更好地支持多FPGA的信号级探测,思尔芯提供了多 FPGA 并发深度调试方案。最新的MDM Pro支持同时对多达8个FPGA进行并发探测,并具备多FPGA触发功能。MDM Pro配备了64GB的内置DDR4内存,能够实现深度信号跟踪。它可以捕获多达16K条信号,分为8组,每组包含2K个探针,而无需重新编译FPGA。这一解决方案通过将MDM Pro预构建到我们的Quad 10M和Quad 19P逻辑系统中,提升了生产力。MDM Pro的触发设置设计直观,且与FPGA厂商工具中的触发设置非常相似,确保了工程师在使用时能够顺畅过渡。

MDM Pro具备灵活性,能够适应不同的设计流程偏好,支持IP模式和编译模式两种流程。在IP模式下,设计人员可以直接在RTL中实例化MDM客户端,以连接他们希望捕获的信号。或者,设计人员也可以通过编译模式,使用Player Pro指定需要捕获的信号,从而提供了一种高效且多样化的调试方式

。3. 写在最后

在芯片设计过程中,原型验证在性能上显著优于软件仿真和硬件仿真,尽管在可视性方面稍显不足。这促使了商用原型验证解决方案对高效调试手段的深度需求与重要性,以最大化原型验证的优势。作为国内最早推出原型验证工具的EDA供应商,思尔芯一直以来通过其全面且灵活的调试手段提升原型验证的生产力和效率。由于在大规模复杂 SoC 设计原型验证过程中,可用的可视性往往局限于单个FPGA,这使得跨多个FPGA映射的设计使调试可见性变得更加困难。思尔芯高效且多样化的调试方式,适用于从简单到复杂的多种应用场景,尤其应对多FPGA环境中的复杂挑战,并在工程师加速设计验证和缩短上市时间方面发挥了关键作用。

-

芯片

+关注

关注

455文章

50711浏览量

423095 -

集成电路

+关注

关注

5387文章

11529浏览量

361591 -

soc

+关注

关注

38文章

4161浏览量

218149 -

验证

+关注

关注

0文章

61浏览量

15187

发布评论请先 登录

相关推荐

Nordic推出最新物联网原型验证平台Thingy:91 X

芯华章发布新一代FPGA原型验证系统HuaPro P3

芯华章推出新一代高性能FPGA原型验证系统

国产EDA公司芯华章科技推出新一代高性能FPGA原型验证系统

SOC芯片设计的挑战与解决方案

解决验证“最后一公里”的挑战:芯神觉Claryti如何助力提升调试效率

快速部署原型验证:从子卡到调试的全方位优化

康谋分享 | 在基于场景的AD/ADAS验证过程中,识别挑战性场景!

解锁SoC “调试”挑战,开启高效原型验证之路

解锁SoC “调试”挑战,开启高效原型验证之路

评论