随着无线通信的快速发展和广泛普及,无线系统标准对收发机的性能要求越来越高。功率放大器作为发射机的主要组成部分,其指标决定着发射机的性能,如效率 决定着整机功耗,线性度决定着整机的动态范围,谐波分量大小又是发射机线性度的度量。传统的功率放大器为了获得较高效率,功放管通常会工作于饱和状态,这 时将有大量的谐波分量产生。如果不对谐波分量加以回收和抑制,这不单会造成能量的浪费,降低了其效率,还会对其他信道的信号造成干扰。

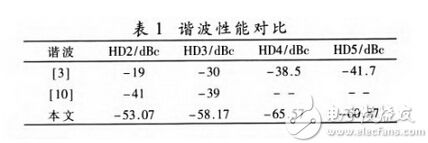

通常功率放大器为了获得较高的效率和较低的谐波分量都使得功率放大器工作于F类,但该结构需要采用λ/4传输线,占用空间面大,不利于小型化。采用了 低通输出匹配网络设计了一个工作于E类的功率放大器,在11 dBm输入时的2~5阶谐波分量分别为:-19 dBc、-30 dBc、-38.5 dBc、-41.7 dBc。但该结构采用E类放大器,它要求功放管具有较高的集电极击穿电压,这与集成电路发展趋势相违背。采用GaN工艺设计的功率放大器,为了 获得较好的谐波性能,该设计在输出匹配网络中引入了两根开路传输线,但开路传输线的使用使得该方法与现代电路向小型化、集成度高方向发展相违背。

本文提出了一种结构简单、利于集成且具有谐波抑制功能的输出匹配网络,利用该方法采用InGaP/GaAs HBT工艺设计了一个工作于2 GHz频率的功率放大器。测试结果表明,利用该方法设计的功率放大器获得了较高的效率和很好的谐波性能。

1 电路设计

一个典型的功率放大器通常由输入匹配网络、放大电路、直流偏置电路和输出匹配网络组成。然而对功率放大器性能起决定性作用的还是匹配网络。它作为 功率放大器的重要组成部分,任何一个不合适的匹配网络都可能会引起电路的不稳定,导致功率放大器输出功率小、效率低,恶化其线性度。设计匹配网络时,在满 足基本的阻抗变换的同时,还要兼顾到其谐波阻抗,插入损耗以及网络的带宽,最后还需要考虑所设计的网络是否易于实现以及小型化。

1.1 具有谐波抑制功能的输出匹配网络

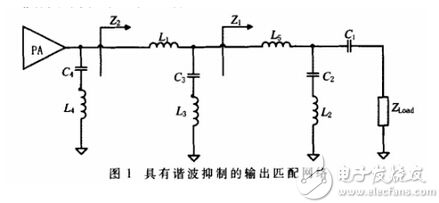

输出匹配网络作为匹配网络中最重要的部分,决定着功率放大器的功率和效率,以及最终功率放大器的谐波性能。文献[6-7]详细说明了输出匹配网络二次谐 波阻抗对其效率的影响,但都忽略了高次谐波的影响。本文设计的输出匹配网络在考虑二次谐波阻抗的同时,还兼顾了高次谐波阻抗,其结构如图1所示。

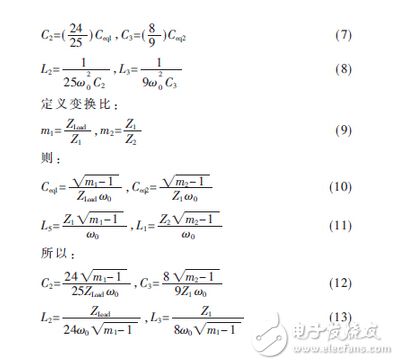

其中C1起隔直作用,L1、C3和L5、C2构成一个二级低通网络,在基频时主要起阻抗变换作用,在高阶奇次谐波处呈现出高阻抗,C4和L4构成一个串 联LC谐振网络,谐振频率为2ω0,其中ω0为基频,使得输出网络在二次谐波处得到一个短路的负载。该结构类似于F类功率放大器[8],对奇次谐波负载呈 现高阻抗,对偶次谐波负载呈现低阻抗,有利于对功放管的输出电压电流波形进行整形,减小两者之间的重合提高了效率[9]。同时为了对高次谐波能量进行回收 和抑制,在该两级LC低通匹配中加入了两个电感L3和L2,它和C3、C2构成一个串联谐振网络,谐振频率分别为3ω0和5ω0,即分别对3次谐波和5次 谐波进行处理。输出匹配结构的分析如下:对于功放管的负载,它的值大小与输出功率的关系为:

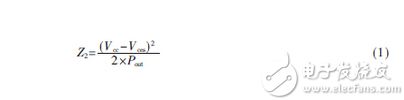

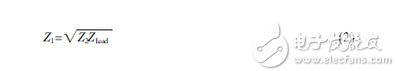

为了获得较好的网络带宽,两级LC低通匹配网络中间级的阻抗为:

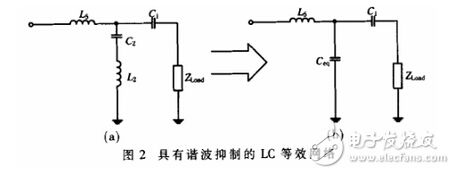

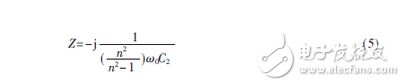

对于由LC构成的谐波处理网络,当其谐振在高次谐波频率上时,在基频处,该网络等效为一个电容,如图2所示,设L2C2谐振在n次谐波处(图2(a)),在基频处它等效为电容Ceq1(图2(b)),其关系为:

工作于基频时,该网络的阻抗为:

联立(3)(4)两式得:

即谐振网络在基频处的等效电容与谐振网络的电容关系为:

对于本设计因L2C2谐振在5次谐波频率处,L3C3谐振在3次谐波频率处,所以有:

对于L4C4组成的串联谐振网络,其谐振频率为2ω0,主要用于回收2次谐波能量,这样能对功放管输出端的电压和电流波形进行整形,减小两者之间的重合,提高功率放大器的效率。电容电感两者之间满足以下关系式:

1.2 整体电路设计

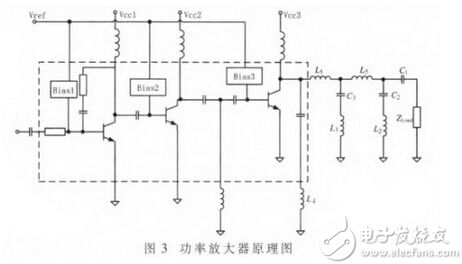

本文采用以上介绍的具有谐波抑制功能的输出匹配网络,采用InGaP/GaAs HBT工艺设计了一个工作于2 GHz频率的高效率高谐波抑制的功率放大器,该放大器采用三级放大结构,供电电压为5 V,具体电路结构如图3所示。

该设计为了获得高的增益采用了三级放大结构,其中第一级工作于A类状态,以获得高的线性度,该级采用了一个RC负反馈使电路能稳定工作;第二级工作于浅 AB类状态;第三级为了获得高的效率工作于深AB类状态。其中虚线方框内的部分为片内实现,方框外的部分采用多层基板、绑定线和贴片元件来实现。对于级间 匹配网络,匹配电感于外部绑定线实现有助于减少级间匹配网络的插损,获得了较高的效率和功率,同时调试灵活方便。对于输出匹配网络,其中L4由绑定线和基 板上的传输线共同组成,通过调节金线的长度,可以控制二次谐波分量的大小。而对于L3和L2,由于该网络是对高次谐波进行抑制,所需电感较小,主要是由多 层基板的过孔构成。

2 测试结果

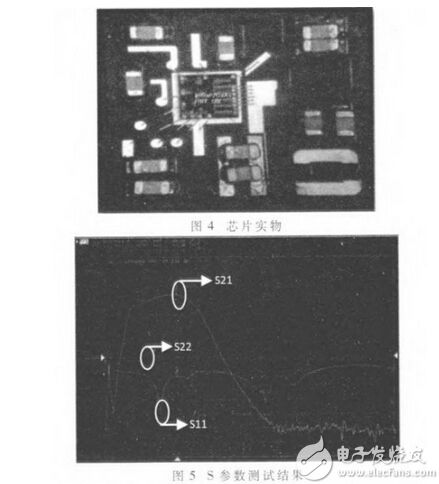

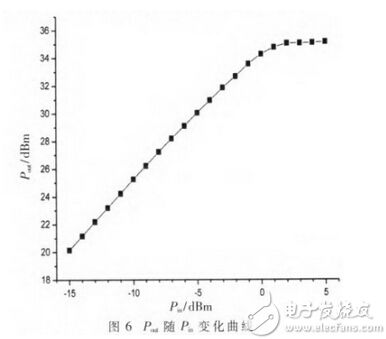

本芯片采用InGaP/GaAs HBT工艺制作,图4为芯片实物图,DIE面积为1 mm×1 mm,整体封装大小为4 mm×4 mm。图5为本设计S参数测试结果,测试平台为安捷伦矢量网络分析仪E5071C。测试结果表明,在2 GHz频率处该设计的S参数为:S21=35.1 dB,S11<-10 dB,S22<-10 dB,从S参数看出本设计获得了很好的小信号性能。图6为输出功率和输入功率的关系图,从图可知当Pin小于0 dBm时,放大器工作于线性工作状态,当Pin大于0时开始出现压缩,到达3 dBm时,输出功率已经饱和,此时Pout=35.2 dBm,放大器的1 dB压缩点为P1dB=34.2 dBm。

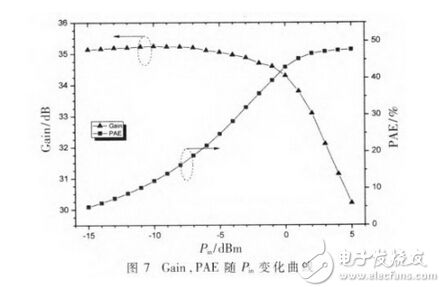

从该图可知,该放大器获得了较好的线性度。图7为增益Gain和效率PAE随着输入功率的变化的曲线图,该图表明该设计的增益在Pin<0 dBm时,增益波动小于0.2 dB,表明该设计获得了很好的AM-AM,在饱和工作时,即Pout=35.2 dBm时,效率为PAE=48%;工作于1 dB压缩点时,即Pout=34.2 dBm时,效率为PAE=43%。从效率曲线图可知,该放大器不但在饱和工作时获得了很高的效率,在线性工作时也获得了很好的效率。表1是该设计的谐波性 能与其他设计的比较,从表1可知本设计在考虑二次谐波同时还兼顾了高次谐波,达到了良好的谐波抑制,特别是在对高次谐波的处理上。

3 总结

本文通过在功率放大器的输出匹配网络中引入多个LC谐振网络来对功率放大器的谐波能量进行回收和利用,提高了功率放大器的效率,抑制了负载端的谐波分 量。该方法简单,易于实现及利于功率放大器的小型化。利用该方法设计了一个工作于2 GHz频率的功率放大器,该功率放大器的实测结果为:增益为Gain=35 dB,1 dB压缩点为P1dB=34.2 dBm,饱和工作时效率为PAE=48%,各次谐波分量大小分别为:HD2=-53 dBc、HD3=-58 dBc、HD4=-65 dBc、HD5=-60 dBc。测试结果表明,该方法设计的功率放大器获得了很好的效率和谐波性能。

-

功率放大器

+关注

关注

102文章

3568浏览量

131809 -

功放管

+关注

关注

1文章

27浏览量

17758 -

谐振网络

+关注

关注

0文章

3浏览量

8060

发布评论请先 登录

相关推荐

设计高谐波抑制功率放大器的几大要点剖析

设计高谐波抑制功率放大器的几大要点剖析

评论