半加器(Half Adder)和全加器(Full Adder)是数字电路中的基本组件,用于执行二进制加法运算。它们的主要区别在于功能和输入输出的数量。

1. 功能差异

半加器 :

- 半加器只能处理两个一位二进制数的加法,即A和B。

- 它不考虑前一位的进位输入。

- 它的输出包括和(Sum)和进位(Carry)。

全加器 :

- 全加器可以处理三个一位二进制数的加法,包括两个加数(A和B)以及一个前一位的进位输入(Cin)。

- 它的输出同样包括和(Sum)和进位(Cout)。

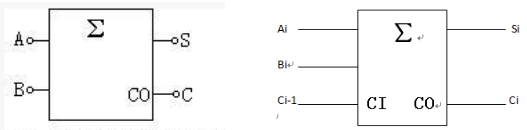

2. 输入输出差异

半加器 :

- 输入:两个位(A和B)。

- 输出:两个位(和与进位)。

全加器 :

- 输入:三个位(A、B和一个进位输入Cin)。

- 输出:两个位(和与进位)。

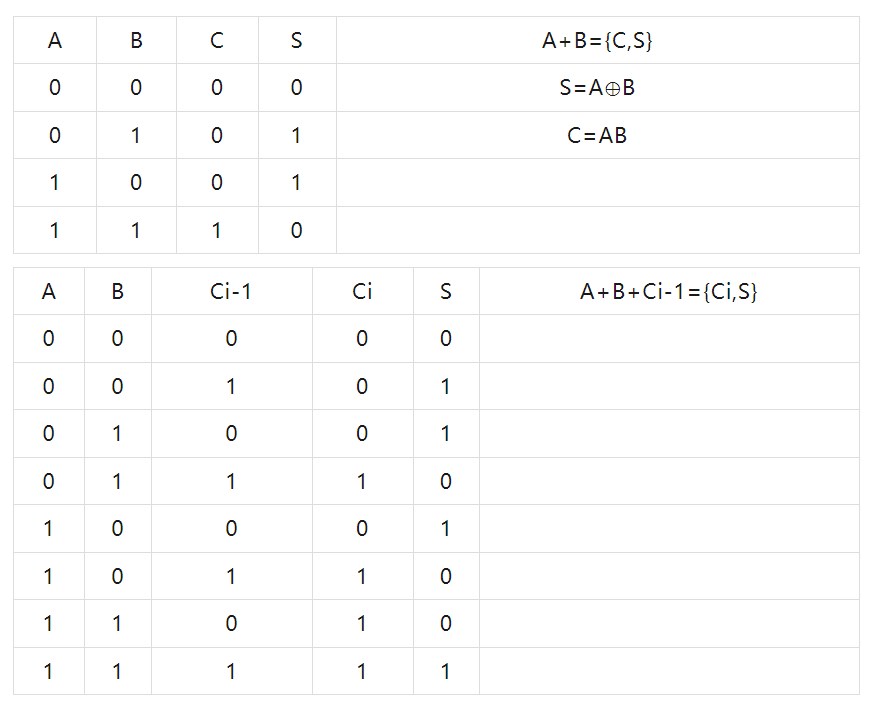

3. 真值表

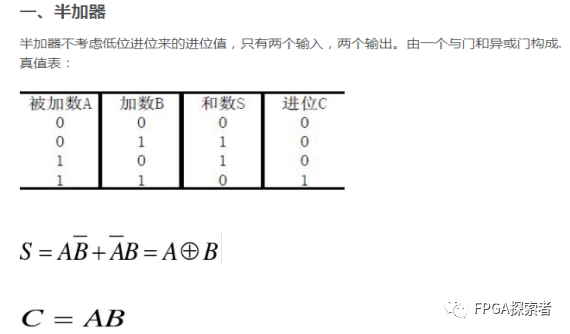

半加器的真值表 :

| A | B | Sum | Carry |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

全加器的真值表 :

| A | B | Cin | Sum | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

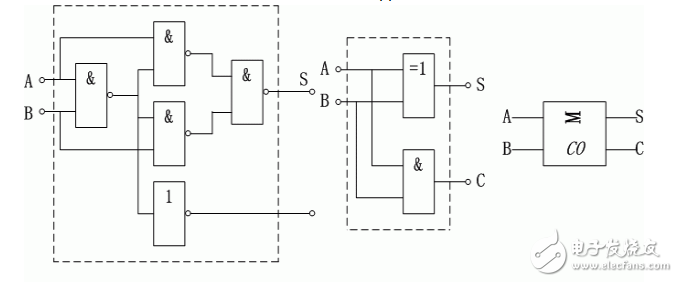

4. 电路实现

半加器 :

- 可以通过一个异或门(XOR)来实现和(Sum),一个与门(AND)来实现进位(Carry)。

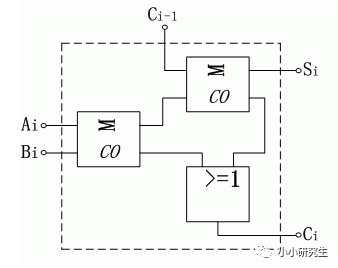

全加器 :

- 可以通过两个半加器和一个或门(OR)来实现。第一个半加器处理A和B,第二个半加器处理第一个半加器的和与进位输入Cin。

5. 应用场景

半加器 :

- 由于半加器不考虑进位,它通常用于简单的加法运算,或者作为更复杂加法器(如全加器)的一部分。

全加器 :

- 全加器由于考虑了进位,因此可以用于实现多位二进制数的加法。在多位数的加法运算中,全加器可以串联起来,每个全加器处理一位的加法,并将进位传递给下一个全加器。

6. 性能和效率

半加器 :

- 由于功能简单,半加器的电路实现通常比全加器更简单,延迟也更小。

全加器 :

- 全加器虽然功能更强大,但电路更复杂,可能会有更高的延迟。

7. 总结

半加器和全加器的主要区别在于它们处理的输入数量和是否考虑进位。半加器适用于简单的一位加法,而全加器适用于更复杂的多位加法。在设计数字电路时,根据需要处理的数据位数和复杂性,可以选择适当的加法器类型。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

全加器

+关注

关注

10文章

62浏览量

28493 -

数字电路

+关注

关注

193文章

1605浏览量

80577 -

半加器

+关注

关注

1文章

29浏览量

8790

发布评论请先 登录

相关推荐

FPGA入门——1位全加器设计 精选资料分享

FPGA入门——1位全加器设计一、原理图输入1.1 创建工程1.2 原理图输入1.3 将设计项目设置成可调用的元件1.4 半加器仿真1.5 设计全加

发表于 07-26 07:01

半加器和全加器的区别是什么

半加器和全加器的区别是什么

评论