一、背景

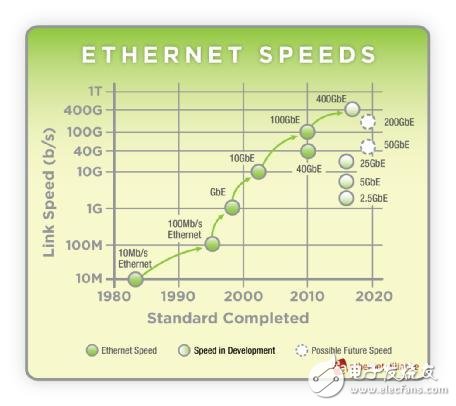

高速串行通道(Serdes)是目前绝大多数通信系统中用到的数据传输通道,为满足人们对图片、视频传输所带来的日益增长的带宽需求,通信设备中高速串行通道上的信号速率以每五年翻一倍的速度进行提升。从最初的单链路10Mb/s速率一路提升到当前业界广泛应用的25Gb/s速率,而且未来还会向着56G、112G等更高速率持续演进,图1所示即为以太网联盟定义的以太网速率升级路线图。

图1 未来五年以太网速率升级路线图

对于几十Gbps速率的高速串行链路,单纯依靠以往的设计经验,已经无法确保高速链路设计的正确性。因此,需要采用各种高频电磁场仿真的EDA工具软件,在设计前和设计完成后对高速串行链路进行前仿真和后仿真分析,充分验证高速串行链路的各种电气性能是否满足设计要求,从而确保一次性地设计成功,满足产品上市的时间需求。

当前业界已经有多款高频电磁场仿真工具,如ANSYS Electronics系列仿真工具(包括HFSS、SIWave、SystemSI、Nexxim等)、KeySight ADS/EMPro等、Cadence Sigrity仿真套件、Synopsys HSpice等。这些EDA仿真软件均为国外大厂开发,且经过了多年的业界应用,软件的功能、易用性、仿真精度等各方面都经过了充分验证。但正如前文所述,人们对以太网带宽持续提升的迫切需求使得路由器、交换机、服务器等数据通信设备中的高速串行链路速率飞速提升,如何实现对更高信号速率链路的准确建模分析,成为了当前EDA仿真软件领域各个厂家均需面对的课题。另外,随着信号速率的提升,高速链路中以往可以忽略的一些影响因素,如绿油影响、BGA焊球、走线泪滴等,在当前的仿真模型中均需考虑进去。

芯禾的Expert系列软件(Via Expert、Snp Expert、Channel Expert)是完全在国内研发的一套高频电磁场仿真分析软件,在吸取了上述各个EDA国际大厂软件优点的基础上,为信号完整性设计者提供了一整套更加便捷的高速Serdes链路建模、仿真、分析方法。基于芯禾的Expert系列软件,可以让SI仿真人员从繁琐的通道建模和数据分析中解放出来,将精力更加集中在通道链路的性能分析和优化上,从而大幅提升仿真设计效率。

下面将详细讲解使用芯禾Expert系列软件实现高速链路的前仿真和后仿真方法。

二、高速链路的前仿真

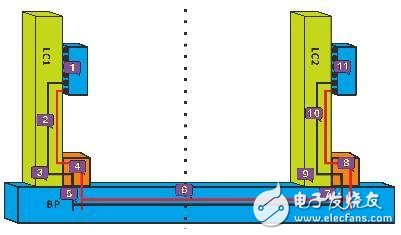

图2 传统背板系统链路示意图

图2所示为传统背板系统链路,信号从一块子卡上的芯片发出,经过背板后被另一块子卡上的芯片接收。以此信号拓扑为例,高速Serdes链路的前仿真过程包括了以下几个步骤:

2、建立各块单板上信号孔和走线的模型;

3、搭建整体链路拓扑,仿真链路的插损、回损、阻抗等曲线;

4、查看仿真结果,并将仿真结果与国际标准进行对比,判断链路的电气性能是否满足规范要求。

由于连接器厂家通常会提供其高速连接器的S参数模型给用户,因而,对高速通道仿真人员来说,仿真的实际工作是从上述第二步开始的。

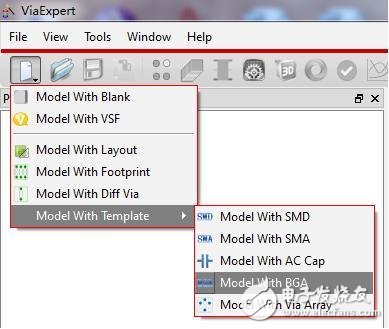

如图3所示,在Via Expert软件中有各种建模的Template。使用这些Template,用户只需要跟随向导界面,设置好叠层和相关参数,就可以由软件自动建出所需的三维模型。相比于HFSS、EMPro、Sigrity等软件,Via Expert针对PCB链路建模所做的这些Template大大简化了仿真人员的建模工作量,使得用户通过GUI界面向导,在很短的时间内就可以建出所需的模型。

图3 使用Via Expert自带的各种Template建出PCB上各种孔的模型

-

高速链路

+关注

关注

0文章

4浏览量

6773 -

芯禾expert

+关注

关注

0文章

1浏览量

1222

发布评论请先 登录

相关推荐

芯海科技引领信号链MCU新纪元:SmartAnalog®系列惊艳登场

芯和半导体正式发布EDA2024软件集

IG网关产品实现链路备份的方法

高速信号传输链路的损耗和均衡

如何识别光纤链路问题?

电路仿真软件如何使用 电路仿真软件操作流程

如何辨别光纤链路的好坏?

永久链路、信道测试的区别

芯和ChannelExpert高速通道分析软件入选2023工业软件推荐目录

使用芯禾Expert系列软件实现高速链路仿真

使用芯禾Expert系列软件实现高速链路仿真

评论