与亚微米工艺类似,多晶硅栅工艺是指形成 MOS器件的多晶硅栅极,栅极的作用是控制器件的关闭或者导通。淀积的多晶硅是未掺杂的,它是通过后续的源漏离子注入进行掺杂,PMOS 的栅是p型掺杂,NMOS 的栅是n型掺杂。

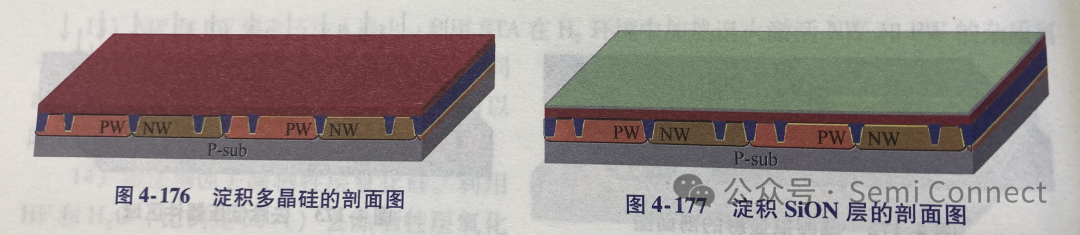

1)淀积多晶硅栅。利用LPCVD沉积一层多晶硅,利用SiH4在630°C左右的温度下发生分解并淀积在加热的晶圆表面,形成厚度约3000A的多晶硅。在CMOS 工艺中掺杂的多晶硅会对器件的阈值电压有较大影响,而不掺杂多晶硅的掺杂可以由后面的源漏离子注入来完成,这样容易控制器件的阈值电压。图4-176所示为淀积多晶硅的剖面图。

2)淀积 SiON。利用 PECVD 淀积一层厚度约200~300A的SiON 层,利用SiH4、N2O和He在400°C的温度下发生化学反应形成SiON淀积。SiON 层作为光刻的底部抗反射层。图4-177所示为淀积 SiON 层的剖面图。

3)栅光刻处理。通过微影技术将栅极掩膜版上的图形转移到晶圆上,形成栅极的光刻胶图案,器件栅极区域上保留光刻胶。AA作为栅极光刻曝光对准。图4-47所示为电路的版图,工艺的剖面图是沿 AA'方向,图4-178所示为栅光刻的剖面图,图4-179 所示为栅显影的剖面图。

4) 测量栅极光刻关键尺寸。

5)测量栅极光刻套刻,收集曝光之后的栅极光刻与 AA 的套刻数据。

6)检查显影后曝光的图形。

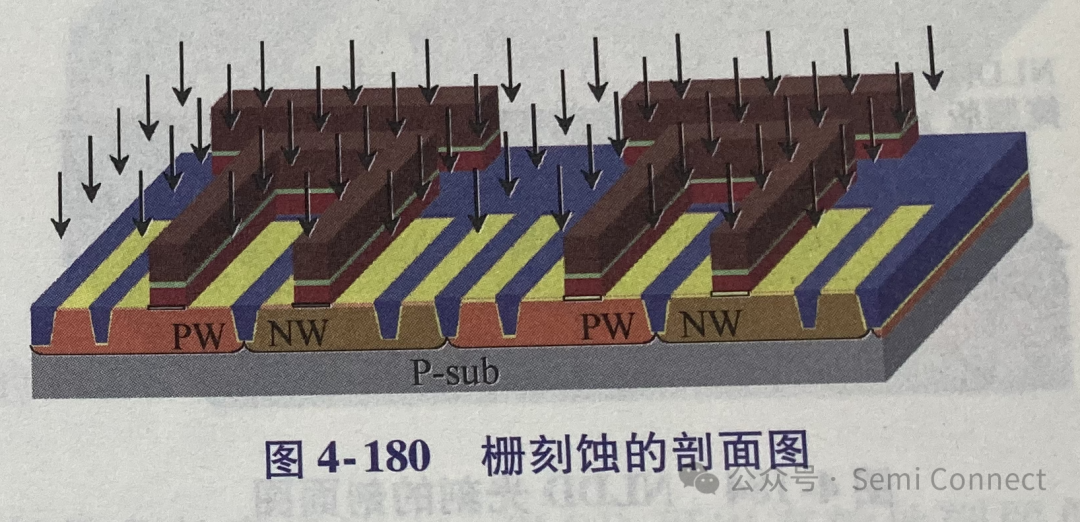

7)栅刻蚀。利用干法刻蚀去除没有光刻胶覆盖的多晶硅形成器件的栅极,刻蚀的气体是CF4、CHF3、CL2和 HBr。刻蚀分两步:第一步是利用CF4和 CHF3去除SiON;第二步是利用CL2和 HBr刻蚀多晶硅。刻蚀会停止在氧化物上,因为当刻蚀到氧化物时,终点侦测器会侦查到硅的副产物的浓度减小,提示多晶硅刻蚀已经完成,为防止有多晶硅残留导致短路,还会刻蚀一段时间。图4-180所示为栅刻蚀的剖面图。

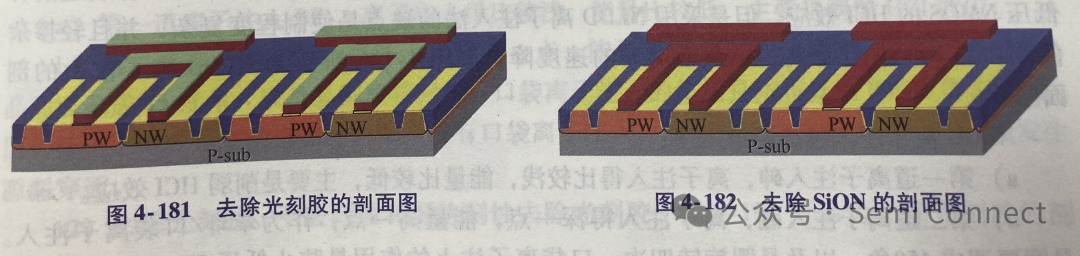

8)去除光刻胶。利用干法刻蚀和湿法刻蚀去除光刻胶。图4-181 所示为去除光刻胶后的剖面图。

9)去除SiON。利用热 H3PO4与SiON反应去除栅极上的SiON。如图4-182所示,是去除SiON 的剖面图。

-

晶圆

+关注

关注

52文章

4890浏览量

127929 -

工艺

+关注

关注

4文章

592浏览量

28779 -

MOS

+关注

关注

32文章

1269浏览量

93675

原文标题:多晶硅栅工艺-----《集成电路制造工艺与工程应用》 温德通 编著

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

分析MOS管未来发展与面临的挑战

低温多晶硅的工作原理是什么?

低温多晶硅,低温多晶硅是什么意思

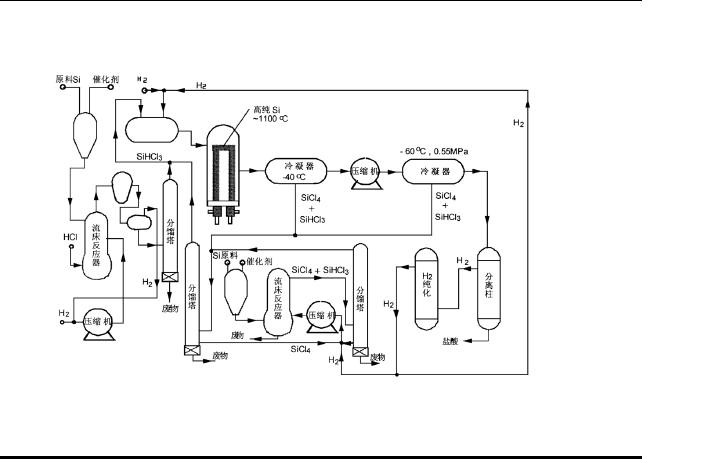

多晶硅生产流程是什么_单晶硅与多晶硅的区别

多晶硅生产工艺流程

关于多晶硅生产工艺流程的简单介绍

多晶硅栅(Poly-Si Gate)

多晶硅的用途包括哪些

多晶硅栅耗尽效应简述

多晶硅栅工艺的制造流程

多晶硅栅工艺的制造流程

评论