本文将介绍:关于数字产品中电源轨噪声如何影响数字系统中时钟抖动。

背景

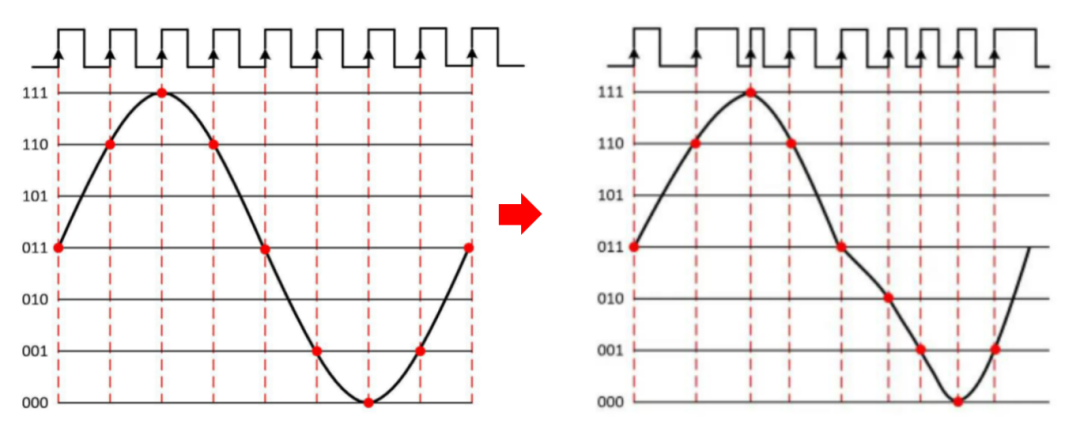

在数字电路中,一串二进制的信号流是通过电压(或电流)的波形来表示。然而,自然界的信号实际上都是vwin 的,而非数字的,所有的信号都受噪音、扭曲和损失影响。信号完整性考虑的问题主要有振铃(ringing)、串扰(crosstalk)、接地反弹、扭曲(skew)、信号损失和电源供应中的噪声。--摘至于维基百科(信号完整性)。

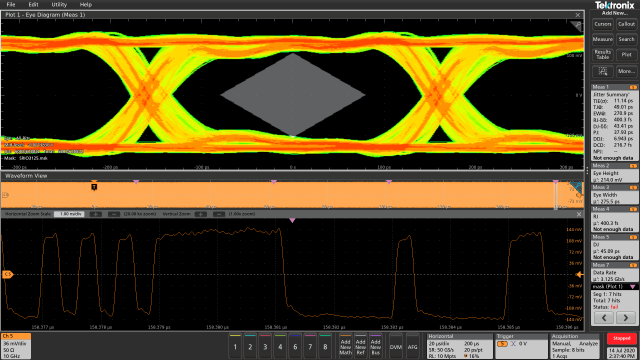

精准的周期性采样时钟是确保数字系统进行正确通信的前提。如果时钟信号发生了偏移,将引起传输的数字信号流发生变化,比如造成时延、误码等等。在高速数字系统中,随着时钟速率迈入GHz级,首要目标是保证信号完整无失真地从源端传送到接收端,往往电源完整性不佳就会影响时钟信号,进而引起信号完整性问题。

高速数字产品设计中不单单包含信号完整性问题,还包含电源完整性问题,而对数字系统中的电源轨噪声进行评估,将直接反映电源完整性的好坏,本文将介绍数字产品中电源轨噪声如何影响系统中时钟抖动。

数字产品中电源轨噪声与时钟抖动是关联的

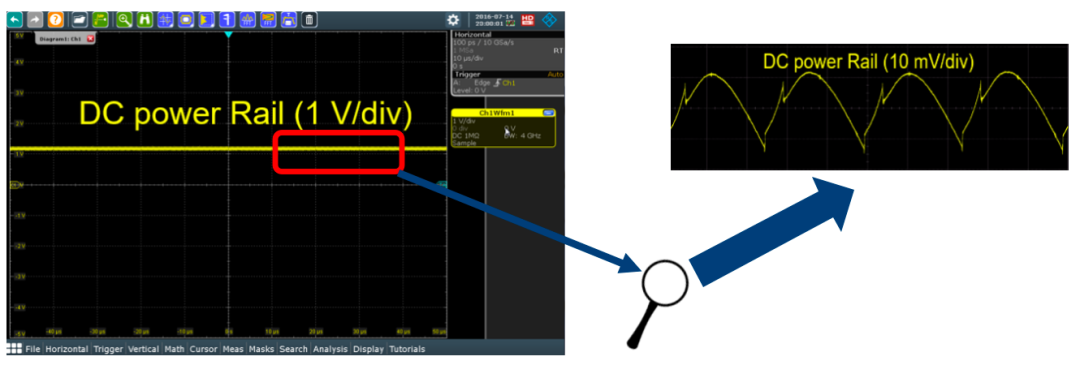

数字电路中的直流电压也就是电源轨波形往往看起来像是纯净平直,然而当我们通过示波器放大后发现其实不是,电源轨上是存在交流波动成分的。

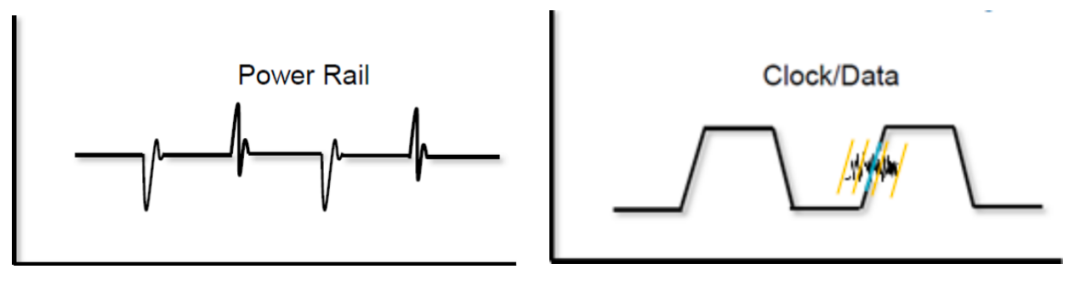

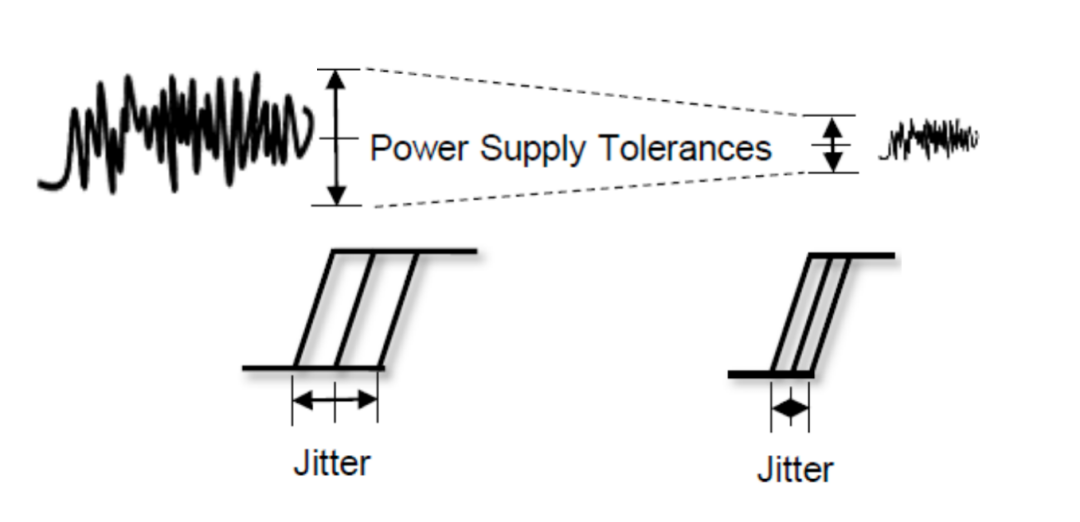

除了由开关电源引入的波动外,电源轨也会受耦合噪声的干扰,当PDN上发生振铃时,会影响芯片输出的时钟信号发生偏移,时钟信号上升沿发生的偏移就是我们俗称的抖动Jitter。

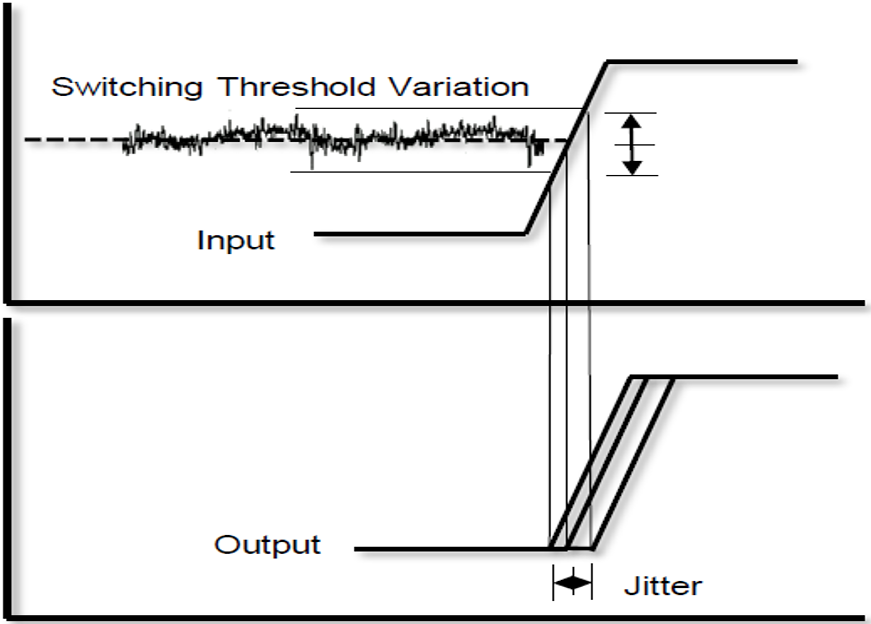

数字系统中的芯片通常由CMOS集成电路组成,其开关阈值会受电源轨的噪声影响而波动,进而引起了系统输出时钟或数据的抖动。

由下图可以看出,电源轨噪声波动的大小将对抖动大小带来影响,电源轨波动越小引起时钟信号的抖动Jitter也会越小。

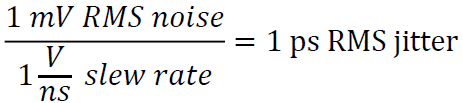

电源轨噪声与时钟信号斜率的比值决定了抖动的大小,电源轨噪声与抖动的关系可由以下公式描述:

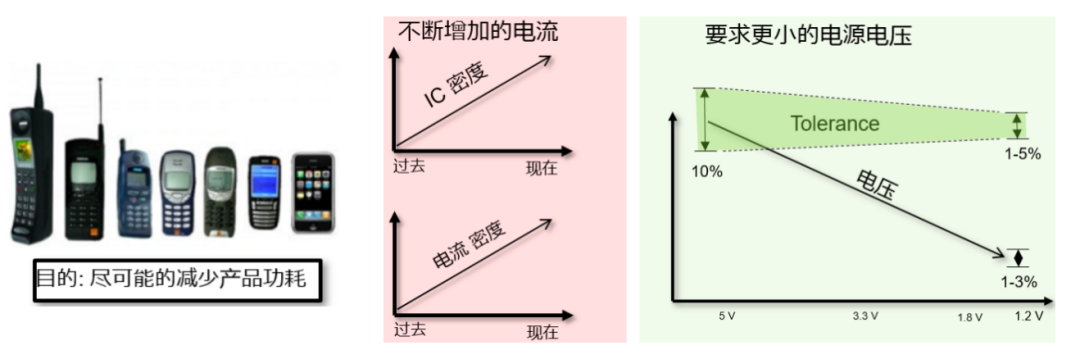

如果要对抖动的影响进行验证,就要准确测量电源轨噪声。但是在如今的电子产品中对电源完整性进行准确评估充满挑战。以最为常见的数字电子产品手机为例,随着手机发展的演变,体积越来越小,而内部IC集成度越来越高,电流密度越来越大,而功耗却在降低,从而要求输入电压也在降低(从典型的5V、3V减小至1V),甚至电压容限也在降低(10%减小到5%,甚至是1%)。这就会给电源轨测量造成挑战。

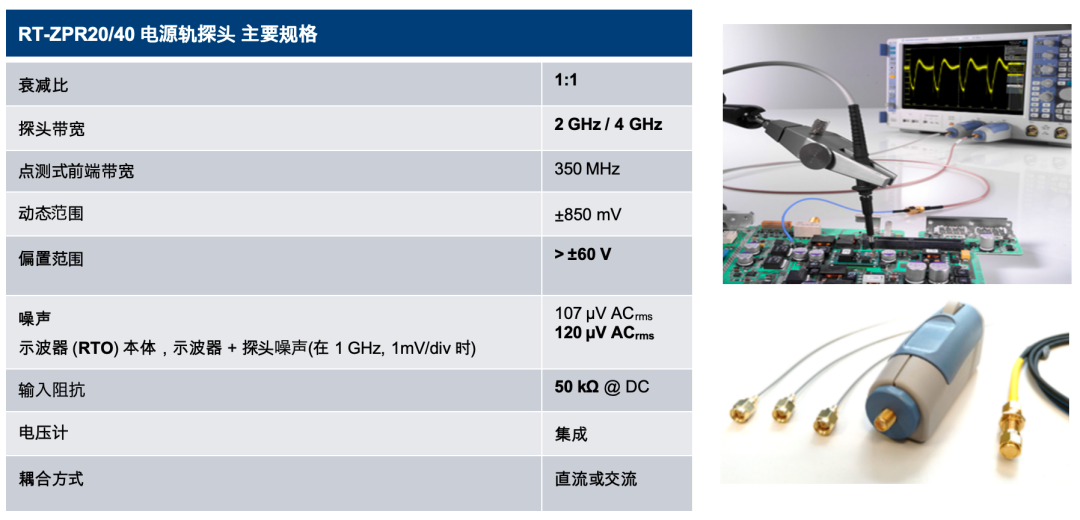

R&S RT-ZPR电源轨探头是应对这一挑战的最佳选择,它不仅具备极低的系统噪声(衰减比1:1),也具备2GHz/4GHz高带宽范围,可以测量更高频率范围的电源轨噪声。

以实际测量为例:使用RT-ZPR电源轨探头和传统RT-ZP1X纹波探头测试直流电压Vpp对比:

38 MHz带宽1:1无源探头RT-ZP1X会遗漏高频成分,不能显示尖峰的存在,从而低估Vpp测量值。但使用同样衰减比而带宽高达2 GHz的电源轨探头RT-ZPR20可以捕获并测量高频瞬态,还能拥有极低的噪声,不难看出针对高频瞬变需要高带宽电源轨探头才能测量出正确的Vpp值。

综上所述,电源轨信号并非是完全平直的,它会受到噪声干扰,进而影响系统时钟的稳定。当今数字产品中电源轨电压越来越低,同时要求的容限也越来越严苛,从而对测量电源轨信号造成挑战。罗德与施瓦茨的电源轨探头RT-ZPR充分应对这些挑战,可以进行准确测量 (高带宽,高灵敏度,低噪声和大偏置补偿)。下一期我们将用一个测量案例继续说明电源轨噪声对数字产品抖动的影响。

罗德与施瓦茨业务涵盖测试测量、技术系统、网络与网络安全,致力于打造一个更加安全、互联的世界。成立90 年来,罗德与施瓦茨作为全球科技集团,通过发展尖端技术,不断突破技术界限。公司领先的产品和解决方案赋能众多行业客户,助其获得数字技术领导力。罗德与施瓦茨总部位于德国慕尼黑,作为一家私有企业,公司在全球范围内独立、长期、可持续地开展业务。

-

噪声

+关注

关注

13文章

1120浏览量

47400 -

时钟抖动

+关注

关注

1文章

62浏览量

15922 -

数字电路

+关注

关注

193文章

1605浏览量

80577 -

电源轨

+关注

关注

1文章

34浏览量

5758

原文标题:【实践分享】|浅谈电源轨噪声对时钟抖动的影响(一)

文章出处:【微信号:罗德与施瓦茨中国,微信公众号:罗德与施瓦茨中国】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何减少SPDIF传输过程中时钟抖动

转:如何减少SPDIF传输过程中时钟抖动

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理

集成电源噪声抑制的时钟源简化FPGA系统的电源设计

电源噪声和时钟抖动对高速DAC相位噪声的影响分析及管理

时钟抖动(CLK)和相位噪声之间的转换

时钟抖动和相位噪声对采样系统的影响

高速ADC在低抖动采样时钟电路设计中的应用

数字产品中电源轨噪声如何影响系统中时钟抖动

数字产品中电源轨噪声如何影响系统中时钟抖动

评论