项目背景及可行性分析

应用背景

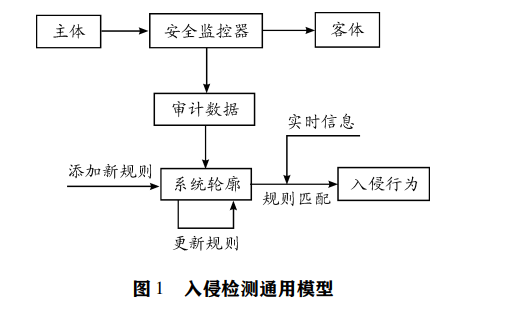

误用入侵检测系统作为当前主流的网络入侵检测系统,有判断准确性高、误报率低等特点,此类系统是建立在对过去各种已知网络入侵方法和系统缺陷知识的积累之上,根据对这些已知模式的检测来达到保障安全的目的。因此,模式库和模式匹配是误用入侵检测系统的核心。随着网络速度的迅速提高,误用入侵检测系统逐渐暴露其在性能上的致命缺陷:检测速率低、资源消耗大。尤其当入侵模式库不断增大时,此类软件系统更是难有较佳表现。因此,误用入侵检测系统在某些网络负载高的环境下不得不放弃对一些网络数据包的检测,这种策略严重影响了误用入侵检测系统在功能上的完整性。

误用入侵检测系统性能的主要瓶颈在于模式匹配引擎的效率上。模式匹配引擎根据入侵规则库中的规则模式对来自网络的数据包进行字符串模式匹配。在许多误用入侵检测系统中(如Snort入侵检测系统),这些用以描述入侵特征的字符串模式是以正则表达式形式给出的,将其作为判断规则的一部分存放于入侵模式规则库中。文献[1]指出在误用入侵检测系统的模式匹配中,正则表达式匹配占了CPU计算时间的90%以上。因此,本项目主要设计实现一个软硬结合的基于SNORT规则集的高速网络入侵检测系统。

研究现状

软件模式匹配引擎为达到较高的匹配效率,通常采用一些多模式匹配算法,文献[2]中作者指出,目前绝大多数的正则表达式匹配算法都是由GAC(Generalization of the Aho-Corasick)算法改进而来。文献[3]中给出了GAC算法设计细节。此类软件多模式匹配算法在由NFA(Nondeterministic Finite Automata)构建DFA(Deterministic Finite Automata)的过程中,状态机的状态数成指数级增长,因此增大了对内存等硬件资源的消耗,其结果是制约了此类系统所能匹配的正则表达式的规模,并且在无法增大规模的同时也降低了系统的性能。

在硬件模式匹配引擎的设计上,目前主要采用NFA和DFA两类模式匹配的方法,文献[4]中,作者应用DFA理论提出了一种新的结构,并通过压缩编码的方式来提高密度;文献[5]的作者依据图论算法对多状态转移进行合并,将DFA转化成,从而减小了95%的存储器占用。但这些利用DFA理论的方法都不可避免面临着硬件资源有限的难题,由于相对NFA来说,DFA实现中的状态数成指数级增长,这使得目前现有的FPGA硬件很难满足大规模正则表达式匹配的任务。文献[6]首次提出了一种利用NFA机制实现的基于FPGA硬件的正则表达式匹配引擎,该引擎可以每周期匹配一个字符,并采用模块化设计思想给出了几种基本模块的设计方法。本项目中的基于SNORT规则集中的正则表达式规则模式匹配引擎(硬件加速)部分,参考了此篇文章的思想并对其改进,采用模块化设计方法,设计实现一款数据流驱动的高速的硬件匹配引擎,解决了NFA引擎中的数据回溯问题。

主要内容

本项目针对传统软件入侵检测系统中存在正则表达式模式检测这一系统瓶颈问题,设计实现一个软硬结合的基于SNORT规则集的高速网络入侵检测系统。此系统主要由三部分组成,即基于SNORT规则集中的正则表达式规则模式匹配引擎(硬件入侵检测模式加速器)、底层硬件传输平台及软件(驱动和应用程序)的设计与实现。

关键技术和创新点

(1)面向正则表达式的多模式匹配硬件引擎的设计;

(2)基于PCI-E的CPU与FPGA的通信平台的设计;

(3)基于硬件的网络数据包的抓取;

(4)软件驱动程序的设计。

-

网络

+关注

关注

14文章

7553浏览量

88724 -

入侵检测

+关注

关注

0文章

57浏览量

14095

发布评论请先 登录

相关推荐

基于SNORT规则集的高速网络入侵检测系统

基于SNORT规则集的高速网络入侵检测系统

评论