一、晶振电路

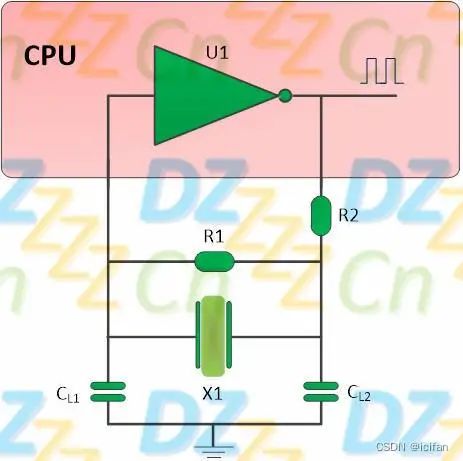

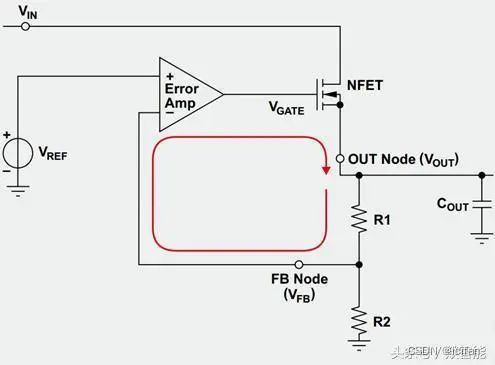

大多数电子工程师都见过单片机中如下图所示的形式,一般单片机都会有这样的电路。晶振的两个引脚与芯片(如单片机)内部的反相器相连接,再结合外部的匹配电容CL1、CL2、R1、R2,组成一个皮尔斯振荡器(Pierce oscillator)

上图中,U1为增益很大的反相放大器,CL1、CL2为匹配电容,是电容三点式电路的分压电容,接地点就是分压点。以接地点即分压点为参考点,输入和输出是反相的,但从并联谐振回路即石英晶体两端来看,形成一个正反馈以保证电路持续振荡,它们会稍微影响振荡频率,主要用与微调频率和波形,并影响幅度。X1是晶体,相当于三点式里面的电感

R1是反馈电阻(一般≥1MΩ),它使反相器在振荡初始时处于线性工作区,R2与匹配电容组成网络,提供180度相移,同时起到限制振荡幅度,防止反向器输出对晶振过驱动将其损坏。

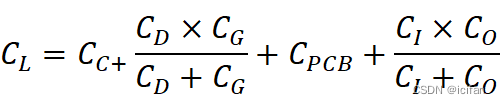

这里涉及到晶振的一个非常重要的参数,即负载电容CL(Load capacitance),它是电路中跨接晶体两端的总的有效电容(不是晶振外接的匹配电容),主要影响负载谐振频率和等效负载谐振电阻,与晶体一起决定振荡器电路的工作频率,通过调整负载电容,就可以将振荡器的工作频率微调到标称值。

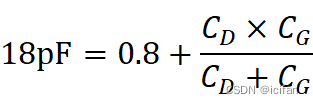

负载电容的公式如下所示:

CL=CC+CD×CGCD+CG+CPCB+CI×COCI+CO

其中,CS为晶体两个管脚间的寄生电容(Shunt Capacitance)

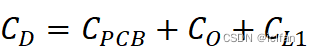

CD表示晶体振荡电路输出管脚到地的总电容,包括PCB走线电容CPCB、芯片管脚寄生电容CO、外加匹配电容CL2,即

CD=CPCB+CO+CL1

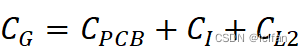

CG表示晶体振荡电路输入管脚到地的总电容,包括PCB走线电容CPCB、芯片管脚寄生电容CI、外加匹配电容CL1,即

CG=CPCB+CI+CL2

一般CS为1pF左右,CI与CO一般为几个皮法,具体可参考芯片或晶振的数据手册

(这里假设CS=0.8pF,CI=CO=5pF,CPCB=4pF)。

比如规格书上的负载电容值为18pF,则有

18pF=0.8+CD×CGCD+CG

18pF=0.8+CD2=0.8+CG2

则CD=CG=34.4pF,计算出来的匹配电容值CL1=CL2=25pF

二、LDO选型

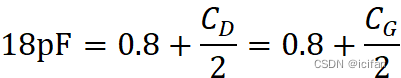

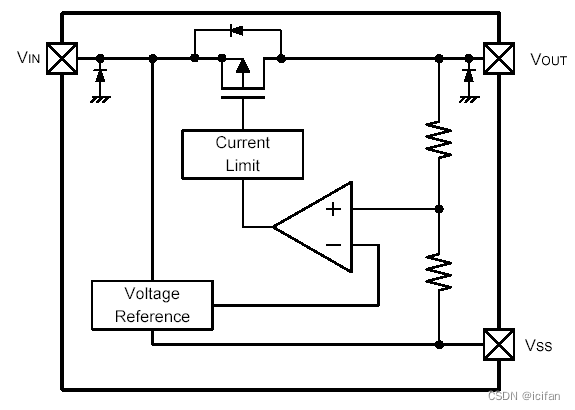

1.LDO工作原理

LDO核心架构:P-MOS+运放

LDO工作原理就一句话:通过运放调节P-MOS的输出。运放控制P-MOS的打开程度。

LDO内部产生一个基准电压,作为运放的反向电压,将LDO的输出电压通过分压作为运放的正向输入电压。运放的输出去控制P-MOS管的工作状态。

P-MOS,相当于一个压控的可变电阻。

P-MOS处于线性电阻区,可看成一个压控可变电阻。输入的VIN电压,经过这个P-MOS管后变为输出电压,这里P-MOS管的作用为将输入电压通过P-MOS的线性电阻区,将电压动态衰减值VOUT电压。

LDO的负反馈回路

2.输入电压

最小的输入电压 VIN 必须大于 VOUT + VDO。需要注意,这与器件 Datasheet 中所给出的输入电压最小值无关。

3.效率

LDO的工作原理是通过负反馈调整输出电流使输出电压保持不变。LDO是一个降压型的DC/DC 转换器,因此Vin > Vout,它的工作效率:

η= Pout/Pin=(Iout×Vout)/(Iin×Vin)

η= (Iout×Vout)/((Iout+Ignd)×Vin)

LDO的工作效率一般在60~75%之间,静态电流小的效率会好一些。在忽略 LDO 静态电流的情况下,可以采用 VOUT / VIN 式子来计算效率。

4.功耗

计算例子见 附录一:LDO使用之热阻考虑。

Pd=(Vin-Vout)×Iout+Vin×Ignd

式中,Ignd:接地电流有时也记作Iq:静态电流。因为Ignd很小,所以一般估算为:

Pd=(Vin-Vout)xIout。

最大允许功耗(PDMAX)是最大环境温度(TA),最大允许结温(TJMAX)(+125°C) 和结点到空气间热阻(RθJA) 的函数。对于安装在典型双层FR4 电解铜镀层PCB板上的5引脚SOT-23A封装器件,其(RθJA)约为250°C/Watt。

PDMAX=(TJMAX-TA)/RθJA

将计算出的Pd代入上式,可求出 TJ,然后将TJ与datasheet给出的最大允许节温相比较,如果TJ

一般电源LDO允许的最大节温为125°C。所以,可以计算出PDMAX,满足PD<=PDMAX即可。

************

热阻的计算:

RθJA = RθJC +RθCS + RθSA

其中:RθJA为LDO结到周围环境的热阻

RθJC为LDO结到表面(封装)的热阻

RθCS为LDO表面(封装)到散热片的热阻

RθSA为LDO散热片到周围环境的热阻

************

5.电源抑制比PSRR

用最通俗的话解释就是,电源的输入与输出的纹波的比值,PSRR越高,表明LDO对于纹波的抑制效果更好,打个比方输入纹波为10mV,PSRR 为75dB,那么输出的纹波幅度为1.8uV(纹波降低约5623倍)。

6.线性调整率 Line Regulation

定义: 又称源效应或电网调整率,是指输出电压随输入电压的线性变化的波动,条件是全满载。(输入电压在额定范围内变化时,输出电压之变化率. )

Line Regulation(+)=(Vmax-Vnor)/Vnor

Line Regulation(-)=(Vnor-Vmin)/Vnor

Line Regulation=(Vmax-Vmin)/Vnor

Vnor:输入电压为常态值,输出为满载时之输出电压.

Vmax:输入电压变化时之最高输出电压.

Vmin:输入电压变化时之最低输出电压.

说明:如只是简单计算Line Regulation ,Vnor可用Vrated即输出电压标称值。

检验方法:输出全满载,在输入电压全范围内测量输出电压,观察示波器及万用表,记下输入电压全范围变化时的输出电压最大和最小值,利用上述公式求得线性调整率。

7.负载调节率 (Load Regulation)

定义: 又称负载效应,是指输出电压随负载变化的波动,条件是输入为额定电压。电源负载的变化会引起电源输出的变化,负载增加,输出降低,相反负载减少,输出升高。好的电源负载变化引起的输出变化减到最低,通常指标为3%~5%。

Line Regulation(+)=(Vml-Vhl)/Vhl

Line Regulation(-)=(Vhl-Vfl)/Vhl×100%

Line Regulation(%)=(Vml-Vfl)/Vhl×100%

Vml:最小负载时之输出电压

Vfl:满载时之输出电压

Vhl:半载时之输出电压

说明:如只是简单计算Load Regulation,Vhl可用Vrated即标称电压来代替.

检验方法:输入为额定电压,分别在负载为空载、全满载两种输出情况下,负载反复投切。观察示波器及万用表,测量输出电压幅值和波形,记下投切过程中的输出电压最大和最小值,利用上述公式求得负载调整率。例如某5V直流稳压电源的输出电流从0增加到最大电流1A,它的输出电压从5.00V降到了4.50V,降落值0.5V除以标称输出电压5V,得到10%,这就是该电源的负载调整率。

8.静态电流

静态电流往往在我们设计超低功耗产品时重点关注,比如,一款蓝牙设备,整机待机状态电流仅为1.5uA,但LDO静态电流如果高达70uA甚至更高将严重影响待机时间,我们必须选择静态电流在uA级别的LDO来满足设计要求。

9.噪声

噪声是衡量一个LDO性能的最关键参数,噪声可以通过两种手段降至最低,第一,选择本底噪声很低的LDO型号,第二在电路设计中将可能引入的电源噪声降至最低。但我们选型和设计中没必要吹毛求兹,选择能够满足电路要求的LDO即可。选择合适的才是最好的。

10.输出电容器

输出电容器的 ESR 对于器件的稳定性来说至关重要。有的 LDO 声明采用具有较高 ESR 的钽电容器,那么一定不要选用极低 ESR 的陶瓷电容器。然而有的 LDO 能够在未采用输出电容器或者只采用了低 ESR 的陶瓷类型的输出电容器,稳定性就可以保证。曾经看到有的资料据此认为,“可以确认,可在采用任何类型的输出电容器的情况下具有稳定的工作特性。”---这点我一直不敢苟同,实在值得商榷。作为设计人员,应严格按照具体 LDO 器件的 Datasheet 选择最为合适类型的输出电容器。

11.反向泄漏保护

在某些 LDO 的输出端上的电压高于输入端的电压的特殊应用中,反向泄漏保护可以有效防止电流从 LDO 的输出端流向输入端。如果忽视这点,这种反向泄漏会损坏输入电源,特别是当输入电源为电池的时候,尤其需要重视。

如果负载端为 RF、音频或其他对噪声敏感的应用,那么应选择具有高电源纹波抑制(PSRR)的 LDO,以实现对输入电源的抗噪性,以及低输出噪声(〈50uVms)。有的 LDO 具有一个用来增加电容以降低输出噪声的旁路(BP)引脚,亦可起到一定作用。

LDO应用

LDO的应用电路十分简单方便,它工作时仅需要二个作输入、输出电压退耦降噪的陶瓷电容器。

Vin和Vout的输入和输出滤波电容器应当选用宽范围、低等效串联电阻(ESR)、低价陶瓷电容器,使LDO在零到满负荷的全部量程范围内具有良好的稳压效果。一些LDO有一个“Bypass”管脚,由它连接一个小的电容器,可以进一步降低噪音。

LDO的工作效率一般在60~75%之间,静态电流小的效率会好一些。

输入电压,压差电压(VDO)

线性稳压器件的压差电压常常被误解。正如上面讨论的,VI和VO之间的电压差是通过线性稳压器后的压降。对于固定的负载电流,线性稳压器的输入与输出的电压降越小功率散耗就越低。压差电压是LDO稳压器技术指标中定义的能够稳压工作时VI和VO之间最小的差值又称为VDO。

三、DC-DC

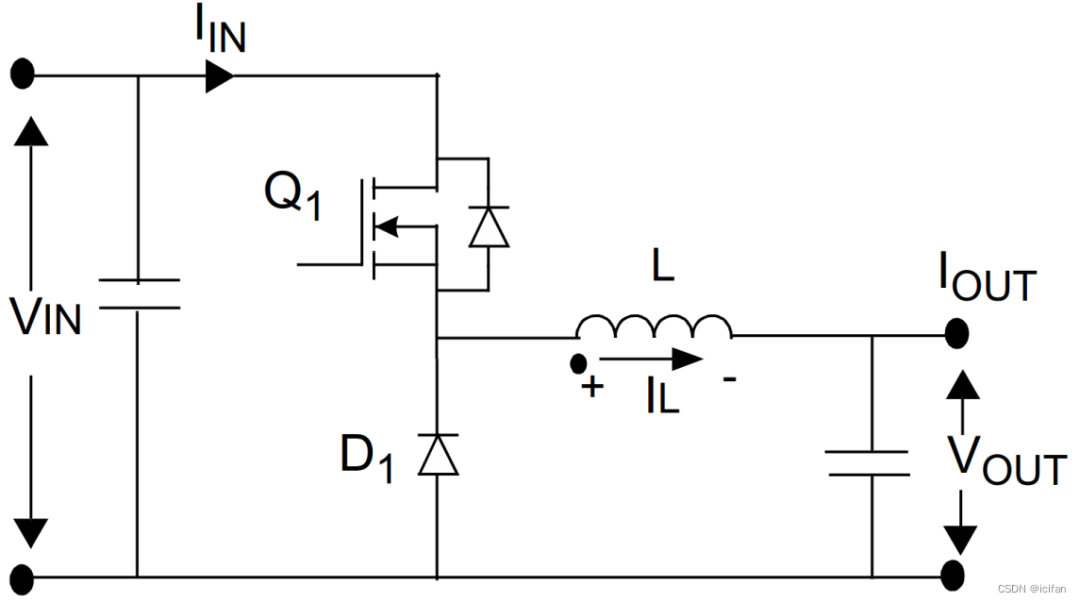

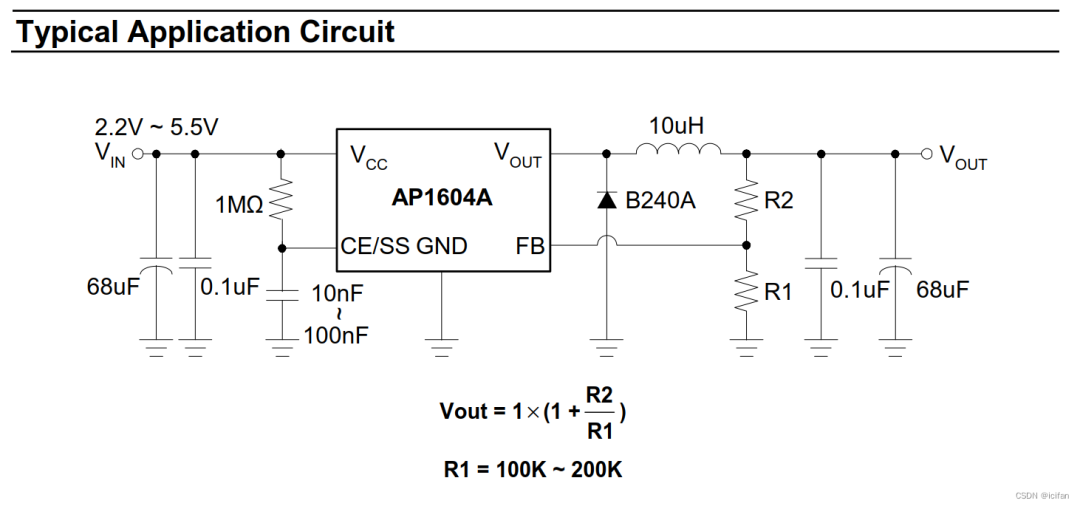

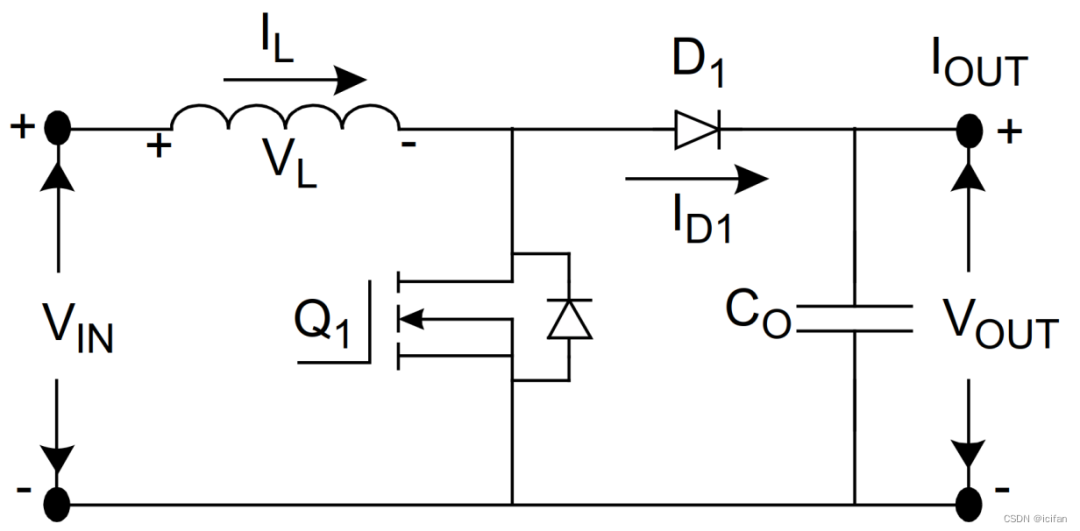

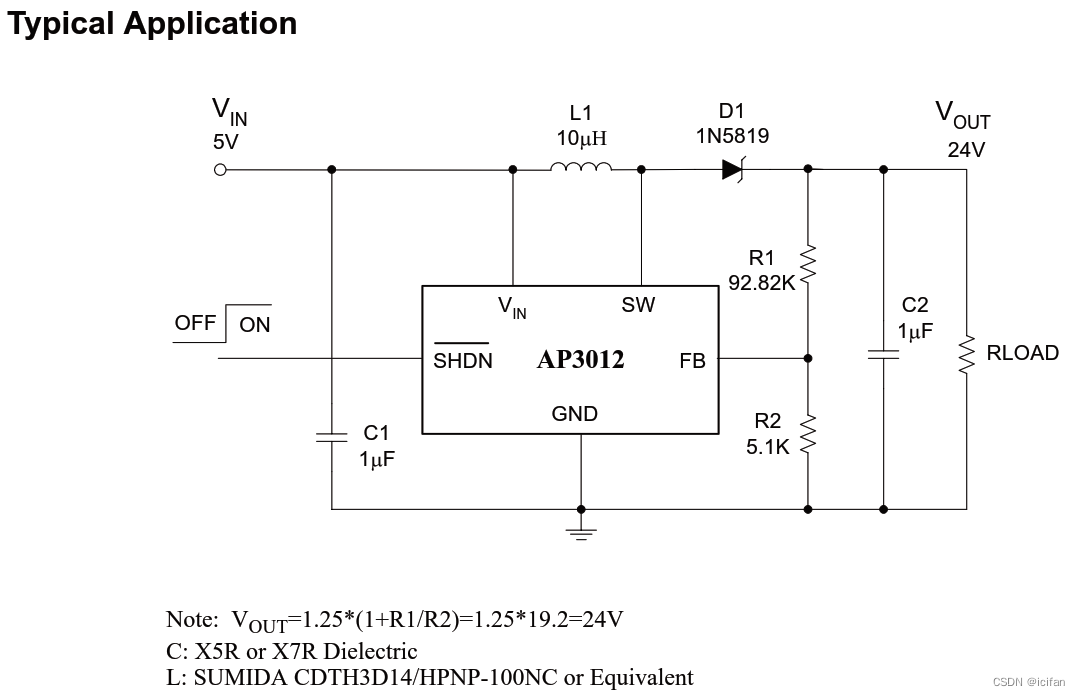

2.升压转换器-Boost Converter

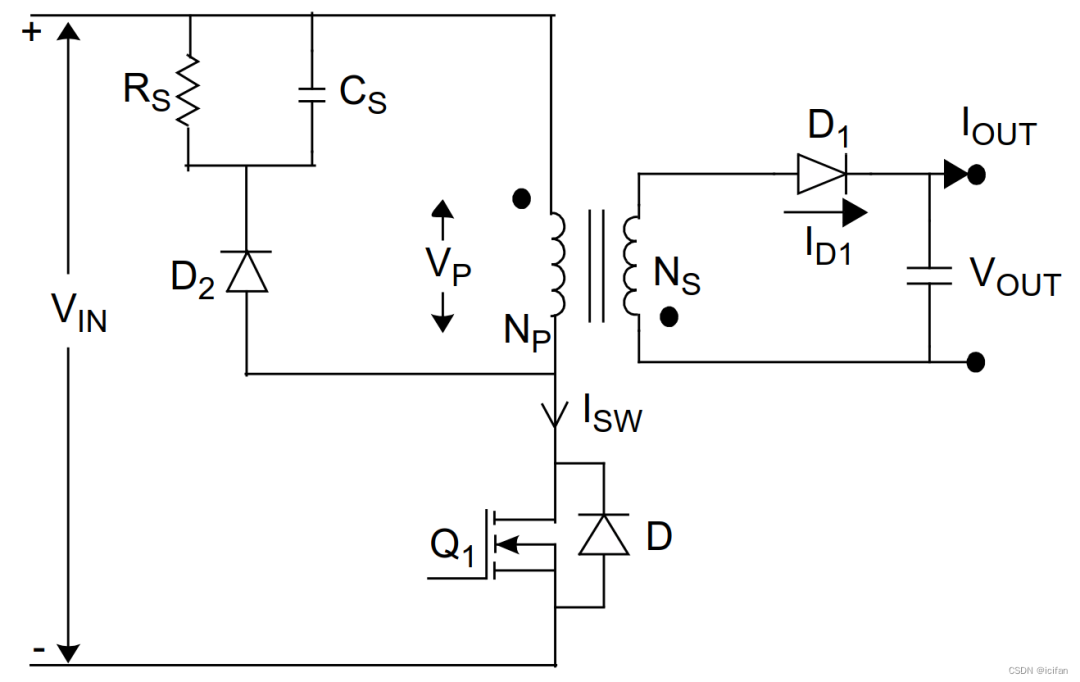

3.反激转换器-Flyback Converter

四、通讯接口

1.USB 总线

现USB标准中,按照速度等级和连接方式分为以下七种版本。注意USB-IF当前正式的主版本号只有USB 2.0和USB 3.2两个。

2.UART

RS232:传输速率一般不超过20Kbps,速率低,抗干扰能力差,RS-232C能传输的最大距离不超过15m(50英尺)。

RS422:定义了一种平衡通信接口,将传输速率提高到10Mbps,传输距离延长到4000英尺(速率低于100Kbps时),并允许在一条平衡总线上连接最多10个接收器。RS-422是一种单机发送、多机接收的单向、平衡传输规范,被命名为TIA/EIA-422-A标准。

RS485:增加了多点、双向通信能力,即允许多个发送器连接到同一条总线上,同时增加了发送器的驱动能力和冲突保护特性,扩展了总线共模范围,后命名为TIA/EIA-485-A标准。最高传输速率10Mbps,抗干扰能力强,可以传距离1.5km。

平衡双绞线的长度与传输速率成反比,在100Kbps速率以下,才可能使用规定最长的电缆长度。只有在很短的距离下才能获得最高速率传输。一般100米长双绞线最大传输速率仅为1Mbps。

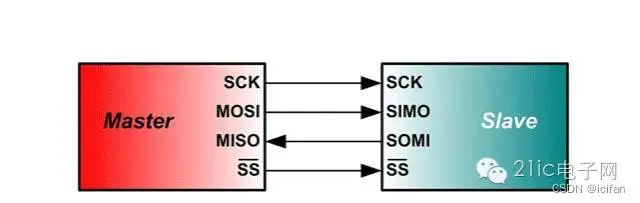

3.SPI

全双工通信,传输速率可达几Mbps水平,比I2C快。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。也是所有基于SPI的设备共有的,它们是SDI(数据输入)、SDO(数据输出)、SCLK(时钟)、CS(片选)。

(1)SDI – Serial Data In,串行数据输入;

(2)SDO – Serial Data Out,串行数据输出;

(3)SCLK – Serial Clock,时钟信号,由主设备产生;

(4)CS – Chip Select,从设备使能信号,由主设备控制。

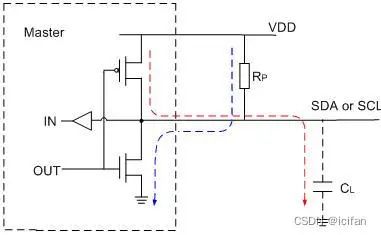

4.I2C

半双工,只有2根线。数据线和时钟线。

标准速度:100kbps

快速模式:400kbps

高速模式:3.4Mbps

在大多数情况下,由于I2C接口采用Open Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的,如图所示。

因为I2C总线在空闲时必须拉高,只有是高的才能拉成低的,所以这是之所以规定空闲时必须为高的一个原因,要是保持“低”的话,那是不可能成为“多主”总线的。

其实I2C总线接口在工作时只会检测高低电平,他不会在乎有无上拉电阻的问题,所以总线必须满足时序要求。

上拉电阻的大小,会牵扯到两个问题,一个是功耗,一个是速度问题,两者是一个矛盾体。如果你想尽量提高速度,那么就牵涉到总线电容的问题,其实很容易理解,上拉电阻与总线的电容形成了RC,高速时将直接影响通讯!因为总线拉高时有个充电时间以及高电平的阀值,如果还没有充电到足以保证从器件可以识别的高电平的阀值时主器件就以为完成了一个总线动作的话,那么通讯肯定是不能进行的!

如果你想尽可能降低功耗,那么就要尽可能增大电阻以最大可能的减小电路各部分的消耗电流从而实现整体降低功耗!但不可能无限大,否则充电时间你会受不了的!

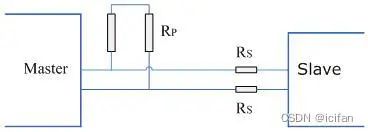

I2C协议还定义了串联在SDA、SCL线上电阻Rs。该电阻的作用是,有效抑制总线上的干扰脉冲进入从设备,提高可靠性。这个电阻的选择一般在100~200ohm左右。当然,这个电阻并不是必须的,在恶劣噪声环境中,可以选用。

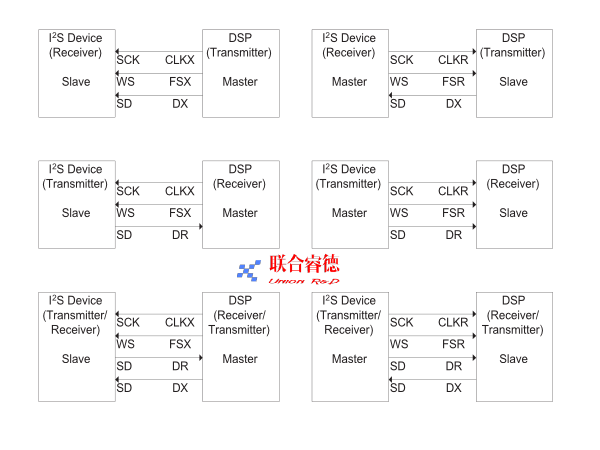

5.I2S

I2S有4个主要信号:

串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。

帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是左声道的数据,为“0”则表示正在传输的是右声道的数据。LRCK的频率等于采样频率。

串行数据SDATA,就是用二进制补码表示的音频数据。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。在DAC内部的delta-sigma调制器以及数字滤波器都需要用到这个时钟,大部分的DAC可以使用内部的振荡器产生这个时钟,在某些要求较高的场合,例如HIFI音响系统等,需要使用一个额外的高质量的时钟用以获得最好的性能。这时候就需要用到MCLK信号了。切记,MCLK并不是必须的。可有可无,看设计要求。

6.Ethernet

也就是通常的网速。

早期的以太网传输速率只有10Mbps。

百兆网:理论上最大100Mbps。

千兆网:理论上最大1Gbps。

7.SD总线

最高能达10Mbps。

8.SATA接口

SATA1.0:理论传输速度是150MB/s(或者1.5Gb/s),实际也就30MBps。

SATA2.0:300MBps,即3Gbps。实际也就80MBps。

SATA3.0:600MBps,即6Gbps。

eSATA:理论传输速度可达到1.5Gbps或3Gbps。

9.PCI总线

PCI:32位,33MHz时钟频率,数据传输速率 = 33 MHz * 32 bits / 8 bits/byte = 132 MBps ≈ 1.056 Gbps。

PCI 2.1:64位,66MHz时钟频率来说:数据传输速率 = 66 MHz * 64 bits / 8 bits/byte = 528 MBps ≈ 4.224 Gbps。

10.CAN总线

CAN,全称为“Controller Area Network”,即控制器局域网,是国际上应用最广泛的现场总线之一。

直接通信距离最远可达10km(速率4Kbps以下)。

通信速率最高可达1MB/s(此时距离最长40m)。

可以多主方式工作,网络上任意一个节点均可以在任意时刻主动地向网络上的其他节点发送信息,而不分主从,通信方式灵活。

网络上的节点可分成不同的优先级,可以满足不同的实时要求。

采用非破坏性位仲裁总线结构机制,当两个节点同时向网络上传送信息时,优先级低的节点主动停止数据发送,而优先级高的节点可不受影响地继续传送数据。

可以点对点,一点对多点及全局广播几种传送方式接收数据。

11.PCI-e

PCI Express 总线频率 2500 MHz,这是在 100 MHz 的基准频率通过锁相环振荡器(Phase Lock Loop,PLL)达到的。

串行总线带宽(MB/s) = 串行总线时钟频率(MHz) * 串行总线位宽(bit/8 = B) * 串行总线管线 * 编码方式 * 每时钟传输几组数据(cycle)

PCI Express x1 总线位宽是 1位,总线频率 2500 MHz,串行总线管线是 1 条,每时钟传输 2组数据,编码方式为 8b/10b,它的带宽为 476.84 MB/s,即 3814.7 Mbps。(带宽是 PCI 的 3.75 倍。)

公式是 2500000000(Hz) * 1/8(bit) * 1(条管线) * 8/10(bit) * 2(每时钟传输2组数据) = 500000000 B/s = 476.8371582 MB/s,即 3814.6972656 Mbps。

下面给出其它类型组合的带宽。

PCI Express x2 的带宽为 953.68 MB/s,即 7629.4 Mbps。(此模式仅用于主板内部接口而非插槽模式)

PCI Express x4 的带宽为 1907.36 MB/s,即 15258.9 Mbps。

PCI Express x8 的带宽为 3814.72 MB/s,即 30517.8 Mbps。

PCI Express x16 的带宽为 7629.44 MB/s,即 61035.5 Mbps。(带宽是 AGP 8X 的 3.75 倍。)

PCI Express x32 的带宽为 15258.88 MB/s,即 122071 Mbps。

五、典型运放应用

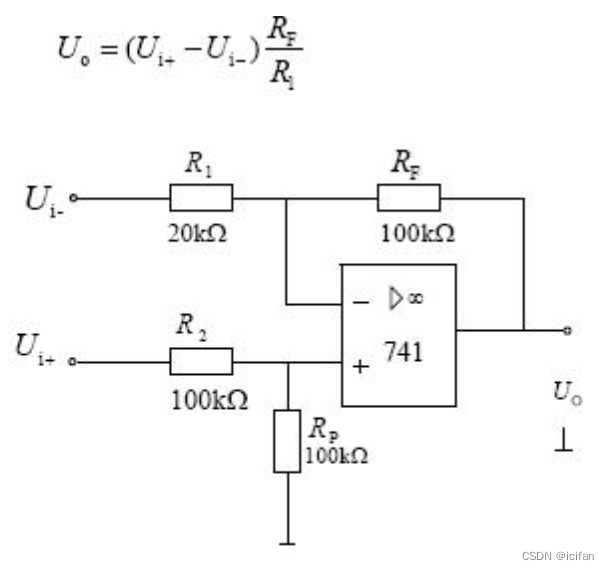

1.差分放大器

差分放大电路的输入信号是从集成运放的反相和同相输入端引入,如果反馈电阻RF等于输入端电阻R1,输出电压为同相输入电压减反相输入电压,这种电路也称作减法电路。

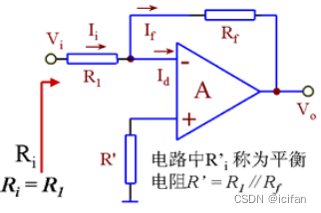

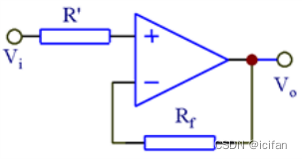

2.反相放大器

基本电路、电压并联负反馈输入端虚短、虚断。运放的平衡电阻是用来平衡运放的两个输入端子的失调电流的,使得两个端子的电压平衡,从而使运放的偏置电流不会产生附加的失调电压。

Vo = -Vi*(Rf / R1)

特点:

反相端为虚地,所以共模输入可视为0,对运放共模抑制比要求低

输出电阻小,带负载能力强

要求放大倍数较大时,反馈电阻阻值高,稳定性差。

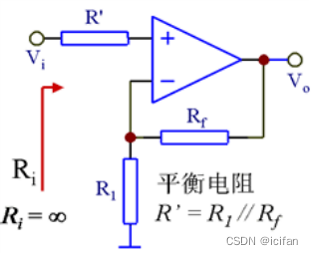

3.同相放大器

1. 基本电路:电压串联负反馈

特点:

输入电阻高,输出电阻小,带负载能力强

V-=V+=Vi,所以共模输入等于输入信号,对运放的共模 抑制比要求高

4.电压跟随器

输入电阻大输出电阻小,能真实地将输入信号传给负载而从信号源取流很小 。

5.运算典型参数

输入偏置电流 (Input Bias Current):这是流入或流出输入引脚的最小电流。如果在运放前级处理低电流,这一点非常重要。此外,它也可以作为应力导致性能偏离的指标,因为这种类型的漏电流对辐射等应力非常敏感。

输入失调电流 (Input Offset Current):这是两个输入的偏置电流之间的差值。

输出失调电压 (Output Offset Voltage):这是当输入设置为某个固定参考值(通常是地或中间电压)时,其理想直流输出与实际直流输出之间的差值。

输入失调电压 (Input Offset Voltage):这是必须施加到输入端的电压,以将输出恢复到理想水平,即vwin

地或中间电压。

转换速率 (Slew Rate):这是输出电压变化的最大速率。这在使用运放处理突变信号(如时钟或图像传感器输出)时尤为重要。

带宽 (Bandwidth):这表示频率响应,通常以闭环大/小信号3dB带宽或增益带宽积表示。在电压反馈运放中,闭环增益与该增益下的3dB闭环带宽的乘积是一个常数。

开环增益 (Open-Loop Gain):这是运放在没有正反馈或负反馈时的增益。

共模抑制比 (CMRR):如果施加差分输入电压,理想情况下输出不应受共模电压的影响。CMRR是共模增益与差模增益的比值。

电源抑制比 (PSRR):这表示输出不受电源电压变化影响的能力。PSRR是电源电压变化与输出电压变化的比值。

输入共模电压范围 (Input Common-Mode Voltage Range):这是共模输入电压的范围,如果超过这个范围,会导致输出信号的总谐波失真超过指定的最大或最小值。

输出电压摆幅 (Output Voltage Swing):这是在不发生波形削波的情况下,可以获得的相对于零的最大正或负输出。

静态电流 (Quiescent Current):这是通常在输出禁用或输出电流接近零时消耗的电源电流。这个参数是设备变化的一个重要全局指标。

输入电压噪声 (Input Voltage Noise):这是反映在输入引脚的理想电压源的内部噪声电压,通常以每赫兹平方根的伏特为单位表示。通常是噪声频率特性曲线在闪烁噪声之后和白噪声开始时的一个点。这个值在1nV/√Hz到20nV/√Hz之间变化。

输入电流噪声 (Input Current Noise):这与前一个类似,但以输入端的电流形式表示。电流噪声比电压噪声变化更大,取决于输入结构。它可以在0.1fA/√Hz到几个pA/√Hz之间变化。

EMC即电磁兼容(Electromagnetic Compatibility),是指电子、电气设备或系统在预期的电磁环境中,按设计要求正常工作的能力,也是电子、电气设各或系统的一项重要的技术性能。

EMC存在的三个要求:干扰源、耦合途径、敏感装置。

电磁干扰有传导干扰和辐射干扰两种。

传导干扰是指通过导电介质把一个电网络上的信号耦合(干扰)到另一个电网络。

辐射干扰是指干扰源通过空间把其信号耦合(干扰)到另一个电网络。

传导、辐射、骚扰和干扰

在进行PCB的EMC设计时,常采用的措施有减少干扰源的强度、切断耦合路径和提高设备的抗干扰能力。

在进行信号完整性与电源完整性设计时,降低信号的过冲、下冲、反射,减缓信号上升沿和下降沿的速率,降低电源的目标阻抗等,也都是为了减少EMI辐射的强度,减少EMI包含的频谱分量。

1.EMI(Electromagnetic Interference)——电磁干扰

即处在一定环境中的设备或系统正常运行时,不应产生超过相应标准所要求的电磁能量于扰。这样的电磁干扰有:

电源线传导骚扰(CE)测试;

信号、控制线传导骚扰(CE)测试;

辐射骚扰(RE)则试;

谐波电流(Harmonic)测试;

电压波动和闪烁(Fluctuation and Flicker)测试。

1. EMI测试

符合CISPR25(对应国标为GB18655)、CISPR12(对应国标为GB14023)、SAEJ551/5(对应国标为GB18387)标准的辐射骚扰测试;

符合CISPR25(对应国标为GB18655)标准的传导耦合/瞬态发射骚扰测试。

2.EMS(Electromagnetic Susceptibility)——电磁抗敏感度

即处在一定环境中的设各或系统正常运行时,设各或系统能承受各种类型的电磁能量干扰。这种电磁能量干扰主要有:

静电放电(ESD)抗扰度测试;

电源端口的电快速瞬变脉冲群(EFT/B)抗扰度测试;

信号线、控制线的电快速瞬变脉冲群(EFT/B)抗扰度测试;

电源端口的浪涌(SURGE)和雷击测试;

信号线、控制线的浪涌(SURGE)和雷击测试;

壳体辐射抗扰度(RS)测试;

电源端口的传导抗扰度(CS)测试;

信号线、控制线的传导抗扰度(CS)测试;

电源端口的电压跌落与中断测试(DIP)。

1. EMS测试

符合1507637-1/2标准规定的电源线传导耦合/瞬态抗扰度测试;

符合1507637-3标准规定的传感器电缆与控制电缆传导耦合/瞬态抗扰度测试;

符合150114527(对应国标为GB17619)标准规定的射频传导抗扰度测试;

符合15011452-2(对应国标为GB17619)标准规定的辐射场抗扰度测试;

符合15011452-3(对应国标为GB17619)标准规定的横电磁波(TEM)小室的辐射场抗扰度测试;

符合15011452-4(对应国标为GB17619)标准规定的大电流注入(BCI)抗扰度测试;

符合15011452-5(对应国标为GB17619)标准规定的带状线抗扰度测试;

符合15011452-6(对应囟标为GB17619)标准规定的三平板抗扰度测试;

符合15010605标准的静电放电抗扰度测试。

对于汽车及车载电子设备,由于其电磁环境与供电环境相对特殊,其EMC测试也相对特殊,但也可分为EMI测试和EMS测试两大类。它更加突出ISO、CISPR和SAEJ标准的重要性,具体的FMC测试项目有两个。

EMC设计不能像硬件电路设计、结构设计、软件设计等设计活动可以单独存在,它依附于产品的其他设计活动中。如果一定要对EMC设计活动进行分类,那么主要包括:

1)产品的EMC标准和需求分析;

2)产品机械结构构架的EMC设计,包括产品中的电缆部分的设计;

3)电路原理图的EMC设计;

4)PCB的EMC设计;

5)EMC测试过程中出现问题的改进

3.ESD防护

1)传导性ESD防护

对静电电流在电路中防护主要使用一些保护器件,在敏感器件前端构成保护电路,引导或耗散电流。此类保护器件有:陶瓷电容,压敏电阻,TVS管等。

2)辐射性ESD防护

对于静电产生的场对敏感电路产生影响,防护方法主要是尽量减少场的产生和能量,通过结构的改善增加防护能力,对敏感线路实施保护。对场的保护通常比较困难,在改良实践中探索出了一种叫做等位体的方法。通过有效地架接,是壳体形成电位相同体,抑制放电。事实证明此种方式有效易于实施。

防护静电的一般方法有许多,包括减少静电的积累;使产品绝缘,防止静电发生;对敏感线路提供支路分流静电电流;对放电区域的电路进行屏蔽;减少环路面积以保护电路免受静电放电产生的磁场的影响。有针对直接放电的,也有针对关联场的耦合。

七、信号完整性SI-Signal Integrity

信号完整性是指信号在信号线上的质量。

信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。主要的信号完整性问题包括反射、振荡、地弹、串扰等。

常见信号完整性问题及解决方法问题

1.反射Reflection

反射就是在传输线上的回波。信号功率(电压和电流)的一部分传输到线上并达到负载处,但是有一部分被反射了。如果源端与负载端具有相同的阻抗,反射就不会发生了。

源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负,反之,如果负载阻抗大于源阻抗,反射电压为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素的变化均会导致此类反射。

2.串扰Crosstalk

串扰是两条信号线之间的耦合,信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

3.过冲Overshoot和下冲Undershoot

过冲就是第一个峰值或谷值超过设定电压——对于上升沿是指最高电压而对于下降沿是指最低电压。下冲是指下一个谷值或峰值。过分的过冲能够引起保护二极管工作,导致过早地失效。过分的下冲能够引起假的时钟或数据错误(误操作)。

4.振荡Ringing和 环绕振荡Rounding

振荡的现象是反复出现过冲和下冲。信号的振荡和环绕振荡由线上过度的电感和电容引起,振荡属于欠阻尼状态而环绕振荡属于过阻尼状态。信号完整性问题通常发生在周期信号中,如时钟等,振荡和环绕振荡同反射一样也是由多种因素引起的,振荡可以通过适当的端接予以减小,但是不可能完全消除。

5.地电平面反弹噪声和回流噪声

在电路中有大的电流涌动时会引起地平面反弹噪声(简称为地弹),如大量芯片的输出同时开启时,将有一个较大的瞬态电流在芯片与板的电源平面流过,芯片封装与电源平面的电感和电阻会引发电源噪声,这样会在真正的地平面(0V)上产生电压的波动和变化,这个噪声会影响其它元器件的动作。负载电容的增大、负载电阻的减小、地电感的增大、同时开关器件数目的增加均会导致地弹的增大。

由于地电平面(包括电源和地)分割,例如地层被分割为数字地、模拟地、屏蔽地等,当数字信号走到模拟地线区域时,就会产生地平面回流噪声。同样电源层也可能会被分割为2.5V,3.3V,5V等。所以在多电压PCB设计中,地电平面的反弹噪声和回流噪声需要特别关心。

6.时域Time Domain和频域Frequency Domain

时域(time domain)是以时间为基准的电压或电流的变化的过程,可以用示波器观察到。它通常用于找出管脚到管脚的延时(delays)、偏移(skew)、过冲(overshoot)、、下冲(undershoot)以及建立时间(settling times)。

频域(frequency domain)是以频率为基准的电压或电流的变化的过程,可以用频谱分析仪观察到。它通常用于波形与FCC和其它EMI控制限制之间的比较。

7.阻抗Impedance

阻抗是传输线上输入电压对输入电流的比率值(Z0=V/I)。当一个源送出一个信号到线上,它将阻碍它驱动,直到2*TD时,源并没有看到它的改变,在这里TD是线的延时(delay)。

8.建立时间Settling Time

建立时间就是对于一个振荡的信号稳定到指定的最终值所需要的时间。

9.管脚到管脚Pin-To-Pin的延时Delay

管脚到管脚延时是指在驱动器端状态的改变到接收器端状态的改变之间的时间。这些改变通常发生在给定电压的50%,最小延时发生在当输出第一个越过给定的阈值(threshold),最大延时发生在当输出最后一个越过电压阈值(threshold) ,测量所有这些情况。

10.偏移Skew

信号的偏移是对于同一个网络到达不同的接收器端之间的时间偏差。偏移还被用于在逻辑门上时钟和数据达到的时间偏差。

11.斜率Slew Rate

Slew rate就是边沿斜率(一个信号的电压有关的时间改变的比率)。I/O 的技术规范 (如PCI)状态在两个电压之间,这就是斜率(slew rate),它是可以测量的。

12.静态线Quiescent Line

在当前的时钟周期内它不出现切换。另外也被称为 “stuck-at” 线或static线。串扰(Crosstalk)能够引起一个静态线在时钟周期内出现切换。

13.假时钟False Clocking

假时钟是指时钟越过阈值(threshold)无意识地改变了状态(有时在VIL 或VIH之间)。通常由于过分的下冲(undershoot)或串扰(crosstalk)引起。

14.IBIS模型

IBIS(Input/Output Buffer Information Specification)模型是一种基于V/I曲线的对I/O BUFFER快速准 确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适合做振荡和串扰等高频效应的计算与仿真。

八、TTL电平和CMOS电平

1,TTL电平:

工作电压:通常为5V。

高电平:输出高电平通常大于2.4V,输入高电平大于2.0V。

低电平:输出低电平通常小于0.4V,输入低电平小于0.8V。

特点:TTL电路速度快,传输延迟时间短(5-10ns),但功耗较大。

2,CMOS电平

工作电压:范围较广,通常在3V到15V之间。

高电平:输出高电平接近电源电压(Vcc),输入高电平大于0.7*Vcc。

低电平:输出低电平接近0V,输入低电平小于0.3*Vcc。

特点:CMOS电路功耗低,静态功耗几乎为零,但速度较慢,传输延迟时间长(25-50ns)。

3,TTL和COMS电路比较

电压范围:TTL电平固定在5V,而CMOS电平范围更广。

噪声容限:CMOS电平的噪声容限更大,抗干扰能力更强。

功耗:TTL电路功耗较大,CMOS电路功耗较低。

速度:TTL电路速度快,CMOS电路速度相对较慢

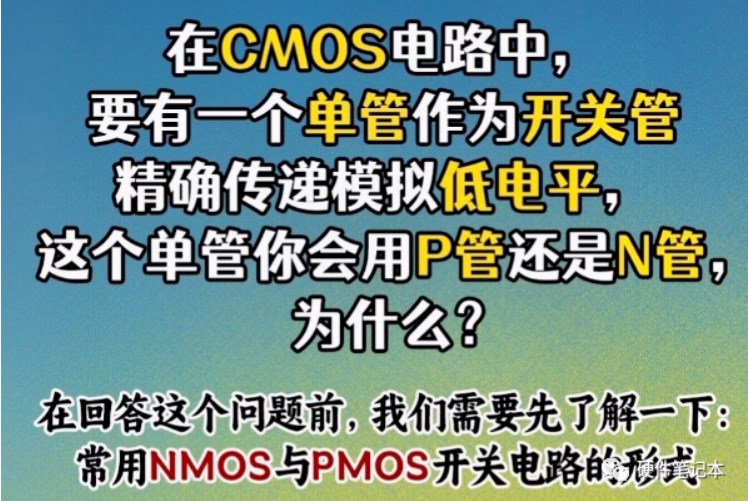

4、COMS电路的使用注意事项

1)COMS电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。所以,不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。

2)输入端接低内阻的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在1mA之内。

3)当接长信号传输线时,在COMS电路端接匹配电阻。

4)当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为R=V0/1mA.V0是外界电容上的电压。

5)COMS的输入电流超过1mA,就有可能烧坏COMS。

九、DFX分析方法

1,DFX分析概述

DFX是Design for X (面向产品生命周期各环节的设计)的缩写,其中X代表产品生命周期的某一环节或特性,主要包括:

可制造性设计DFM——Design forManufacturability;

可装配性设计 DFA------Design for Assembly;

可靠性设计 DFR------Designfor Reliability;

可服务性设计 DFS Design for Serviceability;

可测试性设计 DFT Designfor Test;

面向环保的设计 DFE------Design for Environment 等。

附录一 LDO使用之热阻考虑

1.LDO电源芯片的选型一

在通常的LDO设计中,热阻参数的考虑常常被忽略。但是,该参数对电源系统的影响却是很大的,因为LDO的该参数若是选择不当,就容易造成LDO芯片功耗过大、过热而进入热保护状态,导致电源断电。

最近在一个系统的电源芯片的选型中(系统输入为3.3V,需要得到1.8V的电压,该1.8V所需最大电流250mA左右),为了减小纹波对系统性能的影响,考虑用LDO来进行电压转换,最初选择了Sipex一个LDO(SP6205EM5-ADJ,SOT-23-5)。

该芯片的主要参数为:2.7V~5.5V的电压输入范围;500mA电流输出;输出电压可调;具有限流和热保护功能等。

咋一看,该电源芯片可满足系统需求,250mA的所需电流用500mA也是余量足够了。但与同事讨论,其说该芯片根本达不到500mA的输出电流,因为其热阻较高。于是,我开始详细的阅读该芯片Datasheet,发现其确实存在该问题。

以下讨论都是以该芯片的SOT-23-5封装为例说明。

Thermal Resistance:SOT-23-5(QJA):191 ℃/W

DFN-8(QJA):59 ℃/W

最大功率消耗为:PD(max) = (TJ(max)-TA)/ θJA,其中,TJ为节点温度,TA为环境温度,θJA为热阻。

当芯片超过了最大允许功耗时,节点温度会过高,从而芯片进入热保护模式。

SP6205-ADJ(SOT-23-5封装)的最大功耗为:

PD(max) = ( 125℃ – 25℃ ) / (191 ℃/W) = 523 mW

实际工作过程中,芯片功耗为:

PD = ( Vin – Vout)*Iout + Vin * IGND

通常,IGND为uA级(比如:SP6205在500mA输出时的IGND=0.35mA),若要求不是特别精确,基本可忽略Vin*IGND该项的影响。

因此,芯片实际工作时的功耗必须限制在最大允许功耗范围内,超过PD(max)则芯片进入热保护模式。

根据式(1),我们就可以算出以下参数:

(a)在已知输入输出压差的条件下,得出最大输出电流

例如:输入电压5V,输出电压3V,则:

523mW = (5V – 3V)*I(load(max)) + 5V * 0.35mA,

则 I(load(max)) = 260.6mA。

(b)在已知负载电流的条件下,得出输入输出允许最大压差

例如:输出电压为3V,负载电流为400mA,则:

523mW = (Vin – 3V)* 400mA + Vin * 0.35mA,

则 Vin(max) = 4.3V,△Vmax=1.3V。

所以,在LDO电源芯片选型的过程中,应该根据实际情况的需求,认真考虑其热阻参数。

回到本文开头说提到的系统需求,计算得到的实际最大输出电流为:I(load(max)) = 347mA。与芯片500mA的输出电流相比,电流余量大大降低了。而且,该电流最大值是在环境温度25℃理想情况下计算得到的,随着工作时间的推移,芯片的温度会逐渐升高,该输出电流的最大值还会进一步降低。其500mA的输出电流只有在输入输出压差1V以内、室温25℃的情况下才可以得到。

从以上分析可见,LDO的热阻参数对其它参数(如输出电流、输入输出压差等)是有较大影响的,必须予以考虑。选型时应尽量选择热阻小的芯片或封装,尤其是同一型号芯片的不同封装,其热阻会相差较大,比如以上电源芯片SP6205的DFN-8封装,其热阻就只有59℃/W,较之SOT-23-5封装的191℃/W小了不少。

2.LDO电源芯片的选型二

LDO芯片的主要有:输出电压、最大输出电流、输入输出电压差、 负载调整率、线性调整率、电源抑制比PSRR。在芯片选型时这些都需要进行对比择优而选之,

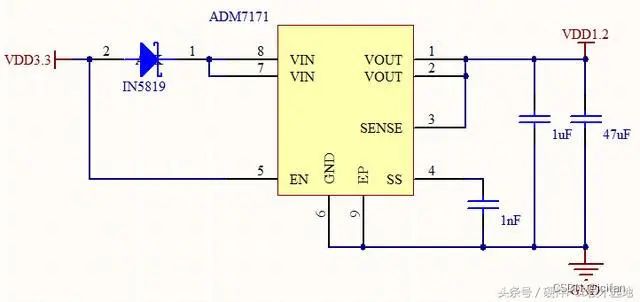

例:现有一个输出1.2V,负载电流为0.4A的应用,有两个芯片作为备选方案:ADM7171和AMS1117-1.2。主要参数对比如文章最后表格,可以看出二者各有优劣。

下面我们根据最重要的一条来决定两个芯片谁更适合本应用设计----最高工作温度下的芯片晶元结温。

一般LDO电源芯片功耗Pd = [(Vin–Vout)*Iload]+( Vin*Ignd),其中Vin为芯片电源输入电压、Vout为芯片输出电压、Iload为负载电流、Ignd为接地电流,通常Ignd可忽略不计。Pd = (Vin–Vout)*Iload。

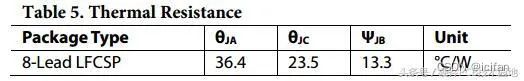

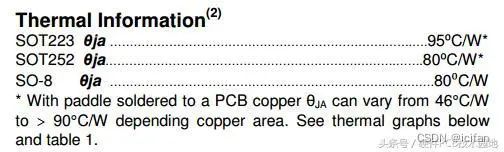

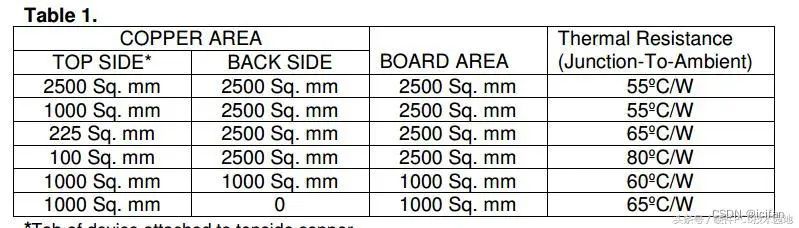

查找手册确定芯片的热阻,ADM7171如图4,AMS1117-1.2如图5。

图4 ADM7171 热阻

图5-1 AMS1117热阻

图5-2 AMS1117热阻表

根据table1,按最低55℃/W计算。

LDO芯片晶元结温计算公式为:Tj=Ta+(Pd*θja),其中Tj:晶元结温,Ta:环境温度,θja:芯片热阻。假设系统电源为3.3V,这里按工业产品最高工作85℃。根据芯片功耗及热阻,计算在最高温度时芯片晶元结温:

ADM7171:Tj=85℃+(0.84W*36℃/W)=115℃,与最大工作结温相差10℃。

AMS1117:Tj=85℃+(0.84W*55℃/W)=136℃,超过最大工作结温11℃。

显然ADM7171更能满足高温工作的性能。

(2)LDO电源芯片电路设计

虽然ADM7171是较为合适的选择,但结温降额只有10℃,从长期工作可靠性角度来讲还是有些不满足要求。在系统电源为3.3V的情况下,可以在ADM7171的电源输入串入一个二极管,如图6,使Pd = [(Vin–Vout)*Iload]中的Vin–Vout差值进一步降低。

图6 最终电路图

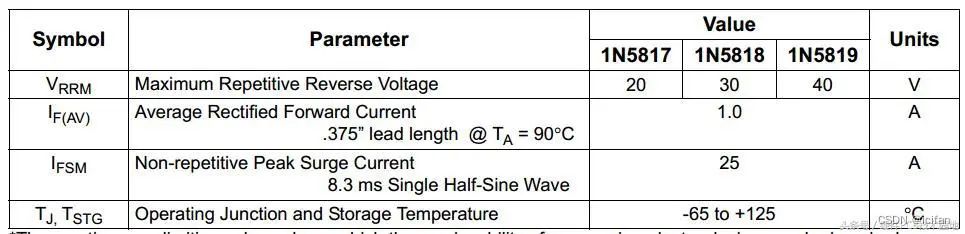

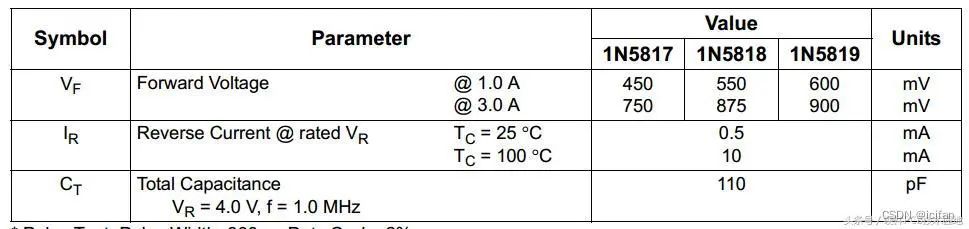

图7为1N5819二极管手册。正向压降为0.55V,此时Tj=85℃+((3.3-0.55-1.2)0.4*36℃/W)=(0.62W*36℃/W)=107℃。此时二极管通过电流为I= (Po+Pd)/Uin=(1.2*0.4+0.62)/(3.3-0.55)=0.4A为1N5819正向导通电流的一半,符合工业产品降额要求。

图7-1 二极管正向电流

图7-2 二极管正向压降

-

ldo

+关注

关注

35文章

1940浏览量

153304 -

晶振

+关注

关注

34文章

2859浏览量

68000 -

DC-DC

+关注

关注

30文章

1942浏览量

81602

原文标题:硬件工程师面试基础知识点

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

硬件工程师面试基础知识点

硬件工程师面试基础知识点

评论