回顾

通过上一期我们了解到:数字电子产品中电源轨噪声和时钟抖动是有关联的,以及测量电源轨噪声的方案,接下来我们基于实际测量,揭示电源轨噪声对系统时钟抖动的影响。

PART2

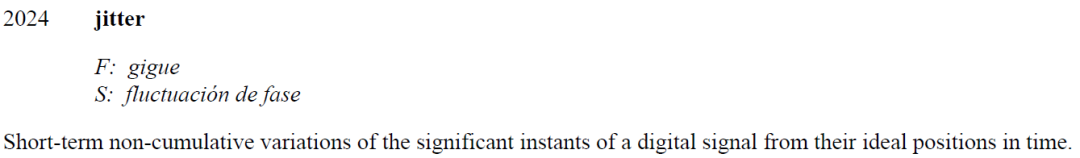

首先了解抖动的定义,在ITU-T G.701中有关抖动的定义如下:

数字信号重要瞬间相对于其理想时间位置的短期非累积变化。

抖动是时钟或数据信号时序的短期时域变化。抖动包括信号周期、频率、相位、占空比或其他一些定时特性的不稳定。抖动在不同周期、多个连续周期或作为长期变化都很重要。

抖动的基本类型:TIE (Time Interval Error) ,Period Jitter ,Cycle-Cycle Jitter等。

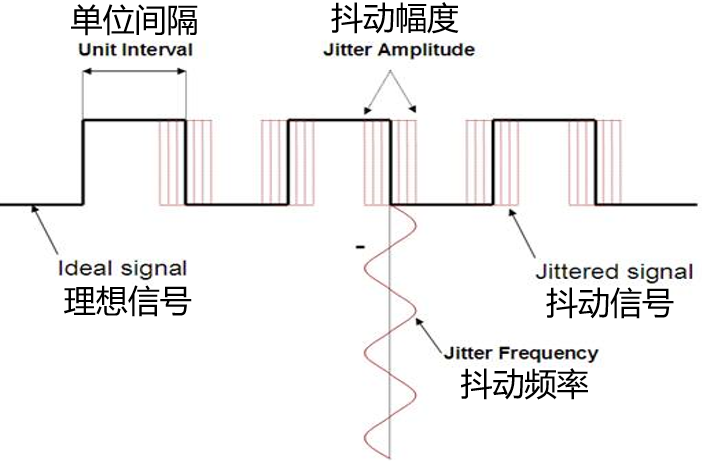

我们使用示波器测得时钟信号抖动TIE(Time-interval error)作为测量项目,并启用测试统计量中的StdDev(标准偏差)作为测量结果。

值得注意的是,除了时域波形,示波器还提供 3 种视图帮助我们对TIE进行分析查看:

1、Track波形;

2、直方图;

3、频谱视图

先解释Track功能,因为它是后续实现电源噪声和抖动TIE关联的关键。

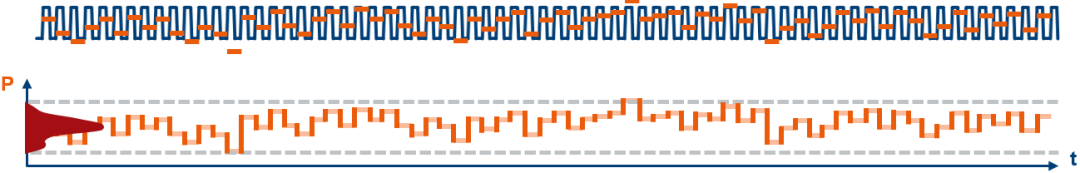

Track波形显示了与测量信号时间相关的测量波形。它是单次采集所有测量值的图形解释。Track功能适用于幅度/时间测量(高、低、幅度、最大值、最小值、峰峰值、平均值、RMS、S-dev、正和负过冲以及面积除外),以及抖动测量。

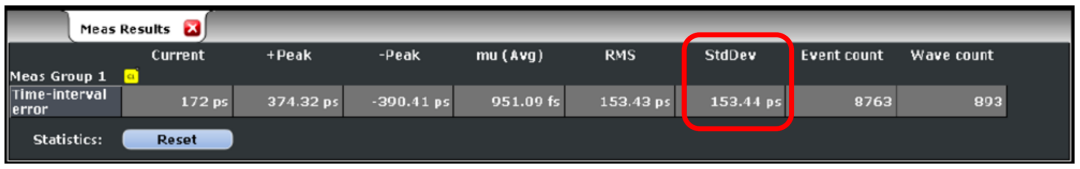

针对时钟周期进行Track为例;

把单次采集的所有周期值取出来,用P1,P2,P3代表周期值,把所有周期值以随时间变化的分布排列起来就形成周期的Track波形。

利用Track波形便能直观地表示周期值随时间变化的趋势。

那么针对抖动TIE进行Track,Track波形就是TIE测量值随时间变化的趋势。为什么要这样啦,我们继续往下看。

PART3

利用频域视图分析:

实现电源轨噪声与时钟抖动关联比较

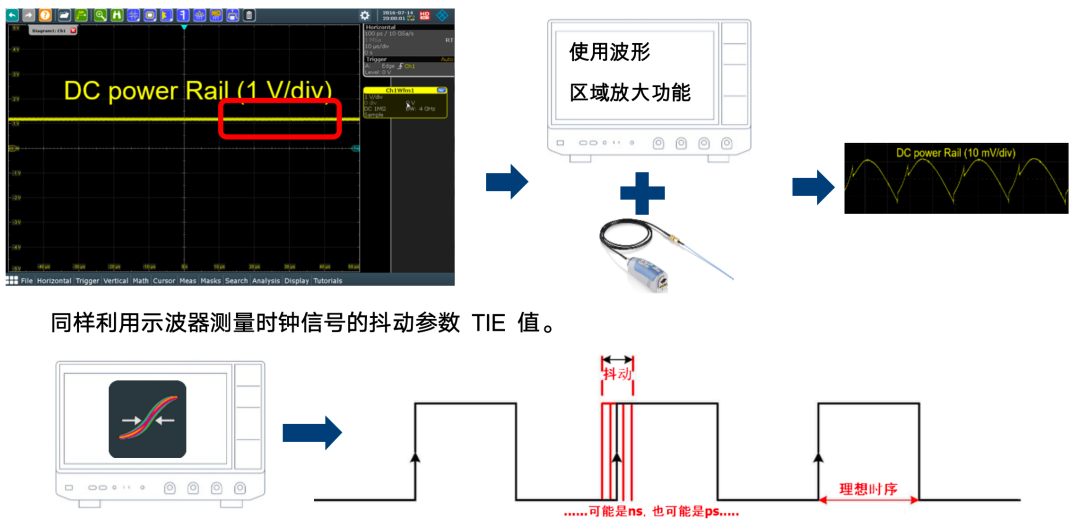

首先利用示波器加电源轨探头的方案测得电源轨上Vpp值。

问题来了,一个是电压值参数,一个是时间参数。那么怎么把它们关联起来进行比较啦?

答案就是利用示波器的频谱视图,把时域波形转换到频域频谱中去进行比较,这充分体现了示波器相比于其他仪器 -- 所具备的强大时频域动态联调能力;不仅查看时域波形中幅值差异和瞬态变化的同时,还可以在频域视图看清耦合的干扰,甚至分析高频噪声。

比如测量电压信号时,使用频谱视图,就可以显示同一信号的两个频段的频谱信息。(针对图中左边的黄色电压信号,右上角图示了DC到1GHz的频谱信息,右下角的图示了DC到1Mhz的频谱信息)

基于上述方法,将测得的时钟信号抖动TIE,通过Track波形转化成频谱视图。

不难发现,利用示波器提供的频谱视图可以实现两者关联。

接下来以一个实例测量进行说明。

PART4

测量示例

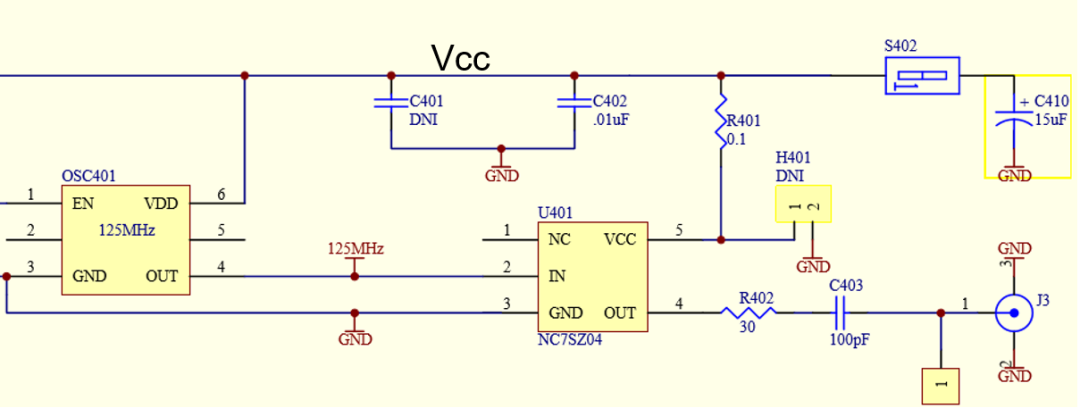

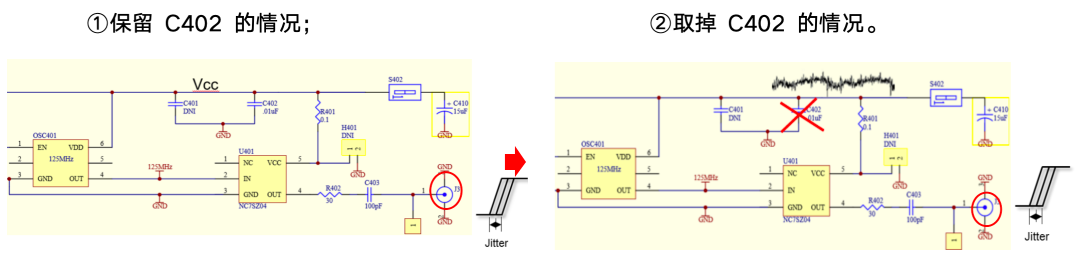

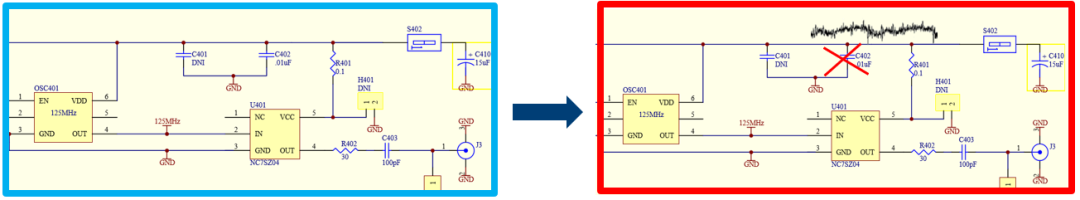

对于如下典型时钟振荡电路中利用反相器NC7SZ04输出时钟信号,如果此电路中Vcc电源轨容限恶化或纹波不佳时,NC7SZ04输出的时钟信号是否会受影响?

实验测量比较两种情况,人为地把Vcc输入处的滤波电容C402取掉后,对比Vcc噪声变化以及时钟信号的TIE的变化。

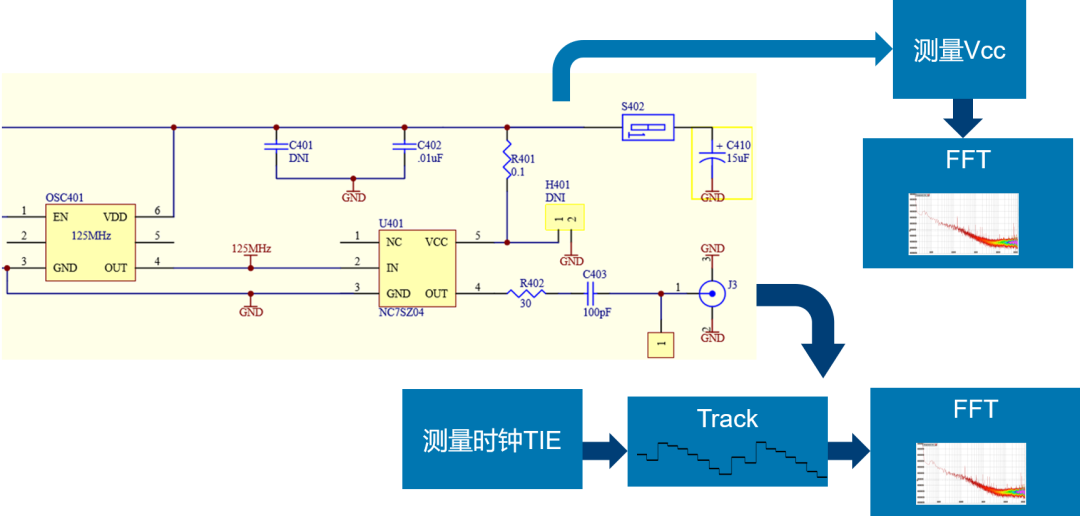

测试的拓扑图如下:

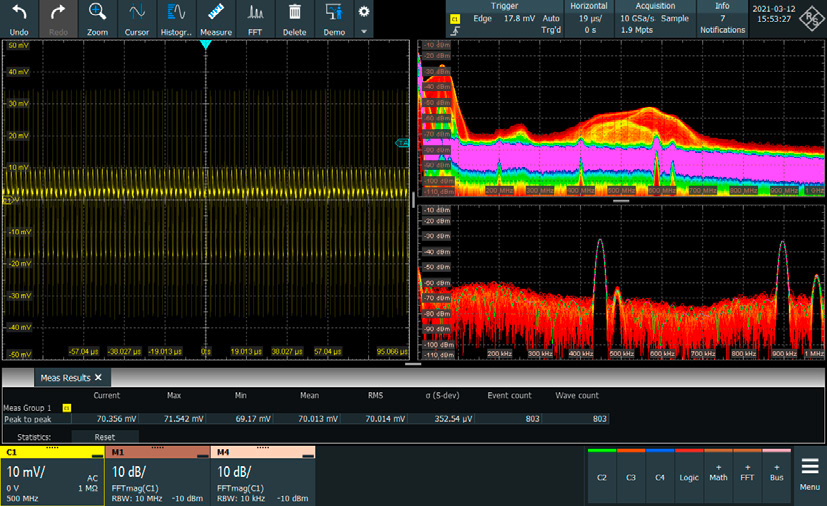

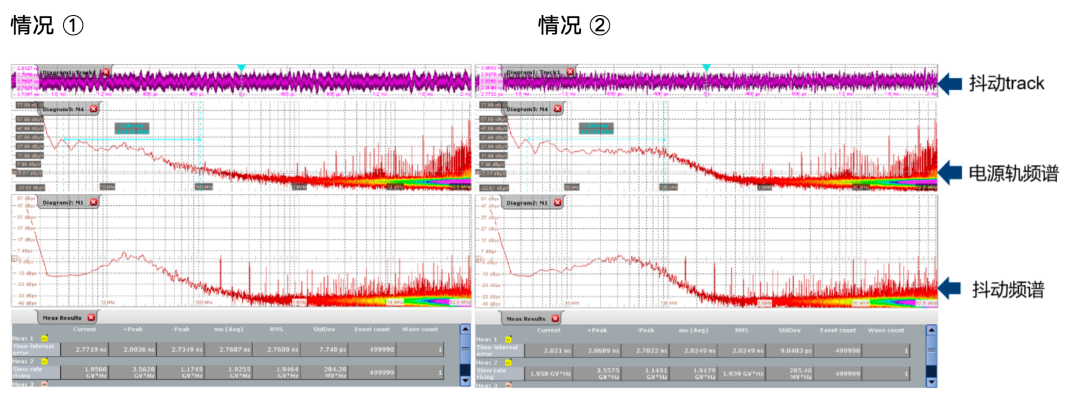

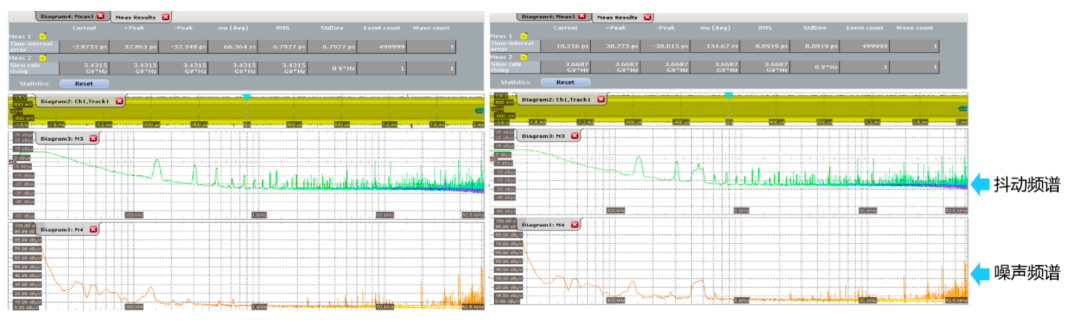

01对比两种情况下,电源轨Vcc的频谱和抖动TIE-track的频谱

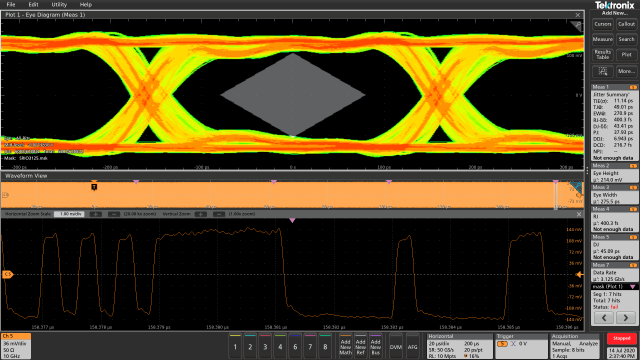

测试界面说明:示波器界面从上到下显示了时钟TIE Track的波形,中间是电源轨Vcc经过FFT得到的频谱,下方是根据TIE -Track经过FFT得到的频谱。

从测试结果中可以得到两个信息:

TIE的StdDev从7.748ps增加到了9.0483ps (9.0483-7.748=1.3003) 大约1ps抖动。

当取掉电容C402后30Khz到300Khz频率范围内噪声增加。

说明Vcc供电噪声恶化后影响输出时钟信号的抖动TIE也变差了。

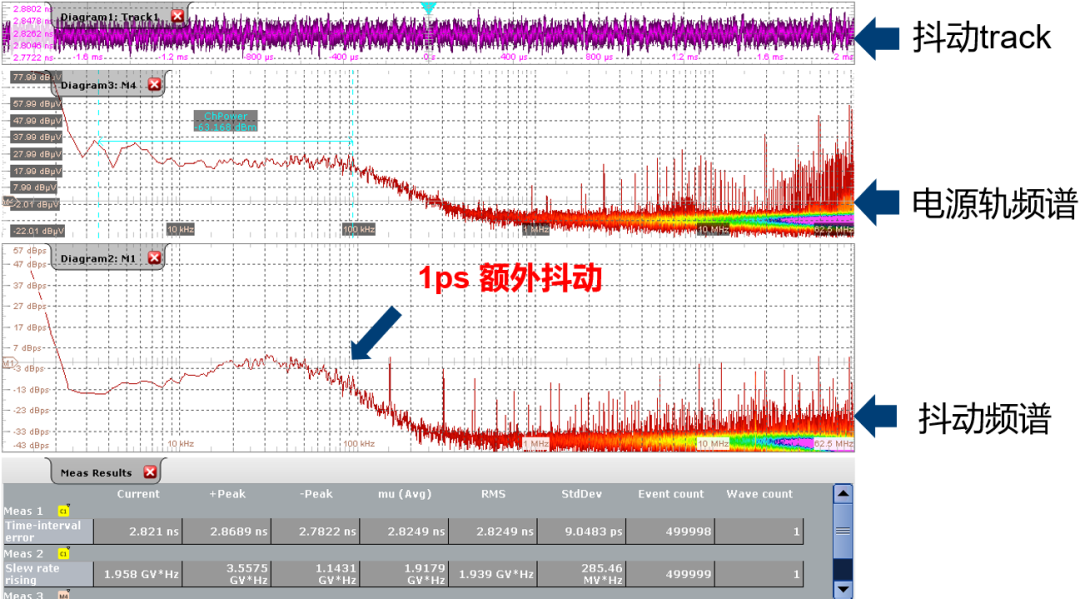

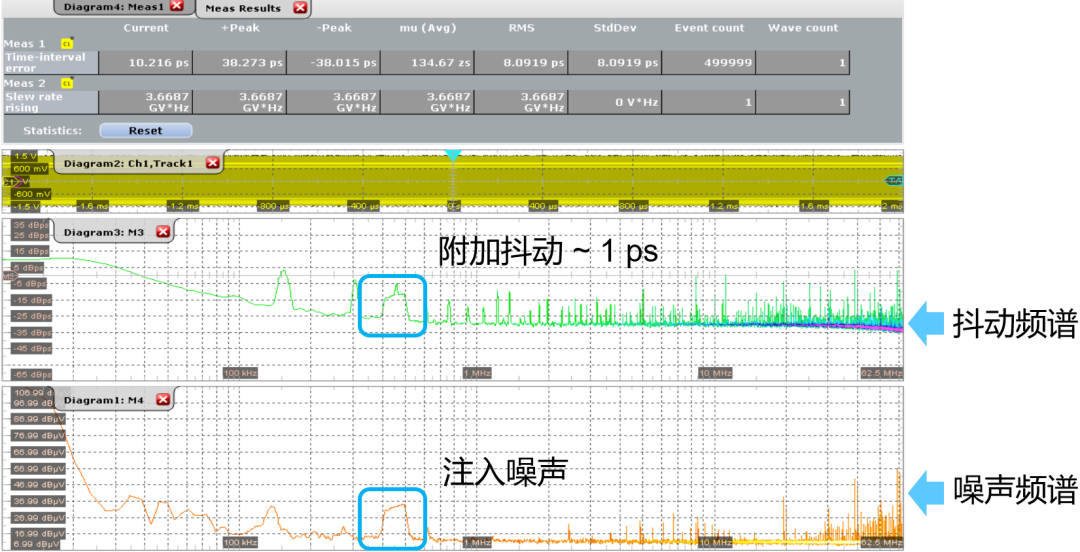

02对比两种情况下,输出时钟信号噪声的频谱和抖动TIE-track的频谱

从最后的结果中可以查看两个信息:

TIE的StdDev从6.7927ps增加到了8.0919ps(8.0919-6.7927=1.2992)也是大约1ps抖动。

当取掉电容C402后在400Khz到500Khz频率范围内时钟信号测得的噪声增加。

从上述的实验中看到,利用频谱视图关联电源轨噪声和抖动TIE的测量比较,发现电源轨噪声的恶化最终导致了时钟抖动的增加(其中时钟信号自身的噪声也是增加的)。由此可知,当电源输入端受噪声注入时,将会对时钟抖动带来影响。

随着高速信号的发展,数字电子产品中的频率越来越高,尤其达到Ghz级别后,信号完整性固然重要,有关电源完整问题也不能忽视,因为它们既有联系又相互影响。电源轨上的噪声恶化会导致时钟信号抖动增加,进而影响高速信号传输,为了在产品设计中优化这些问题,就不得不依靠强大的测试测量仪器;罗德与施瓦茨提供了强大的电源轨探头RT-ZPR,充分应对这些挑战,可以进行准确测量 (高带宽,高灵敏度,低噪声和大偏置补偿),搭配罗德与施瓦茨强大的示波器产品,轻松地实现了时频域的联合调试--既准确又高效。

罗德与施瓦茨业务涵盖测试测量、技术系统、网络与网络安全,致力于打造一个更加安全、互联的世界。成立90 年来,罗德与施瓦茨作为全球科技集团,通过发展尖端技术,不断突破技术界限。公司领先的产品和解决方案赋能众多行业客户,助其获得数字技术领导力。罗德与施瓦茨总部位于德国慕尼黑,作为一家私有企业,公司在全球范围内独立、长期、可持续地开展业务。

-

示波器

+关注

关注

113文章

6240浏览量

184790 -

噪声

+关注

关注

13文章

1120浏览量

47400 -

时钟抖动

+关注

关注

1文章

62浏览量

15922 -

数字信号

+关注

关注

2文章

969浏览量

47538 -

电源轨

+关注

关注

1文章

34浏览量

5758

原文标题:【实践分享】|浅谈电源轨噪声对时钟抖动的影响(二)

文章出处:【微信号:罗德与施瓦茨中国,微信公众号:罗德与施瓦茨中国】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何通过电源轨分析理解电源轨噪声与抖动

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理

电源噪声和时钟抖动对高速DAC相位噪声的影响分析及管理

时钟抖动(CLK)和相位噪声之间的转换

时钟抖动和相位噪声对采样系统的影响

时钟抖动的影响

电源轨噪声对系统时钟抖动的影响

电源轨噪声对系统时钟抖动的影响

评论