如今,由于对大电流和高功率应用的需求不断增加,单一的MOSFET已经无法满足整个系统的电流要求。在这种情况下,需要多个MOSFET并联工作,以提供更高的电流和功率,这有助于减少导通损耗,降低工作温度,从而提高系统的可靠性。然而,当两个或更多MOSFET并联时,应考虑电流的一致性,以便在瞬态和稳态条件下平衡通过每个MOSFET的电流。

在本篇应用文章中,主要集中讨论了导致电流不平衡的动态参数,如阈值电压(Vth)和输入电容(Ciss)等,进一步讨论了驱动回路和功率回路寄生电感的影响,并提出了优化的PCB布局供设计参考。

*本篇应用文章主题为“Paralleling and Driving Power MOSFETs in High-Power Applications”,是由AOS AE团队成员(Alvin Liu, PhoebusChang, Peter Huang, Shaowei Cui, Bugao Wang, Chengyuan He)联袂撰写,以下是原文节选翻译。

01、阈值电压不匹配 电流不平衡

阈值电压(Vth)的变化在许多MOSFET产品中是常见的,尤其是在不同的生产批次中。本实验选取了具有不同阈值电压(Vth),同时保持其他参数(如Rg、Ciss和Gfs)不变的器件。为了便于研究MOSFET并联时的电流均流特性,进行了简化处理,研究了2个、3个和5个MOSFET并联时的均流特性。实验器件(DUT)为AOTL66912,采用典型的TOLL封装,具有100V的BVDSS,RDS(on)为1.4mΩ。

02、多管并联应用 参数设计影响均流效果

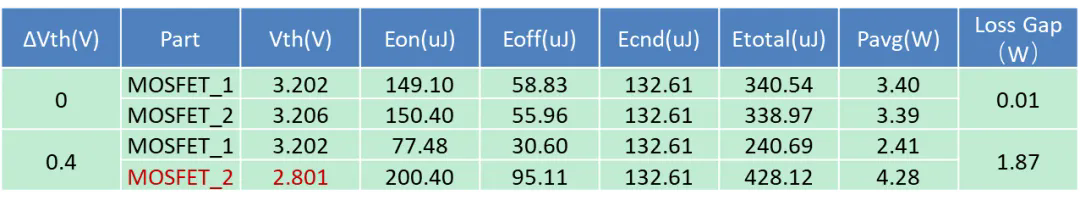

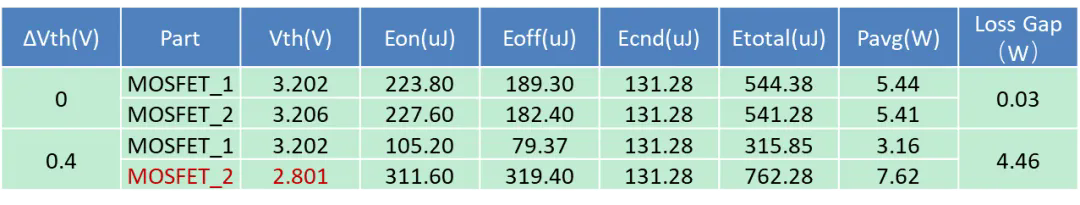

当并联的两个MOSFETs具有相同的参数,如内在阈值电压(Vth)、Rg和Ciss时,它们的开通能量(Eon)和关断能量(Eoff)非常相似,功率损耗的差距仅为0.01W。当2号MOSFET被Vth较低的器件替换时,其Eon和Eoff显著增大,功率损耗比Vth较高的1号MOSFET器件高出1.87W,如表1所示。

图▲ Two MOSFETs parallel Test Result (Ton=250ns, Toff=100ns, Fs=10KHz)

MOSFET开关速度是影响电流平衡的另一个因素。在测试中,采用了更长的开通时间(Ton)和关断时间(Toff),以及较高的外部驱动电阻Rg,此时不同Vth的器件之间的功率损耗差距会变大,如表2所示。当关断时间为100ns时,Vth较低的2号MOSFET与1号MOSFET之间的总功率损耗差(包括开关损耗和导通损耗)约为1.87W;而当关断时间为300ns时,功率损耗差距将增大到4.46W。其原因在于,当关断时间更长时,两个MOSFET的Vgs达到Vth的间隔时间变长,从而使得功率损耗差距也变大。

根据测试结果,具有相同Vth值的MOSFET并联时,MOSFET外部驱动速度的快慢是实现更好电流平衡性能的关键因素。

图 ▲ Two MOSFETs Parallel Test Result (Ton=380ns, Toff=300ns, Fs=10KHz)

03、MOSFET栅极驱动不匹配 电流不平衡

驱动参数的一致性,包括驱动回路的电阻、电容和电感,是影响电流平衡特性的另一个因素。

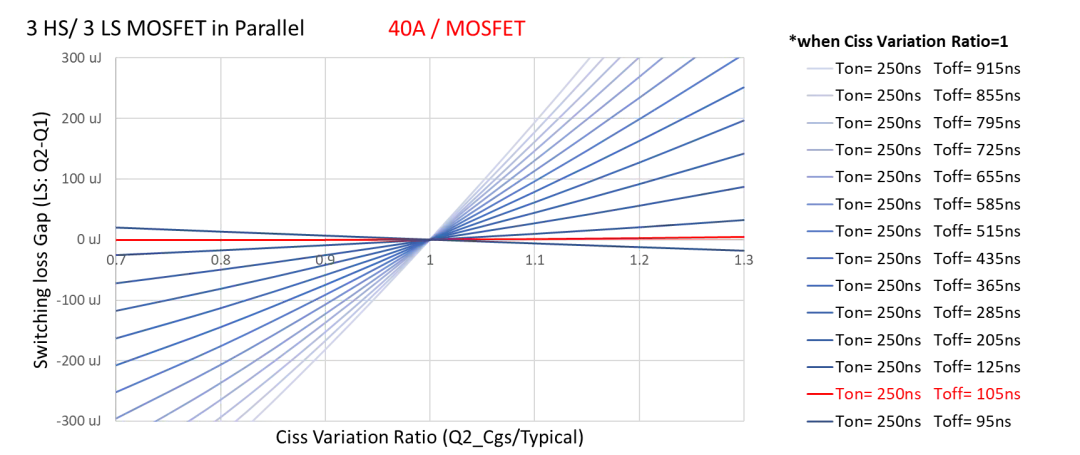

当两个MOSFET并联且其驱动回路的电容不同,具有较大输入电容(Ciss)的MOSFET的开通时刻将比另一个MOSFET延迟,这会导致具有较大Ciss的MOSFET的开通能量(Eon)较小。然而,关断过程则不同,较大的Ciss会导致关断时刻延迟,从而导致较大的关断能量(Eoff)。

通常情况下,当两个MOSFET并联时,具有较大Ciss的MOSFET的Eon较小,但Eoff较大。

MOSFET的输入电容或驱动回路对Eon和Eoff具有相反的影响。如果一个MOSFET的Ciss高于其他并联MOSFET的Ciss,其Eon将减小,而Eoff则会增大。实际上,在某些条件下,Eon和Eoff的总和可以进行权衡,进而达到最小值。因此,不同Ciss对电流平衡的影响可以忽略不计,如图1所示。在实际应用中,建议Toff应约为Ton的40%以实现最佳系统设计。

Ciss Variation Ratio vs Switching Loss Gap | 1 图 ▲

04、驱动参数优化与电流共享 外部Rg选择对电流平衡的影响

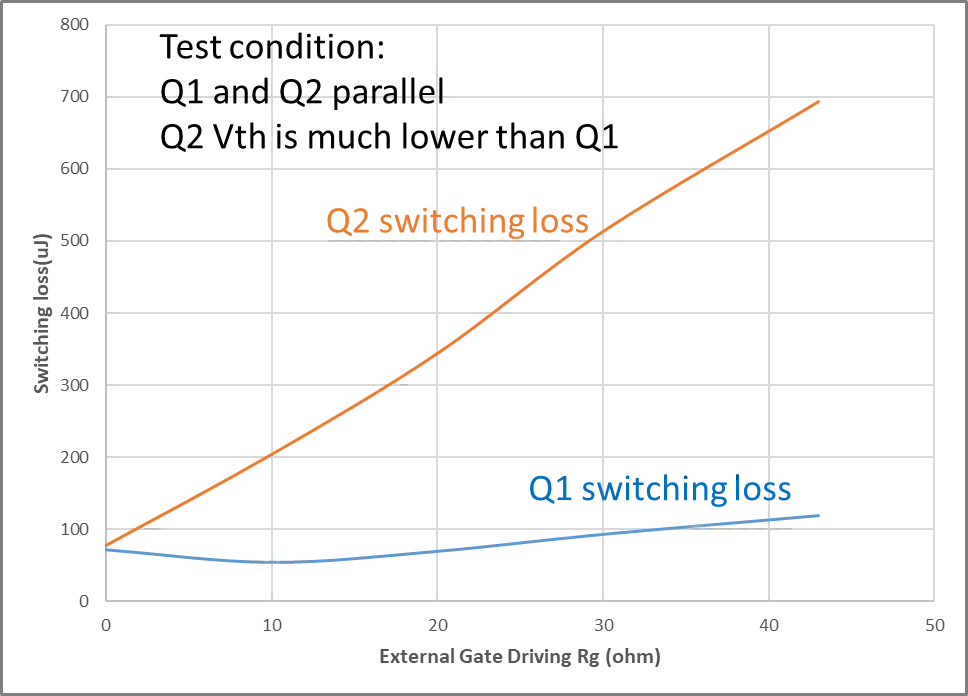

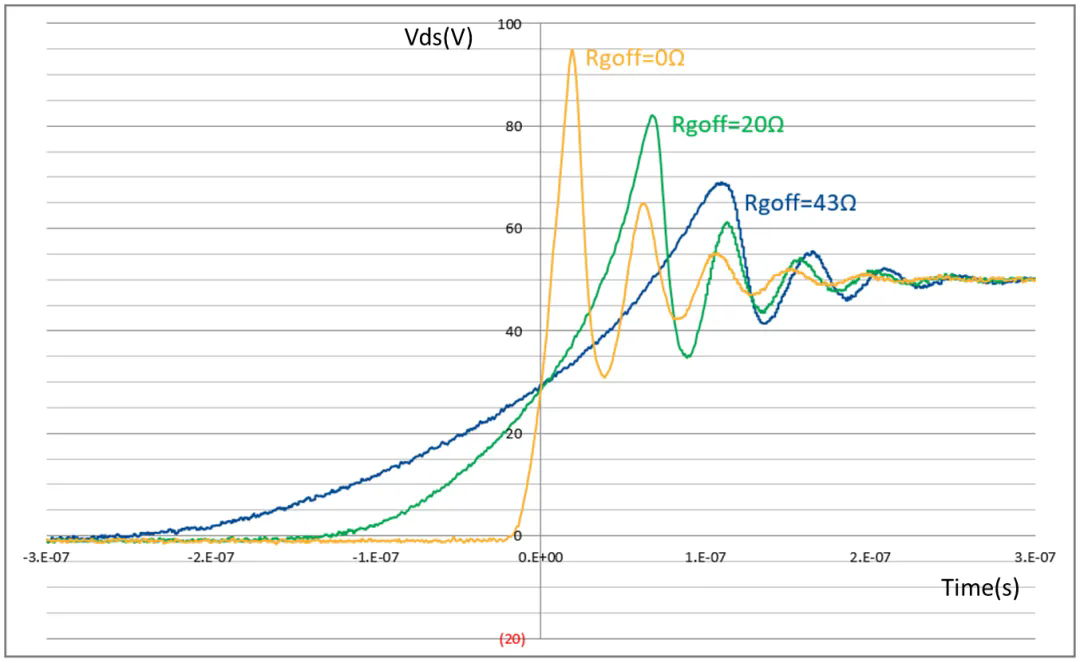

栅极驱动回路的一致性将极大地影响电流平衡性能。驱动回路应保持一致,以满足电流平衡的要求。其次,为了满足系统效率的要求,开关速度应尽可能快。更快的开关速度将导致并联MOSFET之间的开关损耗差距变小,如图2所示。然而,快速的开关速度可能会引发过大的电压尖峰,如图3所示,因此电流平衡特性和电压尖峰之间存在权衡,在系统设计中应找到平衡点。

Differences in Total Switch Losses Under Different Rg | 2 图 ▲

Vds Spike Voltage vs Rgoff | 3 图 ▲

05、结论

在高电流并联应用中,影响电流一致性的因素主要来自两个方面:一是MOSFET参数的一致性,如Vth和Ciss;二是应用中驱动回路设计和功率回路设计的不一致性。对于MOSFET制造商来说,控制生产工艺以获得参数一致性至关重要。从应用角度来看,合适的驱动设计、一致的驱动回路和功率回路电感设计同样是确保电流一致性的关键因素。

唯样是国内知名的电子元器件线上授权代理商。致力于服务终端研发、高校科研、工程师等广大客户高品质、少量多样、快速交付的元器件采购需求。

唯样拥有3.5万㎡仓储、超13万种现货库存、2500w+产品型号数据,已获得YAGEO、TDK、TE Connectivity、nexperia、ROHM、Panasonic、MPS等全球数十家一线品牌代理授权。

审核编辑 黄宇

-

MOSFET

+关注

关注

147文章

7156浏览量

213133 -

高功率

+关注

关注

1文章

192浏览量

18403 -

AOS

+关注

关注

0文章

23浏览量

305

发布评论请先 登录

相关推荐

串联和并联在家居布线中的应用

功率MOSFET的选型法则

压敏电阻是串联还是并联在电路中

熔断器是串联还是并联在电路中

大功率IGBT和SiC MOSFET的并联设计方案

MOSFET并联(并联功率MOSFET之间的寄生振荡)

功率 MOSFET、其电气特性定义

AOS推出新款100V MOSFET AONA66916

AOS推出创新型双面散热 DFN 5x6 封装

AOS MOSFET并联在高功率设计中的应用

AOS MOSFET并联在高功率设计中的应用

评论