在传统PCB开发历程中,往往为了符合开发时程表的期程,我们发现Layout工程师及各个功能开发团队,时常被要求必须在一周内完整解决检查报告中的每一项违规点。检查报告中的违规点数量,以单颗CPU为例,约有三、四千个,双CPU则经常多达七、八千个。

由此可见,这一项要求的背后,需要的是硬体及电源开发工程师即时审查及修正。同时,也必须要有4至5名Layout工程师每天熬夜赶工,以手动进行细部修正所有的违规项目。

传统PCB审查历程的四大痛点

在时间极度压缩的情况下,如何提升效率、增加处理时间,成为了第一要务。因此,环旭电子CIES研发团队在累积的开发案中归纳出四大关键痛点,其中又以第一点最为重要。

如何提升修正Layout违规点的效率,并加快进入出图生产(Gerber Out)的过程?

如何整合来自不同来源的检查需求,减少工程师的汇整负担?

如何统一各功能的检查标准,避免人为标准的落差?

如何记忆各项检查项目及规范细节,降低工程师每次执行检查的作业量?

从四大痛点中,环旭电子CIES研发团队整合多年经验,设计出「前端设计与vwin 自动化平台(FEDS)」,其中自动化电路布局审查工具,将审查工具进行标准化以提高检查效率,进一步优化整个「PCB审查历程」的作业效率。

解决方案 - 什么是前端设计与模拟自动化平台(FEDS)?

前端设计与模拟自动化平台 (FEDS) 是一套由USI环旭电子自主开发,专为提升电子产品设计效率与品质而生的工具平台。它的核心概念是将设计过程中许多重复性高、易出错的任务自动化。从一开始的物料清单生成与检查,到后续的电路图、PCB布局检查,甚至是复杂的电磁模拟,它都能提供全方位的自动化支援。不仅能大幅缩短产品开发周期,更能有效降低人为错误的发生机率。

你可以将FEDS想象成Google平台,此平台不仅提供电路布局审查功能,同时,它也拥有非常多样的延伸应用工具,例如:原物料清单(BOM)生成与检查、线路图检查 (Schematic Check)、模拟仿真电性特性(RF PI Simulation)符合电性规定、RF线上协同作业(RF Matching) 包含:优化RF特性、RF测试自动化、RF测试模拟结果比对…等等。

自动化平台 (FEDS) 最大的差异化优势,就在于极度灵活的客制化能力。传统的商业化EDA工具往往功能过于通用,而FEDS允许企业根据自身产品特性与设计流程,自行开发并整合各种检查规则与模拟工具,能够更精准地满足企业的需求,提升设计效率。

自动化电路布局审查

PCB开发工程师在进行电路布局审查时最需要的需求主要有四项:

常被用于检查CPU讯号介面是否符合其规范的第三方工具。

不同平台设计指南(PDG)对各个讯号介面的规范要求。

公司内部各研发单位或制造部门的设计经验与需求。

户研发工程师对产品的特殊检查需求。

上述需求都被整合在自动化电路布局审查工具中,它具备不断扩充功能,可建立新检查项目并帮助工程师即时修正布线。自动检测完成后,可输出报告供研发工程师检视。此外,系统会收集检测数据以进行统计分析和设计检讨。

目前自动化电路布局审查工具有五大类,包括Routing Check, Pad and Placement及Via Check等。此外,自动化电路布局审查可针对产品的特殊需求,开发专利检查项目,如:差动讯号出线对称性检查、避免串扰效应的检查,以及电源完整性优化的接地过孔密度检查。

1) 差动讯号出线对称性检查:确保差动讯号在焊垫及通孔出线时的走线对称。

2) 避免串扰(CrossTalk)效应:确保差动讯号的焊垫及通孔之间不被其他讯号穿越,以减少干扰。

3) 接地过孔密度检查:此功能可在Layout工程师初步完成走线时,快速检查电源网路(PDN),提前解决电源完整性问题,大幅节省时间和资源。

导入成效

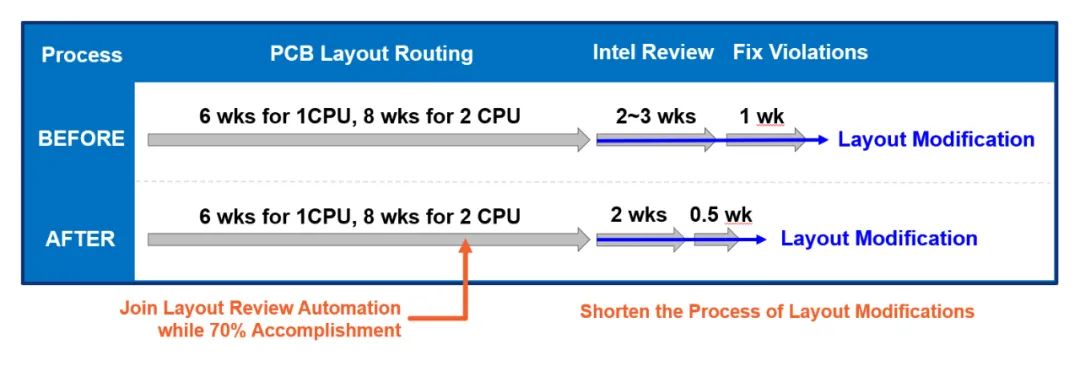

图1. 透过自动化审查工具,PCB Layout开发时程的优化比较

自动化电路布局审查工具主要可以在电路图完成70%的布线之前,自动找出违规并修正,在整体开发过程中,可显著发现两大项的优化成长:

1. 查找Board file上违规点的正确性与一致性

• 导入前: 倚赖经验丰富工程师,意见不一,耗时且效率低。

• 导入后: 自动化检查,统一标准,缩短检查及修正违规点的总时数。

2. 自动化检查与人工检查效率比较

• 导入前: 人工检查耗时长,尤其是大型专案。

• 导入后: 自动化检查速度快,大幅提升效率,可降低工程师所需的重复性工作。

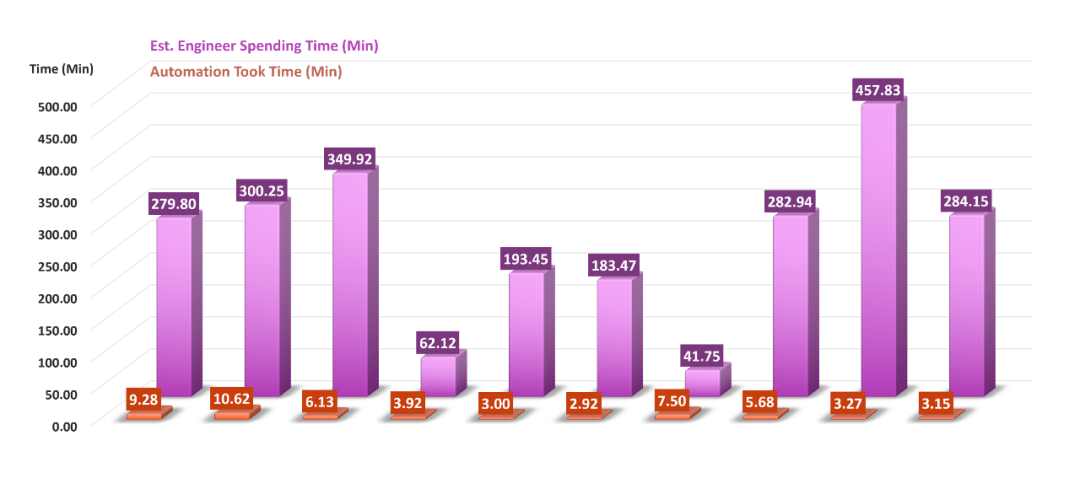

从2023年的Layout专案加以分析、比较自动化与人工检查的工时,图2明显可看出两者的差距已超过十倍,甚至是百倍以上,由此可知自动化对于布局审查作业,有显著提高效率的贡献。

图2. 人工检查与自动化检查的耗时比较

综上所述,自动化检测系统的导入,为企业带来了多方面的效益:

大幅加速产品开发效率:缩短Layout检查时间,加速产品上市时程。

提升检查结果的一致性与可靠性:降低人为因素造成的错误。

自动化平台的灵活性:能针对不同产品、不同制程,客制化开发所需的检查项目。

提高产品品质:及早发现并解决设计问题,降低产品瑕疵率。

展望未来,随着产品设计的复杂度将持续增加,对Layout检查的要求也将越来越高。透过自动化系统,企业能将工程师从繁琐的重复性工作中解放出来,使其能够专注于更具创新性的工作,提升效率、优化品质。

「前端设计与模拟自动化平台」已然是环旭电子开发服务中不可或缺的一环。

-

pcb

+关注

关注

4318文章

23078浏览量

397426 -

Layout

+关注

关注

14文章

403浏览量

61736 -

电路布局

+关注

关注

0文章

5浏览量

9797 -

环旭电子

+关注

关注

0文章

53浏览量

3473

原文标题:FEDS:百倍效率革命!打造自动化电路审查高效流程

文章出处:【微信号:环旭电子 USI,微信公众号:环旭电子 USI】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电子自动化项目承接!

基于EXFO新LTB平台的自动化测试和仪表共享方案

电子设计自动化(EDA)是什么

环旭电子微小化创新研发中心为多样化市场提供SiP双引擎技术平台

环旭电子前端设计与模拟自动化平台解决方案

环旭电子前端设计与模拟自动化平台解决方案

评论