文章来源:老虎说芯

原文作者:老虎说芯

本文简单介绍了多芯片封装的概念、技术、工艺以及未来发展趋势。

多芯片封装技术(Multi-Chip Packaging, MCP)是现代集成电路(IC)领域的一项关键技术,用于在一个封装中集成多个芯片或功能单元。这项技术通过空间的优化和功能的协同,大幅提升了器件的性能、带宽及能源效率,是未来高性能计算、人工智能、通信等领域的核心基础。

1. 多芯片封装的基本概念

1.1 定义与核心思想

多芯片封装是一种将多个芯片(逻辑芯片、存储芯片、射频芯片等)集成到一个封装体中的技术。它包括2.5D封装(通过硅中介层连接)和3D封装(垂直堆叠芯片),实现更高的集成度和性能。

比喻:可以将多芯片封装理解为搭建“微型城市”:每个芯片是一个功能区域,通过“道路”(互连结构)连接,实现高效协作。

1.2 优势

提升性能:缩短芯片间信号传输路径,降低延迟和功耗。

节省空间:更小的封装体积适用于移动设备和高密度服务器。

模块化设计:便于不同功能芯片的灵活组合,降低设计复杂性。

2. 关键技术要点

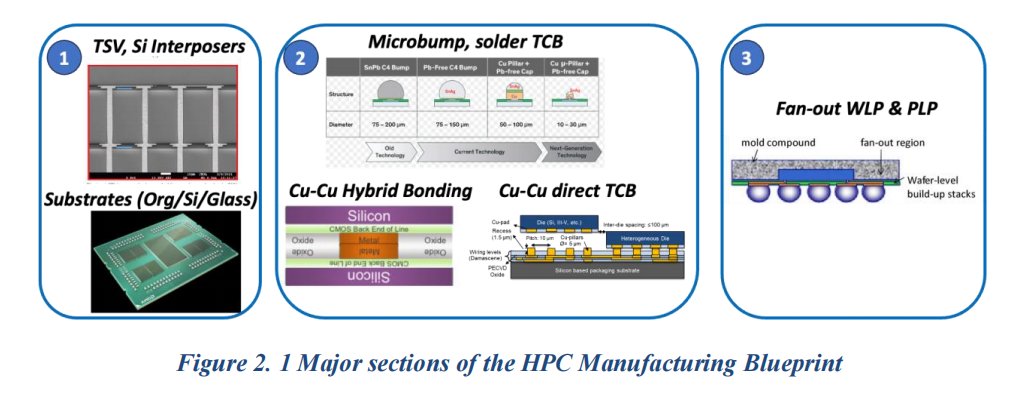

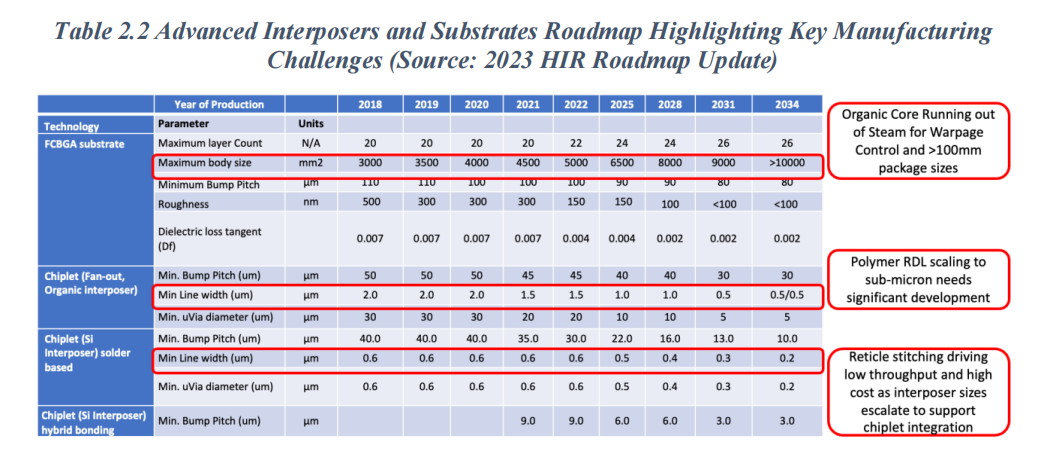

2.1 先进基板

先进基板是多芯片封装的物理载体,其性能直接决定信号传输的速度和功耗。当前技术要求先进基板的线宽/线距在1/1μm甚至更小,以满足高带宽和低功耗的需求。

当前缺口:美国产业链在先进基板制造方面落后于亚洲,特别是在精细间距重新布线层(RDL)技术上。

未来目标:HIR计划到2030年实现0.5/0.5μm线宽/线距。

2.2 互连技术

芯片间互连是多芯片封装的核心挑战。包括以下两种主流技术:

硅中介层(Interposer):提供高密度互连,支持更大的带宽,但制造成本高。

有机基板:成本较低,但信号完整性和散热性能略差。

2.3 热管理

封装功率密度的增加对热管理提出了更高要求。

挑战:200-400W的热设计功耗(TDP)需要有效散热方案。

解决方案:引入先进的封装内热导材料、集成热界面材料(TIM)和液冷等技术。

2.4 电源传输

高带宽需求使电源传输成为一大瓶颈。

问题:传统分立电源组件已无法满足封装内高功率密度要求。

解决方法:基于封装内电压调节器(IVR)的技术,利用电感和开关电容实现高效电源传输。

3. 工艺挑战

3.1 制造工艺

多芯片封装的实现依赖高精度制造工艺,主要包括:

精细间距RDL制造:当前投资主要集中在亚洲,需要突破以实现更高的线宽/线距。

面板级封装(PLP):针对大尺寸封装提供更高性价比的解决方案。

3.2 材料升级

多芯片封装需要新型材料的支持:

中介层替代材料:如高密度陶瓷基板,具备更高热导率和机械强度。

封装材料:需要支持更高的热导率和更低的电阻。

3.3 可靠性

堆叠芯片和细间距互连带来的机械应力、热膨胀失配需要解决封装长期可靠性问题。

4. 未来发展趋势

4.1 小芯片(Chiplet)和异构集成

小芯片技术将不同工艺节点、功能模块芯片进行集成。相比传统的单片设计,小芯片提供了更高的灵活性和性能。

HBM3应用:如高带宽存储(HBM3)需要每通道4-6Gbps的数据速率,封装中的I/O数量快速增长,每个硅节点的HBM数量将增加1.4倍。

4.2 2.5D与3D封装的扩展

2.5D封装:扩展EMIB技术,提高带宽密度并降低成本。

3D封装:通过垂直堆叠实现更高的性能密度,但对热管理和制造精度提出更高要求。

4.3 高密度基板技术

未来目标是将有机基板和面板级基板的性能提高到1/1μm以下,从而实现更低的电阻和更高的传输速度。

4.4 电源集成

封装内电源集成技术将进一步优化,通过局部电压调节器和高效电源传输组件,支持高功率应用。

5. 总结与展望

多芯片封装技术已经成为集成电路产业的关键方向,其优势在于提升性能、节省空间和支持多样化应用。然而,该技术仍面临基板制造、热管理、电源传输等多方面的挑战,需要从材料、工艺、设计等多个维度进行持续创新。

-

集成电路

+关注

关注

5387文章

11530浏览量

361607 -

制造工艺

+关注

关注

2文章

179浏览量

19751 -

多芯片封装

+关注

关注

0文章

4浏览量

6009

原文标题:多芯片封装(MCP)的全面解析

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【视频】智能家居系统关键技术分析与应用

软件无线电的功能结构、关键技术和难点以及应用和发展前景讨论

GPS芯片的关键技术是什么

嵌入式实时系统的关键技术是什么?

RAM技术的基本概念

智能天线的基本概念

归纳碳化硅功率器件封装的关键技术

视觉导航关键技术及应用

ptn技术要素及关键技术

电磁技术与电场的基本概念

多芯片封装的基本概念和关键技术

多芯片封装的基本概念和关键技术

评论