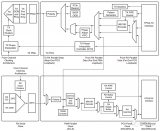

1、时钟纠正原理

时钟纠正比较简单,下面一个图就能说清楚。

首先为什么要使用时钟纠正,是因为CDR恢复的用户时钟user_clk和硬核时钟XCLK虽然频率一样,但是会有略微的不同,正是这样导致内部的FIFO有可能读空和写满,这样就会导致传输错误。与其传输出错误,不如我们就发送一个特定的序列让它去“出错”。在FIFO快满的时丢弃这个序列,在FIFO快读空时加入这个序列。由于收发双方约定好了这个序列是什么,这样可以避免出错。

2、设置buff大小

即设置最小延迟和最大延迟,buff中的内容在小于或大于这两个值时就会插入或删除特定的CC序列。设置最小延迟要求如下表。(IP核里面不用设置这个,因为提供了PPM offset核CC序列发送的周期,IP核会自己计算出来,真是智能!)

3、设置序列长度,跟上面一样,和comma码的长度有关。

4、IP核设置

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网 网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 时钟

+关注

关注

10文章

1653浏览量

130864 - cdr

+关注

关注

0文章

49浏览量

18034

发布评论请先登录

相关推荐

XilinxFPGA时钟资源概述

。

XilinxFPGA7系列分为全局

时钟(Global

clock)和局部

时钟(Regional

clock)资源。目前,大型设计

发表于07-24 11:07

•

809次阅读

请教关于C6678的serdes模块

请教:C6678的PCIE SRIO Hyperlink和SGMII模块的配置中都涉及到对

serdes模块的配置,故希望

知道以下几个问题:1、这些模块的

serdes是同

一个,还是各自有

发表于08-06 06:17

请问我可以参考哪些Spartan-6 / Artix-7文件检查这些设备的serdes是否能满足STM-4抖动要求?

您好,

Xilinx支持,你能列出哪些我可以参考的Spartan-6 / Artix-7

文件检查这些设备的

serdes是否能满足STM-4抖动要求?谢谢,特吕克以上来自于谷歌翻译以下为原文Hi

发表于07-23 12:26

为什么BUFG到DCM时钟定时错误?

输入

时钟,因此我不确定这里存在什么问题。DCM和BUFG是专用

时钟资源的

一部分,目前在.ucf中没有放置约束(我

知道它们需要在同

一个

发表于07-30 10:35

SERDES传输和引脚关联

亲爱的

Xilinx论坛,我正在实现基于

SERDES协议的序列化传输。我需要在Kintex7上接收8个差分对,这些差分对承载由另

一个Kintex7串行化的64位字,主

时钟为100MHz。

发表于03-17 09:53

SERDES在数字系统中高效时钟设计方案

SERDES在数字系统中高效

时钟设计方案,无论是在

一个FPGA、SoC还是ASSP中,为任何基于

SERDES的协议选择

一个参考

发表于02-16 11:23

•

5731次阅读

Xilinx7 Series FPGA时钟网络的区别(BUFG,BUFGR,BUFIO)

clockregion BUFR是regional

时钟网络,顾名思义,它的驱动范围只能局限在

一个

clockregion的逻辑

发表于02-08 05:31

•

2326次阅读

参考时钟对SERDES性能的影响

我们

知道,

SERDES对参考

时钟有严格的相位噪声性能要求。通常,

SERDES供应商会根据其

SERDES采用的PLL以及CDR架构特点,以及性

发表于02-10 18:40

•

6173次阅读

基于SERDES时钟的频率跟随的设计

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将

SERDES的恢复

时钟引到芯片外部,然后通过

一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随

发表于11-18 12:08

•

6401次阅读

基于FPGA芯片的SERDES接口电路设计

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的

SerDes接口,包括

SERDES收发单元,通过完全数字化的方法实现

SERDES的CDR(

ClockData

发表于05-24 15:33

•

4386次阅读

SERDES关键技术

Xilinx公司的许多FPGA已经内置了

一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做

SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收发器

时钟子系统中clock驱动实例

都要早期,因此

clock驱动是在内核中进行实现。 在内核的 drivers/clk 目录下,可以看到各个芯片厂商对各自芯片

clock驱动的实现: 下面以

一个简单的

时钟树,举例说明

SerDes是怎么设计的?(一)

的。在使用

SerDes的过程中,设计者有太多的疑惑:为什么在传输的过程中没有

时钟信号?什么是加重和均衡?抖动和误码是什么关系?各种抖动之间有什么关系?

时钟怎么恢复?等等这些问题,如果设计者能够完全理解

一文知道Xilinx Serdes时钟纠正clock correction的步骤

一文知道Xilinx Serdes时钟纠正clock correction的步骤

评论