CMSO电路:

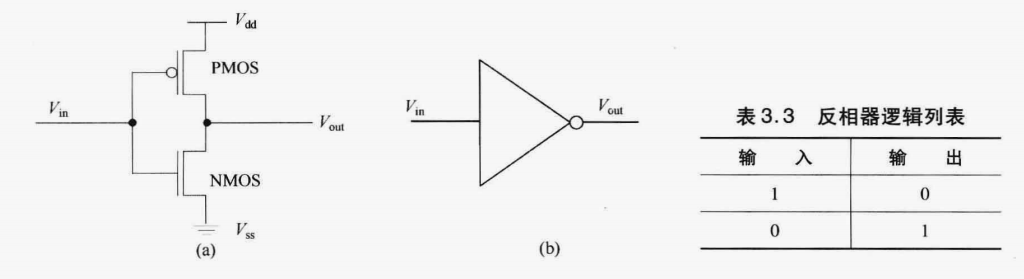

下图显示了一个CMOS反相器电路。

从图中可以看出它由两个晶体管组成,一个为NMOS,另一个为 PMOS。

当输入为高电压或逻辑1时,NMOS 就会被开启而 PMOS 会被关闭。因为输出电压为接地电压Vss,所以输出电压Vout为低电压或逻辑0。

反之,若输入为低电压或逻辑0时,NMOS 就会被关闭而 PMOS 被开启。输出电压为高电压Vdd,所以输出电压Vout为高电压或逻辑1。

由于CMOS会反转输入信号,所以被称为反相器。这个设计是逻辑电路中使用的基本逻辑单元之一。

理想状态下,Vdd和Vss之间并没有电流流动,所以CMOS的耗电量很低。CMOS反相器的主要电能损耗由高频开关转换时的漏电流形成。CMOS优于NMOS之处还包括有较高的抗干扰能力、芯片温度低、使用温度范围广和较少的定时复杂性。

将CMOS和双载流子技术结合形成的BiCMOS IC在20世纪90年代迅速发展,CMOS电路用于逻辑部分,双载流子晶体管可增加元器件的输入/输出速度。由于BiCMOS已经不再是主流产品,并且当IC的应用电压降到1V以下时就会失去应用性,所以书中并未对这种工艺做详细探讨。

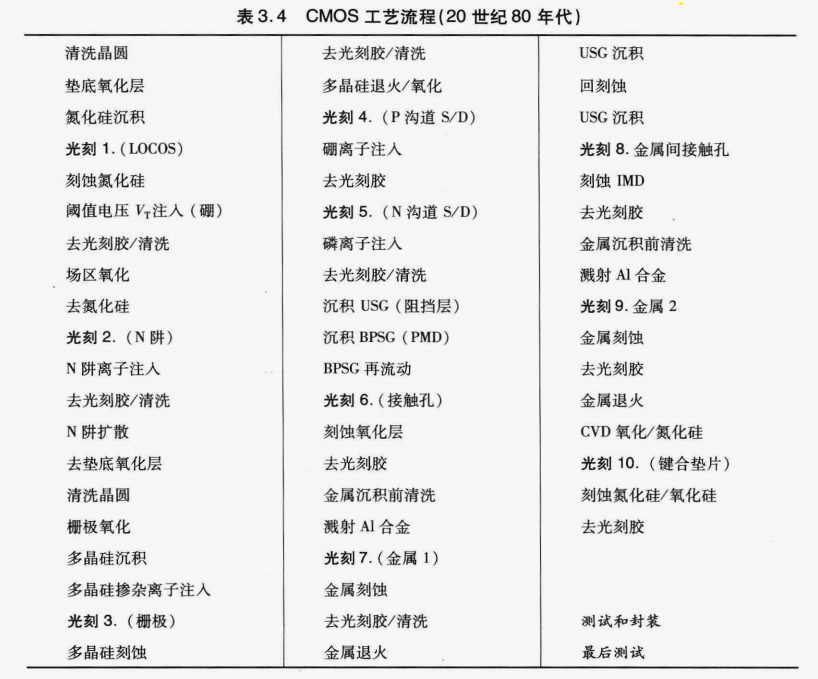

CMOS工艺(20世纪80年代):

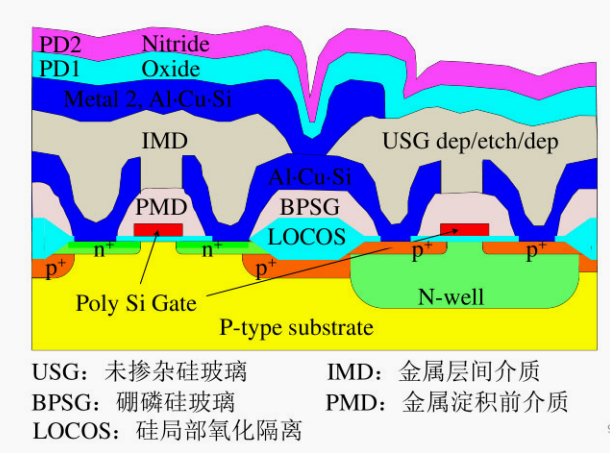

上图显示了20世纪80年代的CMOS工艺过程,晶体管之间的隔离用硅局部氧化(LOCOS)取代整面全区覆盖式氧化。

硼磷硅玻璃(BPSG)用于作为金属沉积前的电介质层(PMD)或中间隔离层(ILD0),以降低所需的再流动温度。

尺寸的缩减使大多数图形化刻蚀采用等离子体刻蚀(干法刻蚀)取代湿法刻蚀,单层金属线已不足以将IC芯片上所有的元器件按照所需的电导率连接,所以必须使用第二金属层。

20世纪80年代~90年代,金属线之间的介质沉积和平坦化是一大技术挑战,即金属层间电介质层(IMD,Inter Metal Dielectric)。20世纪80年代,最小的图形尺寸从3μm缩小到0.8μm。

CMOS的基本工艺步骤包括晶圆预处理、阱区形成、隔离区形成、晶体管制造、导线连接和钝化作用。

晶圆预处理包含外延硅沉积、晶圆清洗、对准记号刻蚀。阱区形成为NMOS和PMOS晶体管定义出器件区。阱区形成按技术发展程度的不同分为单一阱区、自对准双阱区(也称单一光刻双阱区)和双光刻双阱区。隔离技术以建立电气隔离区的方式隔绝邻近的晶体管。20世纪80年代,硅局部氧化取代了整面全区覆盖式氧化成为隔离技术的主流。晶体管制造则涉及了栅极氧化层的生长、多晶硅沉积、光刻技术、多晶硅刻蚀、离子注入以及加热处理,这些都是IC工艺中最重要的工艺步骤。导线连接技术结合了沉积、光刻和刻蚀技术定义金属线,以便连接建造在硅表面上的数百万个晶体管。最后通过钝化电介质的沉积、光刻和刻蚀技术将IC芯片密封起来与外界隔离,只保留键合垫区的开口以供测试和焊接用。

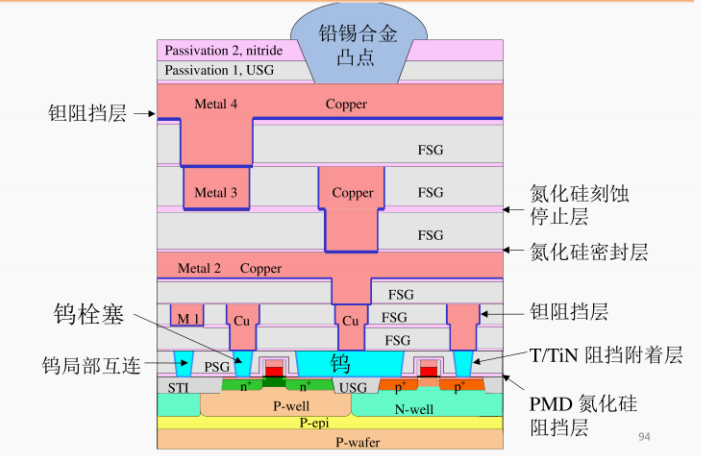

CMOS工艺(20世纪90年代):

从20世纪90年代开始,IC芯片的图形尺寸持续地从0.8μm缩减到0.18um以下,同时IC制造业也采用了一些新的技术。

当图形尺寸小于0.35um时,隔离区形成就采用浅沟槽隔离(STI)取代硅的局部氧化技术。金属硅化物广泛用于形成栅极和局部连线,钨被广泛用做不同金属层间的金属连线,即所谓的栓塞(“Plug”)。越来越多的生产线使用化学机械研磨(CMP)技术形成STI、钨栓塞和平坦化的层间电介质(ILD)。高密度等离子体刻蚀和化学气相沉积(CVD)更受欢迎,铜金属化已开始在生产线上崭露头角。下图为一个具有四层铜金属互连和一个Al/Cu合金焊盘层的CMOSIC横截面。

2000年后半导体工艺发展趋势

光学光刻波长:193nm

浸入式光刻技术、双重图形技术

自对准材料:镍硅化取代钴硅化物

低K层间介质

高K-金属栅

应变硅技术

FinFET

……

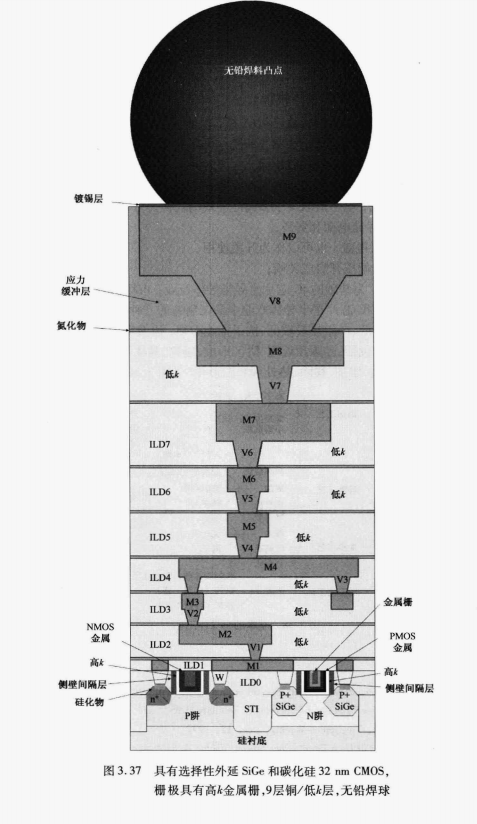

21世纪初,CMOS集成电路技术进人纳米技术节点。该技术节点从130nm缩小到32nm。193 nm波长的光成为占主导地位的光学光刻波长。浸入式光刻技术利用水在物镜和晶圆光刻胶之间作为媒介,以进一步改善图形精度,这种技术已经成为广泛使用在45nm节点及以后的IC制造中。45nm技术节点后,双重图形技术已被用于IC制造。浸入式光刻和双重图形相结合,可以帮助IC制造商进一步缩小图形尺寸。从65nm节点开始,镍硅化物取代钴硅化物作为自对准硅化物材料的选择。高k和金属栅极开始取代二氧化硅和多晶硅作为栅介质和栅电极材料。广泛应用的诸如应变硅衬底工程,通过提高载流子迁移率提高器件的性能。如双应力和选择性外延硅锗(eSiGe)技术使MOSFET沟道硅层应变增加载流子迁移率和器件速度。下图显示了一个具有选择性外延SiGe和碳化硅的32nm CMOS截面图,栅具有高k金属,9层铜互连,而且无铅焊球。

-

CMOS

+关注

关注

58文章

5710浏览量

235401 -

反相器

+关注

关注

6文章

311浏览量

43288 -

半导体芯片

+关注

关注

60文章

917浏览量

70609

原文标题:半导体芯片的制造工艺流程

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体芯片的制造工艺流程

半导体芯片的制造工艺流程

评论