verilog编译指令详解

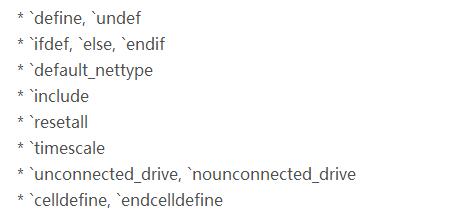

以`(反引号)开始的某些标识符是编译器指令。在Verilog 语言编译时,特定的编译器指令在整个编译过程中有效(编译过程可跨越多个文件),直到遇到其它的不同编译程序指令。完整的标准编译器指令如下:

1、`define 和`undef

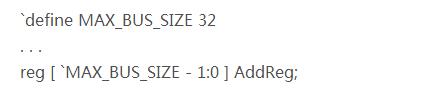

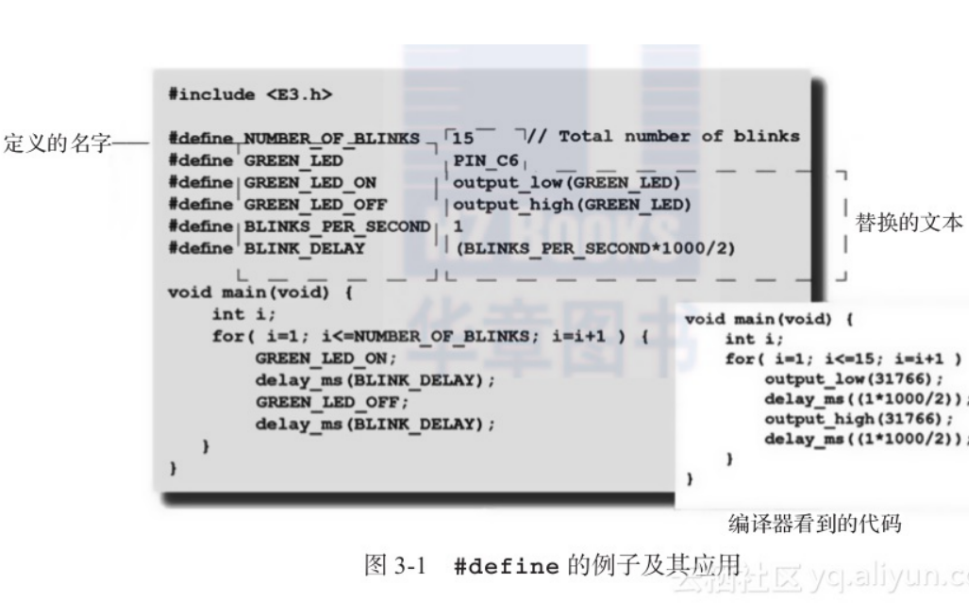

`define指令用于文本替换,它很像C语言中的#define 指令,如:

一旦`define 指令被编译,其在整个编译过程中都有效。例如,通过另一个文件中的`define指令,MAX_BUS_SIZE 能被多个文件使用。

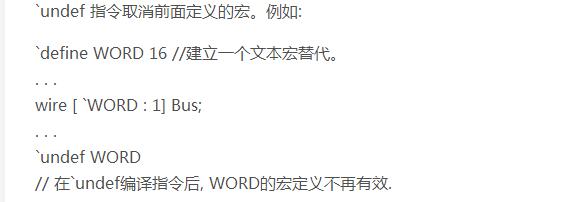

`undef 指令取消前面定义的宏。例如:

2、 `ifdef、`else 和`endif

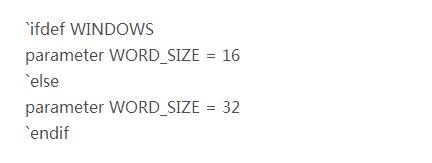

这些编译指令用于条件编译,如下所示:

在编译过程中,如果已定义了名字为WINDOWS的文本宏,就选择第一种参数声明,否则选择第二种参数说明。

`else 程序指令对于`ifdef 指令是可选的。

3、`default_nettype

该指令用于为隐式线网指定线网类型。也就是将那些没有被说明的连线定义线网类型。

`default_nettype wand

该实例定义的缺省的线网为线与类型。因此,如果在此指令后面的任何模块中没有说明的连线,那么该线网被假定为线与类型。

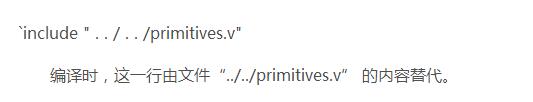

4、`include

`include 编译器指令用于嵌入内嵌文件的内容。文件既可以用相对路径名定义,也可以用全路径名定义, 例如:

5、`resetall

该编译器指令将所有的编译指令重新设置为缺省值。

`resetall

例如,该指令使得缺省连线类型为线网类型。

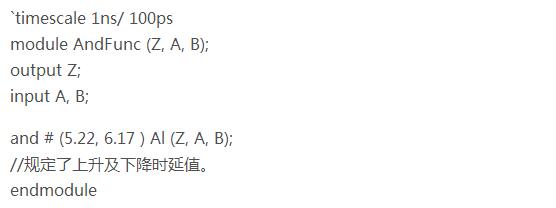

6、`timescale

在Verilog HDL 模型中,所有时延都用单位时间表述。使用`timescale编译器指令将时间单位与实际时间相关联。该指令用于定义时延的单位和时延精度。`timescale编译器指令格式为:

`timescale time_unit / time_precision

time_unit 和time_precision 由值1、10、和100以及单位s、ms、us、ns、ps和fs组成。例如:

`timescale 1ns/100ps

表示时延单位为1ns, 时延精度为100ps。`timescale编译器指令在模块说明外部出现, 并且影响后面所有的时延值。例如:

//规定了上升及下降时延值。

endmodule

编译器指令定义时延以ns为单位,并且时延精度为1/10 ns(100 ps)。因此,时延值5.22对应5.2ns, 时延6.17对应6.2 ns。如果用如下的`timescale程序指令代替上例中的编译器指令,

`timescale 10ns/1ns

那么5.22对应52ns, 6.17对应62ns。

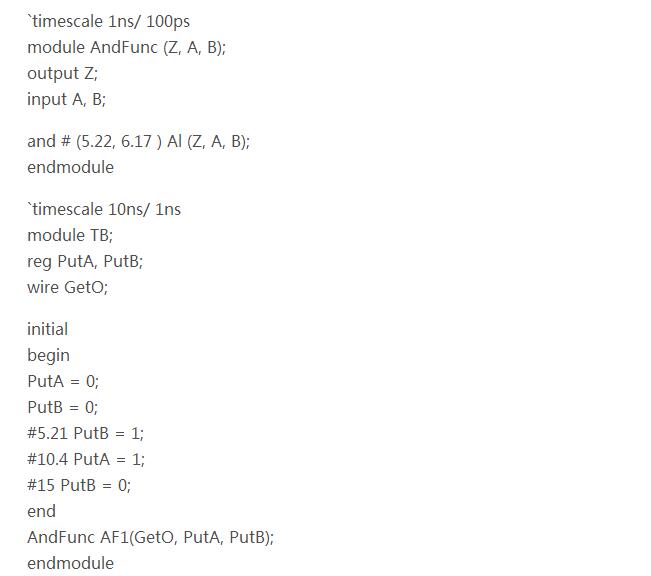

在编译过程中,`timescale指令影响这一编译器指令后面所有模块中的时延值,直至遇到另一个`timescale指令或`resetall指 令。当一个设计中的多个模块带有自身的`timescale编译指令时将发生什么?在这种情况下,vwin 器总是定位在所有模块的最小时延精度上,并且所有时 延都相应地换算为最小时延精度。例如,

在这个例子中,每个模块都有自身的`timescale编译器指令。`timescale编译器指令第一次应用于时延。因此,在第一个模块中,5.22对应5.2 ns, 6.17对应6.2 ns; 在第二个模块中5.21对应52 ns, 10.4对应104 ns, 15对应150 ns。如果仿真模块TB,设计中的所有模块最小时间精度为100 ps。因此,所有延迟(特别是模块TB中的延迟)将换算成精度为100 ps。延迟52 ns现在对应520*100ps,104对应1040*100 ps,150对应1500*100 ps。更重要的是,仿真使用100 ps为时间精度。如果仿真模块AndFunc,由于模块TB不是模块AddFunc的子模块,模块TB中的`timescale程序指令将不再有效。

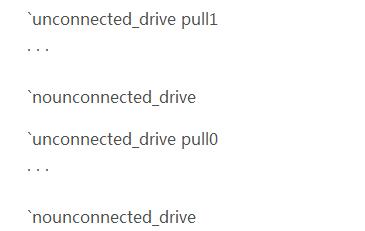

7、`unconnected_drive和`nounconnected_drive

在模块实例化中,出现在这两个编译器指令间的任何未连接的输入端口或者为正偏电路状态或者为反偏电路状态。

8、`celldefine 和`endcelldefine

这两个程序指令用于将模块标记为单元模块。它们表示包含模块定义,如下例所示。

某些PLI例程使用单元模块。

verilog编译器指示语句(数字IC)

设计者在写设计代码时,有时可能针对仿真写一些语句,这些语句可能是不为DC所接受,也不希望DC接受;设计者如果不对这些语句进行特殊说明,DC读入设计代码时就会产生语法错误。另一种情况是,设计者在写设计代码,有些设计代码是为专有的对象写的(如公司内部),这些专有的设计代码可能不希望被综合。Synopsys提供了引导语句,设计者可以使用这些引导语句控制DC综合的对象

可以利用HDL描述中的一些特定的注释语句来控制综合工具的工作,从而弥补仿真环境和综合环境之间的差异,这些注释语句称为编译器指示语句。

Verilog编译器指示语句

1、translate_off/ translate_on

这组语句用来指示DC停止翻译 “//synopsys.。.translate_off”之后的Verilog描述,直至出现 “//synopsys translate_on”。当Verilog代码钟含有供仿真用的不可综合语句时,这项功能能使代码方便地在仿真工具与综合工具之间移植。

例1(translate_off/ translate_on指示语句的使用):

//synopsys translate_off

//synopsys translate_on

2、parallel_case/ full_case

DC可能使用带优先级的结构来综合Verilog的case语句,为避免这种情况,可以使用“//synopsys.。.parallel_case”指示DC将case语句综合为并行的多路选择器结构。

(parallel_case指示语句的使用):

always @ (state)

case (state) //synopsys parallel_case

2’b00: new_state = 2’b01;

2’b01: new_state = 2’b10;

2’b10: new_state = 2’b00;

default: new_state = 2’b00;

endcase

另外,Verilog允许case语句不覆盖所有可能情况,当这样的代码由DC综合时将产生锁存器。为避免这种情况,可以使用“//synopsys full_case”指示DC所有可能已完全覆盖。

例2 (full_case指示语句的使用):

always @ (sel or a1 or a2)

case (sel) //synopsys full_case

2’b00: z = a1;

2’b01: z = a2;

2’b10: z = a1 & a2;

endcase

-

Verilog

+关注

关注

28文章

1351浏览量

110073 -

编译器

+关注

关注

1文章

1623浏览量

49107 -

Verilog语言

+关注

关注

0文章

113浏览量

8224

发布评论请先 登录

相关推荐

循环模型编译器Verilog和System Verilog语言支持指南

NICE自定义指令如何被编译生成汇编文件和.verilog二进制文件?

编译器是如何工作的_编译器的工作过程详解

C语言编译器常见的预编译指令详细资料说明

Verilog可综合的循环语句

Verilog教程之Verilog HDL程序设计语句和描述方式

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

交叉编译器安装教程

Verilog中的If语句和case语句介绍

verilog编译指令_verilog编译器指示语句(数字IC)

verilog编译指令_verilog编译器指示语句(数字IC)

评论