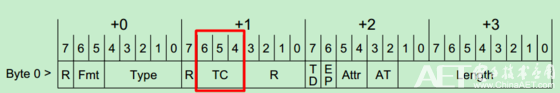

PCIe总线设计之初,主要是针对于音频和视频传输等这些对时间要求特别敏感的应用的。为了保证这些特殊应用的数据包能够得到优先发送,PCIe Spec中为每一个包都分配了一个优先级,通过TLP的Header中的3位(即TC,Traffic Class)。

如下图所示:

TC值越大,表示优先级越高,对应的包也就会得到优先发送。一般来说,支持QoS(Quality of Service)的PCIe总线系统,对于每一个TC值都会有一个独立Virtual Channel(VC)与之对应。这个Virtual Channel实际上就是一个Buffer,用于缓存数据包。

注:当然也有那些只有一个VC Buffer的,此时不管包的TC值如何,都只能缓存在同一个VC Buffer中,自然也就没有办法保证按优先级传输了。这样的PCIe设备称之为不支持QoS的PCIe设备。

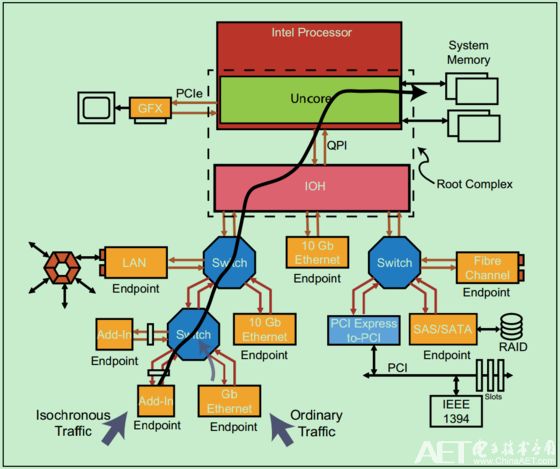

一个简单的QoS的例子如下图所示:

图中左下角的Endpoint(即Isochronous Traffic)的优先级比右边的Endpoint(即Ordinary Traffic)的优先级要高。因此,在Switch中,来自左边的Endpoint的包会得到优先传输。而Switch的这种判决操作叫做端口仲裁(Port Arbitration)。

默认情况下,VC Buffer中的数据包是按照包达到的时间顺序,依次放入VC Buffer中的。但是也并不是总是这样,PCIe总线继承了PCI/PCI-X总线关于Transaction-Ordering和Relaxed-Ordering的架构,但也只是针对相同的TC值才有效。关于Transaction-Ordering和Relaxed-Ordering,大家可以去参考PCI-X的Spec,这里不再详细地介绍。

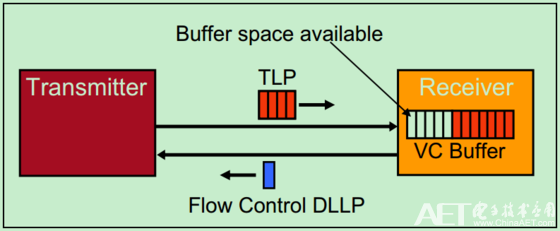

对于大部分的串行传输协议而言,发送方能够有效地将数据发送至接收方的前提是,接收方有足够的接收Buffer来接收数据。在PCI总线中,发送方在发送前并不知道接收法是否有足够的Buffer来接收数据(即接收方是否就绪),因此经常需要一些Disconnects和Retries的操作,这将会严重地影响到总线的传输效率(性能)。

PCIe总线为了解决这一问题,提出了Flow Control的概念,如下图所示。PCIe总线中要求接收方必须经常(在特定时间)向发送方报告其VC Buffer的使用情况。而报告的方式是,接收方向发送方发送Flow Control的DLLP(数据链路层包),且这种DLLP的收发是由硬件层面上自动完成的,并不需要人为的干预。需要注意的是,虽然这一操作旨在数据链路层之间进行,但是这些VC Buffer的使用情况对于应用层(软件层)也是可见的。

采用Flow Control机制的PCIe总线,相对于PCI总线获得了更高的总线利用率。虽然增加了Flow Control DLLP,但是这些DLLP对带宽的占用极小,几乎对总线利用率没有什么影响。

-

总线

+关注

关注

10文章

2878浏览量

88051 -

PCIe

+关注

关注

15文章

1234浏览量

82575

原文标题:【博文连载】PCIe扫盲——PCIe总线事务层入门(三)

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCIe总线的通信机制

PCIe总线必须要先完成Flow Control初始化

PCIe扫盲—PCIe错误检测机制的详细资料概述

PCIe总线的热插拔机制

PCIe错误报告的两种机制详解

PCIe 9110IM PCIe总线转CAN设备手册

CET为何而生?CET安全防御机制解析

扒一扒PCIe中的Flow Control

PCIe热插拔机制介绍

采用Flow Control机制的PCIe总线

采用Flow Control机制的PCIe总线

评论