在一篇以前的文章中,Timothy T.曾谈到JESD204B接口标准(该标准越来越受欢迎,因为它能在高速数据采集系统里简化设计)的时钟要求。在本文中,笔者将谈论抖动合成器与清除器的不同系统参考信号(SYSREF)模式,以及如何用它们来最大限度地提高JESD204B时钟方案的性能。

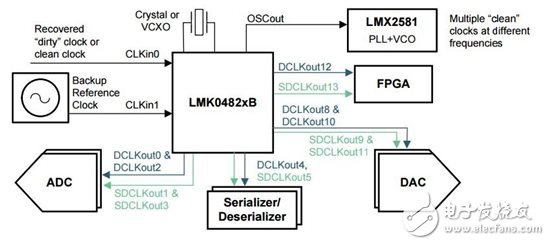

LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们是高性能的双环路抖动清除器,可在具有器件和SYSREF时钟的子类1时钟方案里驱动多达七个JESD204B转换器或逻辑器件。图1是典型JESD204B系统(以LMK04821系列器件作为时钟解决方案)的高级方框图。

图1:典型的JEDEC JESD204B应用方框图

LMK04821凭借来自第二锁相环(PLL)电压控制振荡器的单个SYSREF时钟分频器来产生SYSREF信号。信号从分频器被分配到个别的输出路径。每个输出路径均包含数字和vwin 延迟,以调节与器件时钟有关的SYSREF相位。

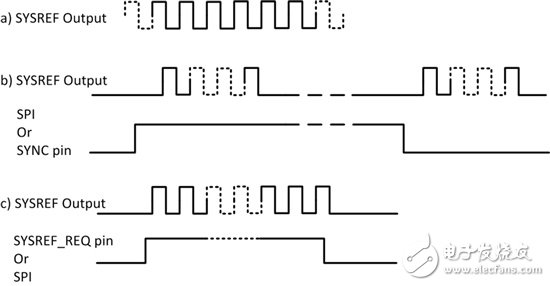

根据JESD204B标准,SYSREF可采用不同的模式,如图2所示。它可以是连续性(也称为周期性)、有间隙的周期性或一次性信号。连续性和有间隙的周期性SYSREF的周期必须是本地多帧时钟(LMFC)的整数倍,以避免多帧中间的SYSREF脉冲。

连续性模式允许连续性输出。由于从SYSREF至器件时钟存在串扰,因此许多开发人员不用连续性模式。但是,连续性模式使系统开发人员能在两个信号之间手动设置恰当的确定性相位关系。设置后,它可变为有间隙的周期性SYSREF。

在有间隙的周期性或一次性模式中,SYSREF时钟分频器的输出通过脉冲发生器被馈送给输出路径。脉冲发生器用门控制SYSREF信号,只让少数脉冲通过。脉冲数可被设定为一个、两个、四个或八个。因为没有周期性信号,所以从SYSREF至器件时钟的串扰被最大限度地减少。

LMK0482x中另一类有间隙的周期性SYSREF模式是请求模式,只要SYNC/SYSREF_REQ引脚为高电平,该模式就能输出SYSREF脉冲的连续流。

图2:LMK0482x的SYSREF模式是:a)连续性SYSREF;b)脉冲式SYSREF(一次性或有间隙的周期性模式);c)SYSREF请求(有间隙的周期性模式)

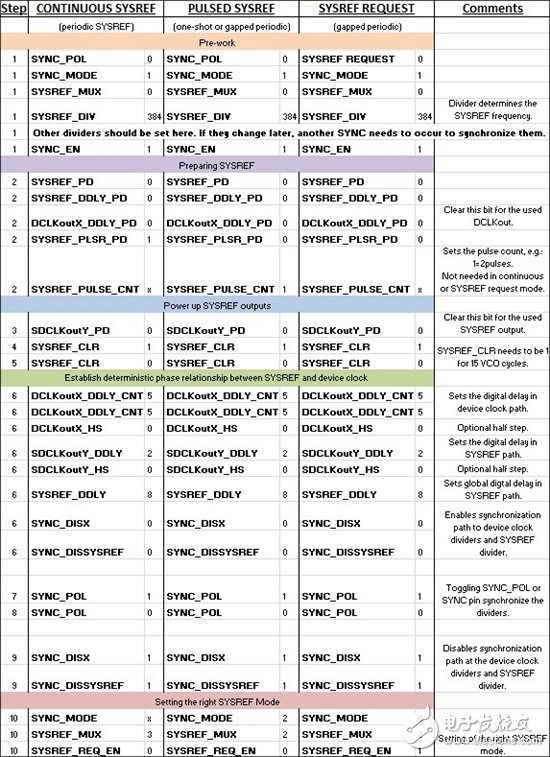

在LMK04821器件中,内部SYSREF分配路径与输出分频器同步路径共享。因此,它需要一个特定的寄存器写入序列,以支持同步输出和无干扰SYSREF脉冲的产生。在表1中,笔者描述的方法都与它们的寄存器写入序列一起列出。表1还展示了内容为十进制值的内部寄存器字段名。具有相同编号的步骤可以互换。

表1:能启用不同SYSREF模式的寄存器写入序列

JESD204B标准是减少布局工作量,同时在信号转换器和逻辑器件之间采用串行化数据传输。通过充分利用JESD204B致能时钟器件的SYSREF模式,您可在整个系统中轻松创建确定性的相位关系。

在JESD204B设计等方面,有没有您希望我们谈及的其它时钟设计挑战?欢迎通过登录在下边发表评论来告知笔者。

-

实时时钟

+关注

关注

4文章

245浏览量

65767 -

JESD204B

+关注

关注

5文章

76浏览量

19125

发布评论请先 登录

相关推荐

JESD204B使用说明

调试ADS52J90板卡JESD204B接口遇到的问题求解

在FPGA里面例化了8个jesd204B的ip核同步接收8块AFE芯片的信号,怎么连接设备时钟和sysref到AFE和FPGA?

使用JESD204B接口,线速率怎么计算?

如何配置LMK04828时钟芯片生成JESD204b需要的时钟?

ADC16DX370 JESD204B串行链路的均衡优化

从JESD204B升级到JESD204C时的系统设计注意事项

采用JESD204B的LMK5C33216超低抖动时钟同步器数据表

LMK0482x超低噪声JESD204B兼容时钟抖动消除器数据表

LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表

抓住JESD204B接口功能的关键问题

如何实现JESD204B时钟方案最大性能

如何实现JESD204B时钟方案最大性能

评论