Intel 10nm工艺还在苦苦挣扎,台积电和三星已经开始量产7nm,下一步自然就是5nm,台积电近日也首次公开了5nm的部分关键指标,看起来不是很乐观。

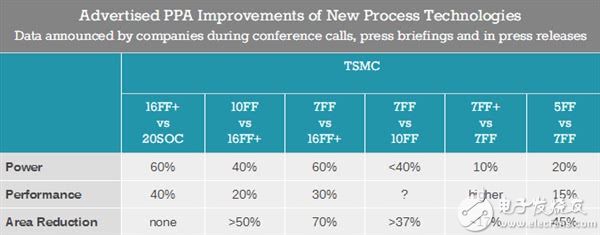

明年,台积电的第二代7nm工艺会在部分非关键层面上首次尝试使用EVU极紫外光刻系统,工艺节点从CLN7FF升级为CLN7FF+,号称晶体管密度可因此增加20%,而在同样密度和频率下功耗可降低10%。

台积电5nm(CLN5)将继续使用荷兰ASML Twinscan NXE: 3400 EUV光刻机系统,扩大EUV的使用范围,相比于第一代7nm晶体管密度可猛增80%(相比第二代则是增加50%)。

看起来很厉害,不过能带来的实际频率提升只有15%,而同等密度和频率时功耗也只能降低20%,对比第二代7nm提升就更有限了。

不过台积电还提供了一个名为“极低阈值电压”(ELTV)的可选项,号称能将频率提升幅度增加到25%,但未解释具体是如何做到的。

工艺不断演进,但是带来的提升却越来越有限,足以显示半导体技术难度和复杂度的急剧增加,当然也不排除台积电这几年在工艺命名上太任性,不像Intel那么老老实实。

如此有限的提升,不知道能不能吸引客户跟进,毕竟要充分考虑成本的。好消息是台积电这几代新工艺,大家都是“趋之若鹜”,比如7nm到今年底将有50多款芯片流片,覆盖从高性能到嵌入式各种领域。

目前,台积电EUV 7nm工艺的基础IP已经完成芯片验证,但是嵌入式FPGA、HBM2、GDDR5等关键模块要到今年底或明年初才能完成,5nm则会在今年7月完成0.5版本,大量IP模块诸如PCI-E 4.0、DDR4、USB 3.1则要等到2019年。

设备方面,台积电将为5nm开设一座新的晶圆厂Fab 8,引入多台新光刻机,但是目前EUV光刻机的平均日常功率只有145W,部分可以持续几周做到250W,都不足如完全投入商用,预计要到今年晚些时候才能达到300W,仍需进一步改进。

还有EUV光刻掩膜材料的问题,目前极紫外线的通透率只有83%,明年才能超过90%。

-

台积电

+关注

关注

44文章

5632浏览量

166406

发布评论请先 登录

相关推荐

台积电2nm制成细节公布:性能提升15%,功耗降低35%

台积电分享 2nm 工艺深入细节:功耗降低 35% 或性能提升15%!

EUV极紫外真难!台积电首次揭秘5nm:频率仅提升15%

EUV极紫外真难!台积电首次揭秘5nm:频率仅提升15%

评论