MCS-51单片机是一种集成的电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、vwin 多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的计算机系统。本文主要详解MCS-51与中断有关的寄存器、中断入口地址及编号,具体的跟随小编一起来了解一下。

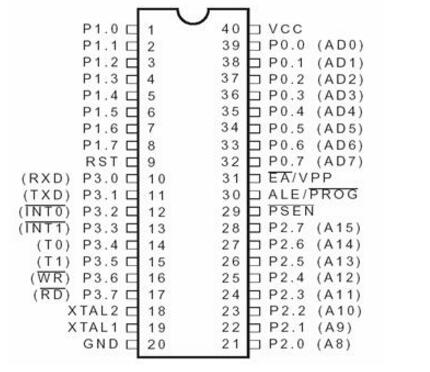

MCS-51单片机引脚图及功能

1、电源

Vcc:芯片电源,一般为+5V;

Vss:接地端。

2、时钟

XTAL1和XTAL2:晶体振荡电路反相输入端和输出端。当使用内部振荡电路时,需要外接晶振,常见有的4M、6M、11.0592M、12M等。当使用外部振荡输入时XTAL1接地,XTAL2接外部振荡脉冲输入。

3、控制线

MCS-51单片机的控制线共有4根,其中3根是复用线,具有两种功能。

(1)ALE/PROG:地址锁存允许/编程脉冲。

ALE:正常使用时为ALE功能,主要用来锁存P0口送出的8位地址。P0口一般分时传送低8位地址和数据信号,且均为二进制数。区分是否是低8位数据信号还是地址信号就看ALE引脚。当ALE信号有效时,P0口传送的是低8位地址信号;当ALE无效时,P0口传送的是8位数据信号。一般在ALE引脚的下降沿锁定P0口传送的内容,即低8位地址信号。

当CPU不执行访问外部RAM指令(MOVX)时,ALE以时钟振荡频率1/6的固定频率输出,所以ALE信号也可以作为外部芯片的时钟信号。但当CPU执行访问外部RAM(MOVX)时,ALE将跳过一个ALE脉冲。

PROG:当单片机在编程期间,该引脚输入编程脉冲(由编程器提供)。

(2)PSEN:外部ROM读选通信号。

当单片机读外部ROM时,每个机器周期内PSEN两次有效输出。PSEN就相当于外部ROM芯片输出允许的选通信号。但读片内ROM和读片外RAM时无效。

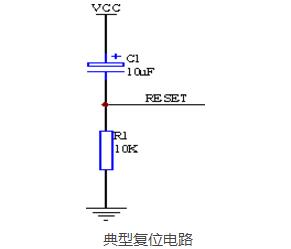

(3)RST:复位引脚。

RST为单片机上电复位输入端,只要在该引脚上连续保持两个机器周期以上的高电平,单片机就可以实现复位操作,复位后程序从0000H处开始执行。在一般应用中可以用RC电路来实现单片机的上电复位,在一些工业控制等要求较高的场合一般用专用的看门狗芯片进行复位及电源监控,典型的RC上电复位电路如图所示:

(4)EA/VPP:内外ROM选择/EPROM编程电源。

EA:正常工作时,EA为内外ROM选择端。MCS-51型单片机的寻址范围为64KB,其中4K在片内,60K在片外,当EA为高电平时,先访问片内ROM,当程序长度超过4K时将自动转向执行外部ROM中的程序。当EA为低电平时单片机只访问外部ROM,对老的8031单片机(因片内没有ROM),EA必须接地。目前的大部分单片机都自带ROM,所以一般应用中也将EA接高电平。

VPP:对于有内部EPROM的单片机,在片内EPROM编程期间,此引脚用于施加编程电源。

4、I/O引脚

MCS-51单片机共有4个8位并行I/O端口,共32个可编程I/O引脚。四个I/O口各有各的功能,在一般情况下,P0专用于分时传送低8位地址信号和8位数据信号,P2口专用于传送高8位地址信号,P3口大部分时间用于第二功能。当然所有I/O口都可以做为普通的输入/输出端口用。

MCS-51与中断有关的寄存器、中断入口地址及编号

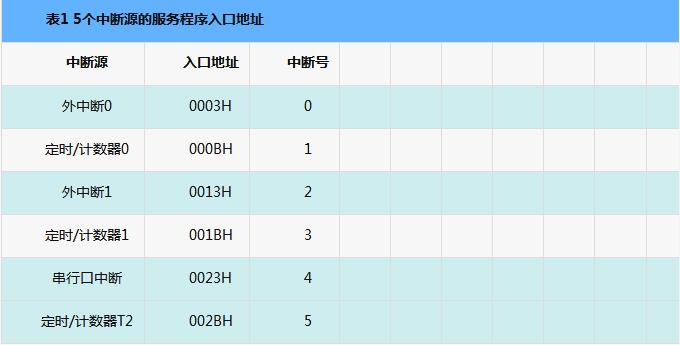

一、中断入口地址及编号

MCS-51在每一个机器周期顺序检查每一个中断源,在机器周期的S6按优先级处理所有被激活的中断请求,此时,如果CPU没有正在处理更高或相同优先级的中断,或者现在的机器周期不是所执行指令的最后一个机器周期,或者CPU不是正在执行RETI指令或访问IE和IP的指令(因为按MCS-51中断系统的特性规定,在执行完这些指令之后,还要在继续执行一条指令,才会响应中断),CPU在下一个机器周期响应激活了的最高级中断请求。

中断响应的主要内容就是由硬件自动生成一条长调用LCALL addr16指令,这里的addr16就是程序存储器中相应的中断区入口地址,这些中断源的服务程序入口地址如下:

生成LCALL指令后,CPU紧跟着便执行之。首先将PC(程序计数器)的内容压入堆栈保护断点,然后把中断入口地址赋予PC,CPU便按新的PC地址(即中断服务程序入口地址)执行程序。

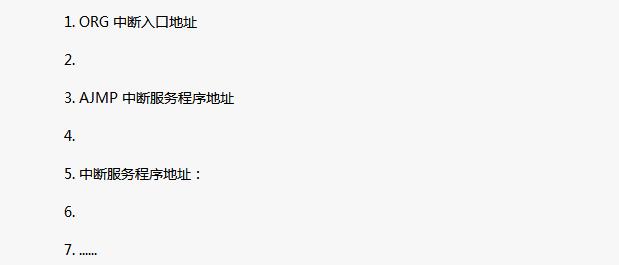

值得一提的是,各中断区只有8个单元,一般情况下(除非中断程序非常简单),都不可能安装下一个完整的中断服务程序。因此,通常是在这些入口地址区放置一条无条件转移指令,使程序按转移的实际地址去执行真正的中断服务程序。

对于汇编,中断函数的一般形式为:

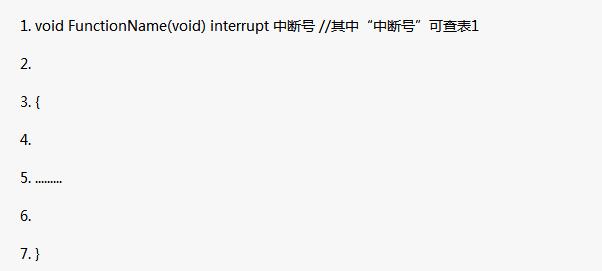

对于C语言,中断函数的一般形式为:

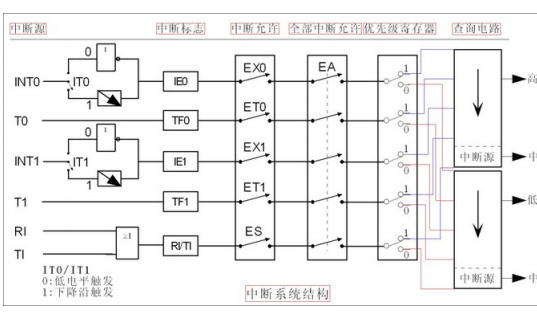

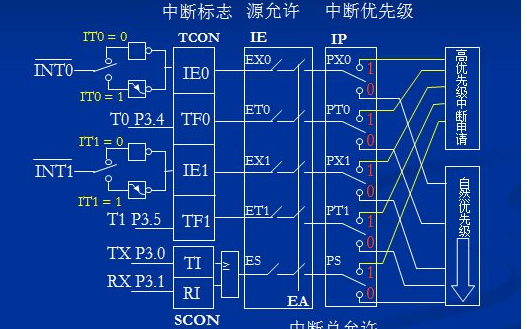

二、与中断有关的寄存器

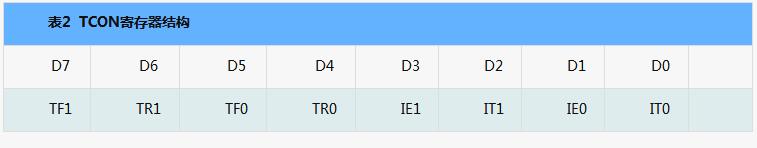

1、定时器控制寄存器TCON

IE1:外部边沿触发中断1请求标志,其功能和操作类似于TF0。

IT1:外部中断1类型控制位,通过软件设置或清除,用于控制外中断的触发信号类型。IT1=1,边沿触发。IT=0是电平触发。

IE0:外部边沿触发中断0请求标志,其功能和操作类似于IE1。

IT0:外部中断0类型控制位,通过软件设置或清除,用于控制外中断的触发信号类型。其功能和操作类似于IE1。

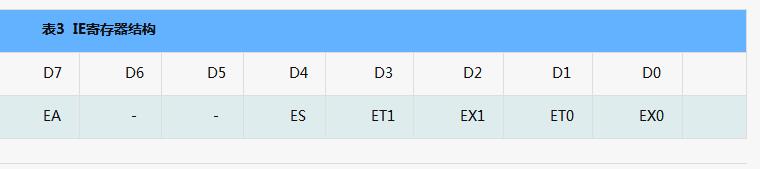

2、 中断允许寄存器IE

EA:中断总控制位,EA=1,CPU开放中断。EA=0,CPU禁止所有中断。

ES:串行口中断控制位,ES=1允许串行口中断,ES=0,屏蔽串行口中断。

ET1:定时/计数器T1中断控制位。ET1=1,允许T1中断,ET1=0,禁止T1中断。

EX1:外中断1中断控制位,EX1=1,允许外中断1中断,EX1=0,禁止外中断1中断。

ET0:定时/计数器T0中断控制位。ET1=1,允许T0中断,ET1=0,禁止T0中断。

EX0:外中断0中断控制位,EX1=1,允许外中断0中断,EX1=0,禁止外中断0中断。

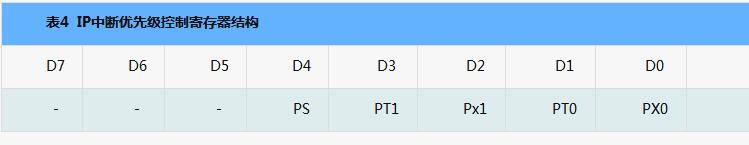

3、中断优选级控制寄存器IP

PS:串行口中断口优先级控制位,PS=1,串行口中断声明为高优先级中断,PS=0,串行口定义为低优先级中断。

PT1:定时器1优先级控制位。PT1=1,声明定时器1为高优先级中断,PT1=0定义定时器1为低优先级中断。

PX1:外中断1优先级控制位。PT1=1,声明外中断1为高优先级中断,PX1=0定义外中断1为低优先级中断。

PT0:定时器0优先级控制位。PT1=1,声明定时器0为高优先级中断,PT1=0定义定时器0为低优先级中断。

PX0:外中断0优先级控制位。PT1=1,声明外中断0为高优先级中断,PX1=0定义外中断0为低优先级中断。

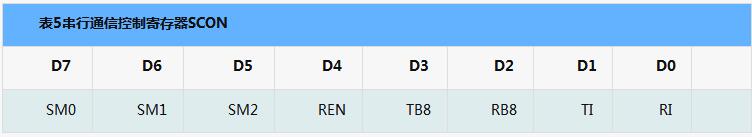

4、串行通信控制寄存器SCON

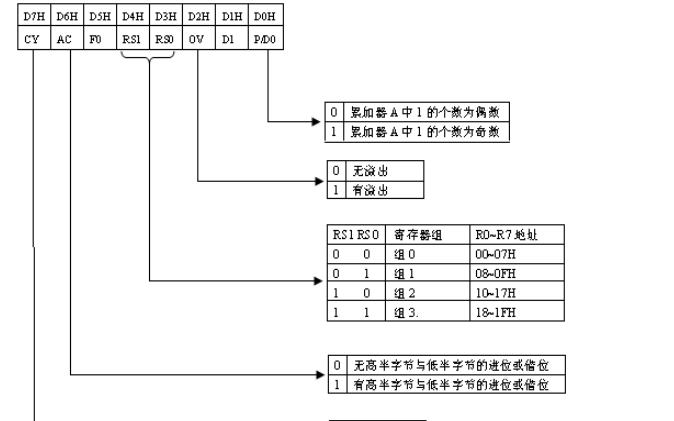

它是一个可寻址的专用寄存器,用于串行数据的通信控制,单元地址是98H,其结构格式如下:

TI:发送中断标志位。

方式0时,发送完第8位数据后,由硬件置位,其它方式下,在发送或停止位之前由硬件置位,因此,TI=1表示帧发送结束,TI可由软件清“0”。

RI:接收中断标志位。

接收完第8位数据后,该位由硬件置位,在其他工作方式下,该位由硬件置位,RI=1表示帧接收完成。

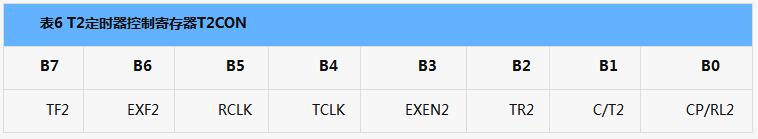

5、T2状态控制寄存器T2CON

TF2:T2溢出中断标志。TF2必须由用户程序清“0”。当T2作为串口波特率发生器时,TF2不会被置“1”。

EXF2:定时器T2外部中断标志。EXEN2为1时,当T2EX(P1.1)发生负跳变时置1中断标志DXF2,EXF2必须由用户程序清“0”。

EXEN2:T2的外部中断充许标志

-

单片机

+关注

关注

6035文章

44554浏览量

634577 -

寄存器

+关注

关注

31文章

5336浏览量

120224 -

MCS-51

+关注

关注

2文章

126浏览量

29328

发布评论请先 登录

相关推荐

MCS-51的中断响应过程解析

单片机中断系统的结构

MCS-51单片机系统结构

MCS-51中断系统中的复位问题

单片机中断系统和中断控制寄存器与中断响应的详细资料说明

MCS-51与中断有关的寄存器、中断入口地址及编号详解

MCS-51与中断有关的寄存器、中断入口地址及编号详解

评论