0 引言

随着现代科技的发展,航天系统、武器装备等领域对系统可靠性要求与日俱增[1-3]。为保证嵌入式控制系统的可靠性,针对嵌入式控制系统的测试尤为重要。针对系统重要的控制信号的检测及分析,直接关系到整个控制系统功能的正确性及安全性,同时在系统研究及生产领域发挥着十分重要的作用,并且不同嵌入式控制系统的输出信号的能力及状态不同。因此,时序信号监测系统的小型化、智能化、通用化是亟待解决的重要课题。

PC104是一种嵌入式计算机平台,与PC兼容,具有灵活的可扩展性,其尺寸小、功能强的特点非常适合嵌入式系统的应用[4,5]。本文基于PC104架构搭建了小型化的时序信号监测系统,以运放AD620实现外界时序信号的处理及转化,以国产BQV300 FPGA完成数字信号数据的采集,通过ISA总线完成数据到主控设备的传输,使用国产SPARC V8处理器完成信号的解析处理。时序信号监测系统对外提供网络通信模块及异步串口通信模块。用户可以根据需要,实现数据与主机之间的通信,最终在上位机软件对各项时序信号进行实时监测及处理。

1 系统整体设计

本文从硬件设计、软件设计等方面阐述高低压时序信号监测系统的整体设计构架。

1.1 硬件组成

高低压时序信号监测系统可以进行定制化组合。主要由主控单元模块、高低压测量模块、电源模块、测试电缆等组成。高低压时序测量模块可随意增减,每个高低压测量模块可以20路信号测量,以100路为例,硬件组成框架如图1所示。

测量系统各个模块采用标准PC104结构设计,通过ISA总线进行主控计算机及高低压时序采集模块的信息通信,其功能可实现对电压信号脉冲及恒流信号脉冲的测量。

1.2 功能设计

1.2.1 主控模块功能

主控计算机模块是整个时序监测系统的对内对外控制中心。其主要由CPU、SDRAM、ISA总线转换、Flash、以太网、扩展UART、PWM、总线驱动、电源变换等9个功能子模块组成。

主控计算机模块是面向控制应用,采用国产化SPARC V8处理器而研制的一种兼容PC/104规范的嵌入式计算机模块。该模块采用国产SPARC-V8处理器BM3110,支持VxWorks操作系统,对外提供交互支持。设计采用PC104主从模式控制模式,对内与高低压信号采集模块进行实时的数据传输,对外提供多元的交互通信通道,供操作者获取采样数据信息,具体结构如图2所示。

主控模块通过FPGA扩展接口输出,支持PC104总线16/8位模式,实现了128 MB SDRAM和256 MB Flash存储器,3路RS232串行通信接口,2路可冗余备份10 M/100 M自适应以太网接口。支持VxWorks操作系统,实现了TFFS文件系统。在整个时序信号监测系统起着信息数据承上启下的作用,是整个系统的核心模块。

1.2.2 从设备模块功能

高低压信号采集模块是整个测试系统的功能机理实现模块,作为从设备实现20路vwin 信号转化采集测量功能。本模块由继电器控制板卡测量模式转化,通过运放调理电路对信号进行放大和转换,光耦隔离电路进行信号隔离,国产FPGA电路实现时序信号处理、存储和传输。

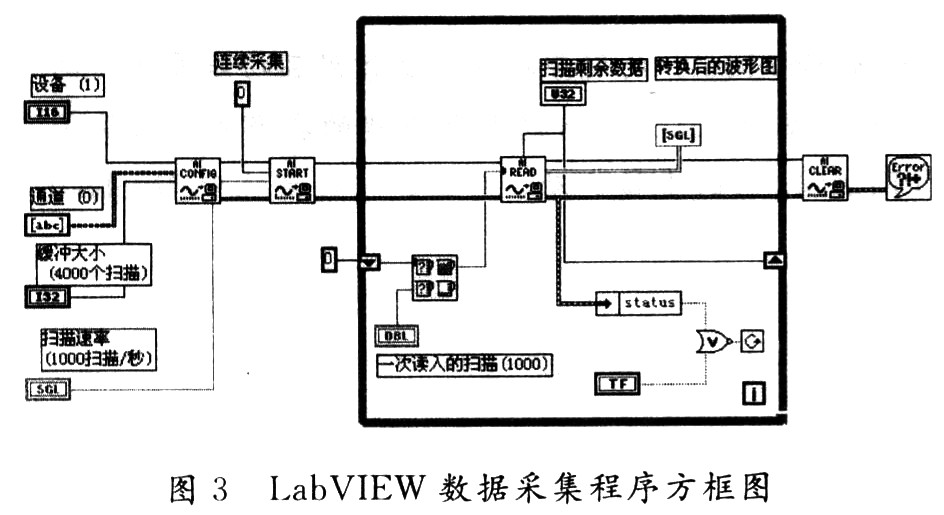

限于空间、体积的要求,设计实现两块板卡组成PC104高低压时序测量模块,原理框图如图3所示。模块分为数字电路板卡及模拟电路板卡,两块板卡之间信号通过接插件连接。模拟电路板卡主要为模拟电路,核心器件包括继电器、放大电路、基准电路、比较器,主要功能为实现信号切换和处理功能。数字电路板卡主要为数字电路,核心器件为FPGA、光耦、电源模块,主要提供信号控制及与PC104主板通信接口功能。

模拟电路板卡在硬件上主要划分为信号采集切换电路、信号处理电路及信号接口电路。其中,信号采集切换电路接收外部信号,可以根据数字电路板卡发送的信号完成高/低压信号电路的切换;信号调理电路,包括信号运放电路、基准电路、比较电路,实现信号的过滤处理,转换成符合数字电路要求的波形输出;信号接口电路实现数字电路板卡与模拟电路板卡之间的信号通路,获得数字电路板卡电源模块产生的供电信号,接收数字电路板卡传输过来的切换控制信号,发送采集到的波形信号。

数字电路板卡硬件上主要划分为电源模块电路、FPGA相关电路、隔离电路、PC104总线接口电路和信号接口电路。电源模块接收外部电源信号,转换成板卡各个模块需要有效电源信号,完成模拟电路板卡及数字电路板卡上器件的供电;隔离电路则完成模拟信号到数字信号的隔离工作,供FPGA处理;FPGA相关电路,完成FPGA周围信号的输入、输出,FPGA则实现所有信号的处理解析;PC104总线接口模块负责PC104总线信号的传输,完成PC104高低压时序板卡与PC104主控板卡之间的交互,实现主控板卡对测量板卡的控制及波形信息的采集;信号接口电路功能同模拟电路上的信号接口电路,负责电源信号、控制信号、波形信号在两个板卡之间的传输。

1.3 软件设计

信号监控系统分为下位机软件及上位机软件设计,通过数据传输协议进行数据交互,完成整套监控系统功能输出。

1.3.1 下位机软件设计

下位机采用VxWorks嵌入式操作系统作为开发环境,因此设计思路采用黑箱实现采集解析功能,通过对外通信接口向上位机发送最终数据,尽量减少上位机的工作。为了简化功能,采用模块化设计,其主要由自检功能模块、信号采集模块、数据存储模块、数据交互模块组成。这样不仅简化了设计流程,同时增强软件的健壮性[6]。具体软件流程如图4所示。

下位机软件上电启动后首先对整个系统进行自检测试。若自检失败,则发送自检错误帧到上位机进行报警;若自检正常,则进行系统功能配置,开始数据采集;当采集到有效数据时备份到文件系统,同时发送数据到上位机。

1.3.2 上位机软件设计

上位机为用户提供显示界面。根据通信接口获取下位机采集处理后的测量数据帧信息,并且逐条解析,根据数据协议提取关键信息,并实时显示到显示终端供用户分析。同时,上位机可以及时汇报时序监控系统状态信息,进行实时预警。具体流程图如图5所示。

1.3.3 交互协议设计

由于下位机主控计算机模块提供多种通信接口,因此上位机可以根据实际硬件选择。本设计采用网络接口,使用UDP协议进行数据传输。为保证数据传输可靠,在UDP有效数据段增加可靠性设计。具体帧格式为:帧头、帧类型、数据字段、校验、帧尾。下位机发送数据帧到上位机后,有上位机软件获取到一条UDP数据后,首先要检查数据校验是否正确,当确定为一条有效帧后,根据帧类型判断当前帧数据内容格式,提取有效数据字段,进而做相应的处理。

2 性能

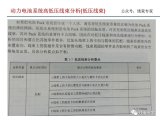

PC104的高低压时序信号监测系统产品成熟后,本文分别对不同阈值参数的高压信号及低压信号进行脉宽测试,测试结果如表1、表2所示。

该产品恒压信号测量阈值范围在20 V~36 V,测量精度在1%;恒流信号测量阈值在10 mA~200 mA,测量精度可以控制在2%以内,满足大多数控制系统应用信号要求。产品经过一定量级的环境试验及压力测试,测量的稳定性和一致性较高。

3 结语

本文提出一种基于PC104系统结构设计的高低压时序信号监测系统,其具有可扩展化、小型化、模块化等特点。其硬件资源丰富,支持多任务和VxWorks嵌入式实时操作系统,速度快、精度高、功能强大,可以有效运行采集信号处理算法,提高了系统的可靠性。通过利用FPGA、SOC等先进电子元器件实现了较高的集成度,在保证实时性和可靠性的情况下,有效地减少了系统功耗,降低了成本。

-

FPGA

+关注

关注

1629文章

21729浏览量

602955 -

PC104

+关注

关注

5文章

52浏览量

67411 -

信号监测

+关注

关注

0文章

11浏览量

8350

发布评论请先 登录

相关推荐

CPLD控制PC104总线时序问题

使用VHDL语言和FPGA的DSP HPI口与PC104总线接口设计

怎么设计基于PC104总线的实时信号采集处理系统?

基于PC104的陀螺仪动态测试系统设计

基于DSP与PC104高速通信接口设计

一文带您熟悉pc104故障监控平台

关于基于PC104的高低压时序信号监测系统

关于基于PC104的高低压时序信号监测系统

评论