1芯片选型

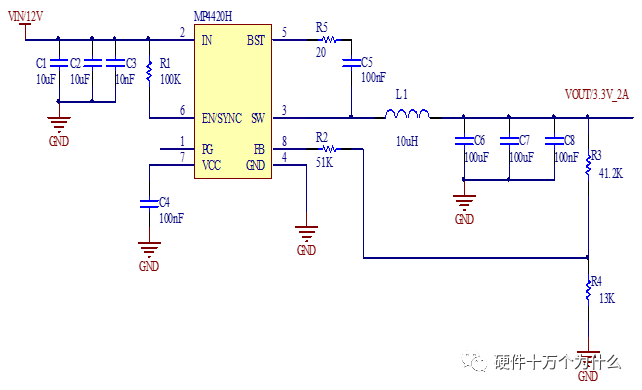

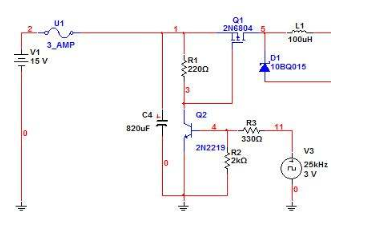

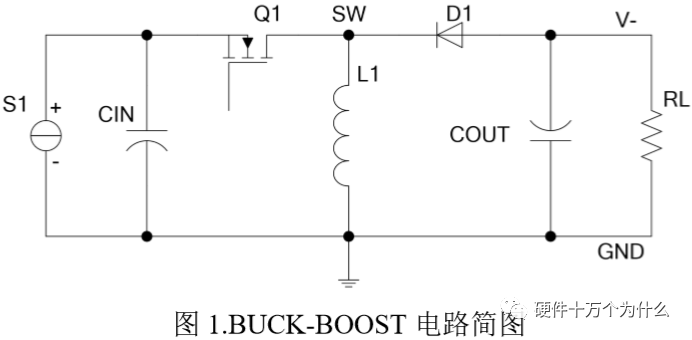

如下图1所示为本模块的电路原理图,具体可以简化为输入部分、控制部分、输出部分以及反馈部分。输入部分:电容C1、C2、C3以及R1;控制部分:MP4420H芯片以及自举电路C5、R5;输出部分:电感L1、电容C6、C7以及C8。反馈部分:电阻R3、R4以及R2。

图1 电源模块原理图

本模块需要实现一个DC-DC的电源转换功能,其输入为12V,输出为3.3V/2A。选择MP4420H这款芯片,MP4420H的输入范围为4V-36V之间,输出电压范围为0.8V-32.4V,最大输出电流2A。MP4420H的特点有:内置两只开关管且采用同步BUCK的技术、开关频率为450KHZ、内部实现软启动、占空比最大可达到95%以及热关断等。

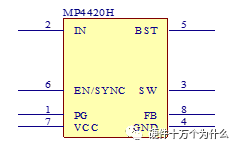

如图2所示为其引脚图。

图2 MPH4420H引脚图

PG:该引脚的输出为开漏,输出电压为高电平超过标称电压的90%

IN:电源输入端,一般接几个电容用来储能和去耦

SW: 开关输出引脚

GND: 接地端

BST: 自举引脚端,需要在SW和BST引脚之间连接一个电容以形成浮动电压来驱动MP4420H内上端的开关管。自举电容建议串联一个20欧姆电阻以降低SW尖峰电压。

EN/SYNC:使能/同步引脚端

VCC: 偏置电压,一般会加一个0.1Uf ~0.22uF的去耦电容,不要超过0.22uF

FB:反馈端

2电容选型

2.1输入电容选型:

输入电容的主要目的为储能和滤波,以防止输出需要大电流的时候,外部供电模块来不及供电,从而导致输出电压跌落的现象。在选择输入电容的时候首先要保证电容的耐压值为供电模块电压的1.5倍,

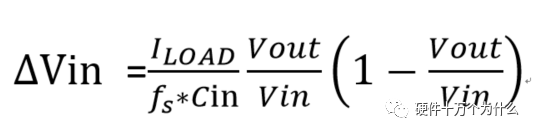

根据MP4420H的数据手册可知输入电容的计算公式1:

公式1:

为输出电流2A,fs为开关频率450KHZ,Cin为输入电容,Vout为输出电压3.3V,Vin为输入电压12V。本模块选用MP4420H数据手册中推荐的22uF的贴片陶瓷电容,可计算出为44mV。选择两个风华牌10uF/25V的C1和C2贴片陶瓷电容并联,再并联一个电容C3大小为10nF/25V的小电容以滤除输入直流电压中夹杂的高频信号。

2.2输出电容选型:

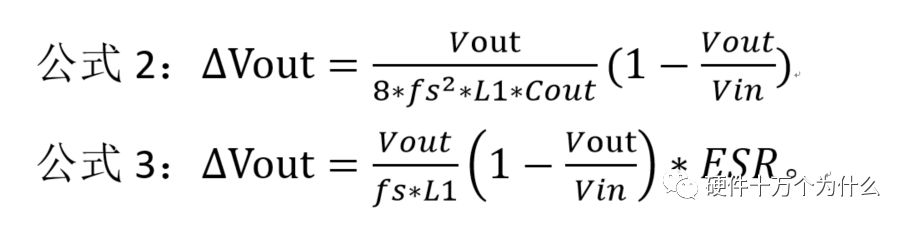

输出滤波电容值可通过计算得到,但是一般在选择电容值的时候通常会选择1.2-2倍计算出的电容值或者更大的电容量,在PCB面积允许的条件下最好多个电容并联。由于输出滤波电容和输出电感会形成两个极点,这会导致电路输出不正常,具体表现为输出纹波较大、输出上升沿有强烈的振荡等。所以在选择电容值的时候也要适当考虑电感值。由MP4420H数据手册可知输出电容和以下公式相关:

L1为输出滤波电感,ESR为输出电容的内阻。故根据输出纹波的要求可大致得到输出电容的大小,在选择电容的时候一般都会选择电容值更大点的电容。对于开关电源模块,电源自身会产生和开关频率一致的电源纹波,始终叠加在电源上输出。输出纹波也会由输出电容的内阻所引起,不断的给输出电容充放电,充电电流在输出电容的内阻ESR两端就会有压降,这个就会产生输出纹波,所以在选择输出电容的时候尽量选择ESR较小的贴片陶瓷电容而不是电解电容,选择几个电容并联也是为了降低输出内阻,一般都会在输出端并联一个较小的电容一般为nF级别的电容以滤去高频纹波。本模块选择两个100uF/16V和一个100nF/16V的贴片陶瓷电容并联。

3电感选型

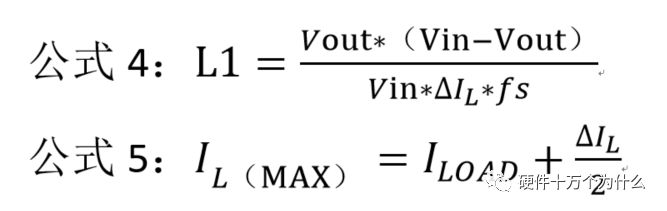

输出电感的主要作用是用来稳定输出电流以及储能,输出电感和输出电容组成的LC滤波电路主要用来平滑输出电压,使输出电压是一个稳定的直流。在选择输出电感的时候,除了要考虑电感值的大小外更要考虑电感所能抑制的电流值。对于BUCK开关变换器的输出电感的电流额定值最少是1.2倍的输出电流。根据MP4420H的数据手册可知,输出电感的电感值在1uH~10uF,电感电流额定值最少为超过负载电流的25%。对于大多数的设计,电感值可由以下公式得到:

为电感的斜坡电流,其大小一般为电感电流最大值的30%。

根据计算得到输出电感值为8uH,实际选择10uH/5A的贴片电感。

4电阻选型

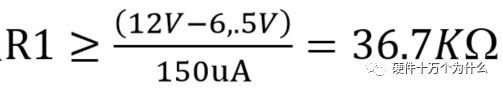

使能电阻R1的选择,EN/SYNC引脚用来控制芯片是否工作,当其为高电平时,芯片就使能工作;当其为低电平时,芯片就不工作。EN/SYNC引脚有一个6.5V的稳压管,连接一个使能电阻到输入端可以使电路使能,流入使能电阻的电流少于150uA,故本模块的使能电阻

,选择R1=100KW。

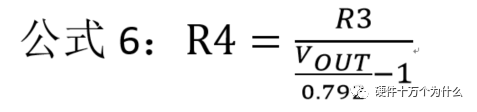

反馈部分电阻的选择,MP4420H通过外接反馈电阻形成一个闭环的电路,从而使输出稳定在3.3V。通过R3和R4的分压得到反馈电压,反馈电压和MP4420H内部的比较器做比较,当反馈电压大于内部比较器的参考电压0.8V时,MP4420H内部的开关管关断,切断输入向输出传递能量。数据手册中推荐R3的大小在40KW左右,本模块选择41.3KW。故可得到R4:

由Vout=3.3V,可得到R4=13KW

R3和R2用来设置环路带宽,R3和R2越大,带宽越小,环路带宽一般要小于开关频率fs的1/10,以使输出稳定。根据数据手册推荐的R2为51KW。

二、电源测试

1电源PDN和纹波噪声

1.1电源PDN

电源纹波噪声测试是一个比较复杂的测试难题,不同方法测量到的结果不同,即使同一种测试方法不同人测试结果一般也会存在差别。

对于终端类产品,不管是CPU、GPU、DDR等,其芯片内部都有成千上万的晶体管,芯片内不同的电路需要不同的电源供电,常见有Vcore、Vcpu、Vmem、VIO、Vgpu、Vpll等,这些电源有DC-DC电源模块供电,也有LDO电源模块供电,都统一由PMU来管理。

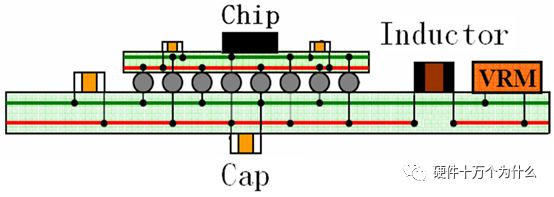

如图3所示,为芯片的PDN图,芯片的供电环路从稳压模块VRM开始,到PCB的电源网络,芯片的ball引脚,芯片封装的电源网络,最后到达die. 当芯片工作在不同负载时,VRM无法实时响应负载对电流快速变化的需求,在芯片电源电压上产生跌落,从而产生了电源噪声。对于开关电源模块的VRM,电源自身会产生和开关频率一致的电源纹波,始终叠加在电源上输出。对于电源噪声,需要在封装、PCB上使用去耦电容,设计合理的电源地平面,最终滤去电源噪声。对于电源纹波,需要增大BULK电感或者BULK电容。

图3芯片电源分布网络(PDN)示意图

对于板级PCB设计,当频率达到一定频率后,由于走线的ESL、电容的ESL的影响,已经无法滤去高频噪声,业界认为PCB只能处理100MHz以内的噪声,更高频率的噪声需要封装或者die来解决。因此对于板级电源噪声测试,使用带宽500M以上的示波器就足够了。一般情况下,示波器的带宽越大,低噪也会随之上升,因此建议测试电源时示波器的带宽限制为1GHz。

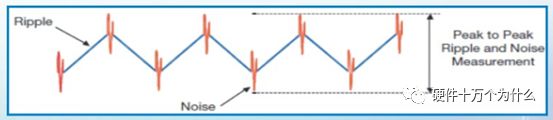

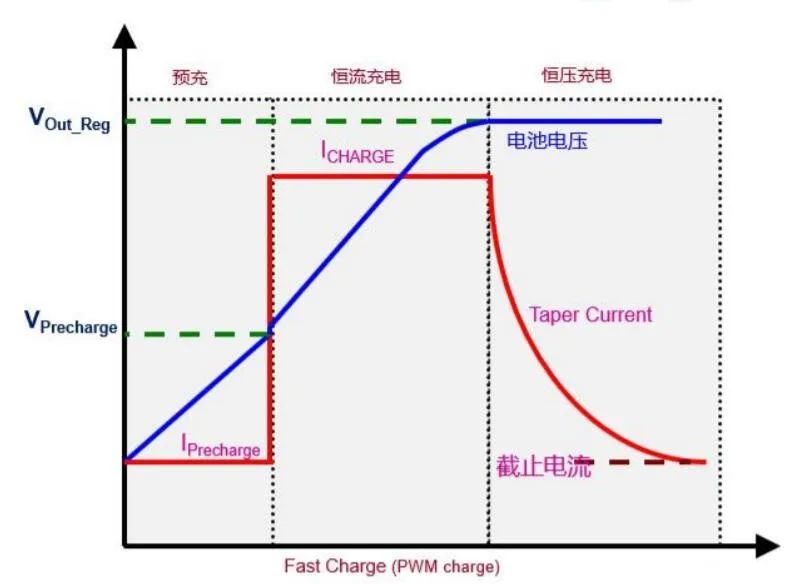

1.2电源纹波和电源噪声

电源纹波和电源噪声是一个比较容易混淆的概念,如下图4所示,蓝色波形为电源纹波,红色波形为电源噪声。电源纹波的频率为开关频率的基波和谐波,而噪声的频率成分高于纹波,是由板上芯片高速I/O的开关切换产生的瞬态电流、供电网络的寄生电感、电源平面和地平面之间的电磁辐射等诸多因素产生的。因此,在PMU侧测量电源输出为纹波,而在SINK端(耗电芯片端,如AP、EMMC、MODEM等)测量的是电源噪声。

图4电源纹波噪声图

电源纹波测量时,限制示波器带宽为20MHz,测量PMU电源输出的波形峰峰值即可电源纹波。由于PMU芯片在设计完成后,芯片厂商会做负载测试,测试PMU在不同负载时输出电源的纹波情况,因此在终端类产品板上,没必要在做这方面的测试,纹波大小参考PMU手册即可。

电源噪声测试时,测试点放在SINK端,由于SINK端工作速度大都在几十MHz以上,因此示波器带宽设置为全频段(最高为示波器带宽上限),测试点要尽量靠近测试芯片的电源引脚,如果存在多个电源引脚,应该选择距离PMU最远端的那个引脚。电源噪声跟PCB布局布线,DECAP电容的位置的位置相关,同时电源噪声影响CPU的工作状态和单板的EMI,终端类产品板需要对每块单板测试电源噪声。

2常见的纹波噪声测试方案

2.1纹波噪声测试基本要求

目前芯片的工作频率越来越高,工作电压越来越低,工作电流越来越大,噪声要求也更加苛刻,以MSM8974的CORE核为例,电压为0.9V,电流为3A,要求25MHz时,交流PDN阻抗为22mohm,电源噪声要求在±33mV以内。对于DDR3芯片,要求VREF电源噪声在±1%以内,若1.5V供电,则噪声峰峰值不大于30mV。

这类低噪声的电源测试非常具有挑战,影响其测量准确性的主要有如下几点:

(1)示波器通道的底噪;

(2)示波器的分辨率(示波器的ADC位数);

(3)示波器垂直刻度最小值(量化误差);

(4)探头带宽;

(5)探头GND和信号两个测试点的距离;

(6)示波器通道的设置;

在测试电源噪声时,要求如下条件:

(1)需要在重负载情况下测试电源纹波;

(2)测试电源纹波时应该将CPU、GPU、DDR频率锁定在最高频;

(3)测试点应该在SINK端距离PMU最远的位置;

(4)测试点应该靠近芯片的BALL;

(5)带宽设置为全频段;

(6)示波器带宽大于500MHz;

(7)噪声波形占整个屏幕的2/3以上或者垂直刻度已经为最小值;

(8)探头地和信号之间的回路最短,电感最小;

(9)测试时间大于1min,采样时间1ms以上,采样率500Ms/s以上;

(10)纹波噪声看Pk-Pk值,关注Max、Min值;

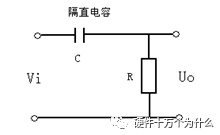

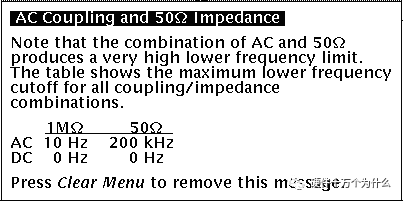

示波器有AC和DC两种耦合方式,当采用AC耦合时,其内部等效电路如图5所示,C为隔值电容,R为终端对地阻抗,Vi为输入信号,Vo为测量信号,滤波器的截止频率为 若为信号频率,则有:

若为信号频率,则有:

当

,用分贝表示为:

,用分贝表示为: ,则表示信号经过滤波器可以无衰减传递;

,则表示信号经过滤波器可以无衰减传递;

当 时,

时, ,用分贝表示为:

,用分贝表示为: ,则表示该频段的信号经过滤波器后,按照-20dB/十倍频的斜率衰减;

,则表示该频段的信号经过滤波器后,按照-20dB/十倍频的斜率衰减;

当

则表示信号衰减约0.707倍。

则表示信号衰减约0.707倍。

当 时,Vo=0.99Vi,测试误差为1%。

时,Vo=0.99Vi,测试误差为1%。

图5 加隔值电容后高通滤波器等效电路

表1不同隔值电容对应的频点

| 隔直电容容值(uF) | 50W截止频率(KHz) | 50W-1%误差频点(KHz) | 50W截止频率(Hz) | 1MW-1%误差频点(Hz) |

| 0.1 | 31.83 | 222.82 | 1.5915 | 11.14 |

| 0.47 | 6.77 | 47.41 | 0.3386 | 2.37 |

| 1 | 3.18 | 22.28 | 0.1592 | 1.11 |

| 2.2 | 1.45 | 10.13 | 0.0723 | 0.51 |

| 10 | 0.32 | 2.23 | 0.0159 | 0.11 |

2.3无源探头DC耦合测试

使用无源探头DC耦合测试,示波器内部设置为DC耦合,耦合阻抗为1Mohm,此时无源探头的地线接主板地,信号线接待测电源信号。这种测量方法可以测到除DC以外的电源噪声纹波。

如图6所示,当采用普通的鳄鱼夹探头时,由于地和待测信号之间的环路太大,而探头探测点靠近高速运行的IC芯片,近场辐射较大,会有很多EMI噪声辐射到探头回路中,使测试的数据不准确。为了改善这种情况,推荐用无源探头测试纹波时,使用右图中的探头,将地信号缠绕在信号引脚上,相当于在地和信号之间存在一个环路电感,对高频信号相当于高阻,有效抑制由于辐射产生的高频噪声。更多时候,建议测试者采用第三种测试方法,将一个漆包线绕在探头上,然后将漆包线的焊接到主板地网络上,移动探头去测试每一路电源纹波噪声。同时无源探头要求尽量采用1:1的探头,杜绝使用1:10的探头。

图6无源探头地线两种处理方法

对于示波器,若垂直刻度为xV/div,示波器垂直方向为10div,满量程为10xV,示波器采样AD为8位,则量化误差为10x/256 V。例如一个1V电源,噪声纹波为50mV,如果要显示这个信号,需要设置垂直刻度为200mV/div,此时量化误差为7.8mV,如果把直流1V通过offset去掉,只显示纹波噪声信号,垂直刻度设置为10mV即可,此时的量化误差为0.4mV。

使用无源探头DC耦合测试,示波器设置如下:

(1)1Mohm端接匹配;

(2)DC耦合;

(3)全带宽;

(4)offset设置为电源电压;

2.4无源探头AC耦合测试

使用无源探头DC耦合需要设置offset,对于电源电压不稳定的情况,offset设置不合理,会导致屏幕上显示的信号超出量程,此时选择AC耦合,使用内置的搁置电路来滤去直流分量。对于大多数的示波器,会有如下参数,设置为AC耦合,此时测量的为10Hz以上的噪声纹波。

图7示波器两种耦合方式频点

使用无源探头AC耦合测试,设置如下:

(1)1Mohm端接匹配;

(2)AC耦合;

(3)全带宽;

(4)offset设置为0

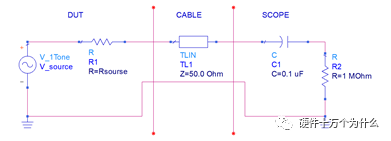

2.5同轴线外部隔直电容DC50欧耦合测试

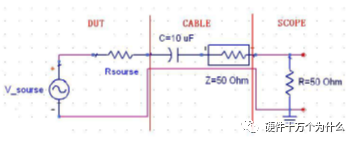

由于无源探头的带宽较低,而电源开关噪声一般都在百MHz以上,同时电源内阻一般在几百毫欧以内,选择高阻1Mohm的无源探头对于高频会产生反射现象,因此可以选择用同轴线来代替无源探头,此时示波器端接阻抗设置为50欧,与同轴线阻抗相匹配,根据传输线理论,电源噪声没有反射,此时认为测量结果最准确。

利用同轴线的测量方法,最准确的是采用DC50欧,但是大部分示波器在DC50欧时offset最大电压为1V,无法满足大部分电源的测量要求,而示波器内部端接阻抗为50欧时,不支持AC耦合,因此需要外置一个AC电容,如图8所示,当串联电容值为10uF时,根据表1可以看到,此时可以准确测试到2KHz以上的纹波噪声信号。

图8 同轴线DC50测量图

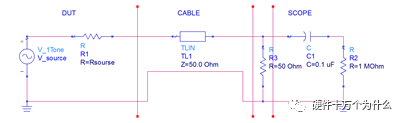

2.6同轴线AC1M欧耦合测试

由于从PMU出来的电源纹波噪声大多集中在1MHz以内,如果采用同轴线DC50外置隔直电容测量方法,低频噪声分量损失较为严重,因此改用图9所示的测量方法,利用同轴线传输信号,示波器设置为AC1M,这样虽然存在反射,但是反射信号经过较长CABLE线折返传输后,影响是有限的,示波器在R2上采集电压值可以认为仍然可以被参考。

图9同轴线AC1M测量图

为了避免反射,在同轴线接到示波器的接口处端接一个50ohm电阻,使示波器输入阻抗和cable线特征阻抗匹配。

图10同轴线AC1M测量改进图

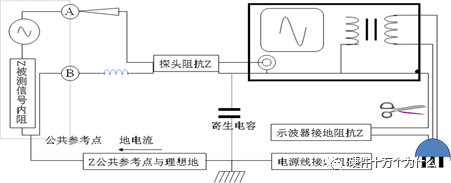

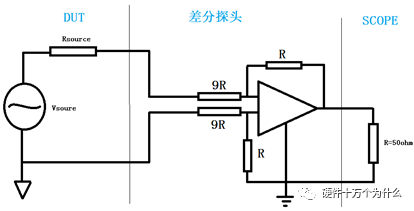

2.7差分探头外置电容DC耦合测试

由于示波器的探头地和机壳地通过一个小电容接在一起,而示波器的机壳地又通过三角插头和大地接在一起,在实验室里,几乎所有的设备地都和大地接在一起,示波器内部地线接法如图11所示,因此上面介绍的两种方法都无法解决地干扰问题,为了解决这个问题,需要引入浮地示波器或者差分探头。

图11示波器内部地线接法

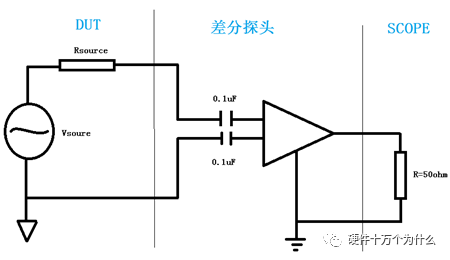

如图12所示,为差分接法,由于差分探头为有源探头,外置差动放大器,可以将待测信号通过差分方式接入,使示波器的地和待测件地隔离开,达到浮地效果。但是差分探头在示波器内部只能DC50欧耦合,而offset最大一般不超过1V,因此需要在差分探头上串联隔直电容。使用差分探头测量时关键是探头的CMRR要足够大,这样才能有效抑制共模噪声。

图12 差分探头外置电容DC耦合接法示意图

3.8差分探头衰减DC耦合测试

当采用差分探头外置电容DC耦合时,同样存在截止频率的问题,测量的结果会损失一些低频分量,为了解决这个问题,可以将差分探头衰减10倍,示波器会将采集到的电压值乘10显示出来,这个时候offset设置也会放大到10V,能够满足终端类产品的直流电压偏置。

图13差分探头衰减DC耦合测试接法示意图

3输入电压测试

本次测试使用的设备有:0~30V/0~2A可调数字电源、鼎阳牌SDS1000X-C数字示波器以及万用表。

如图14所示为可调的数字电源,图15为SDS1000X-C数字示波器,图16为MP4420H的电源模块。

图14 可调电源

图15 SDS1000X-C数字示波器

图16MP4420H电源模块

如图17所示为12V输入电压的测试波形,从示波器上可以看出,输出电压为12V直流电压。

图17 输入电压测试图

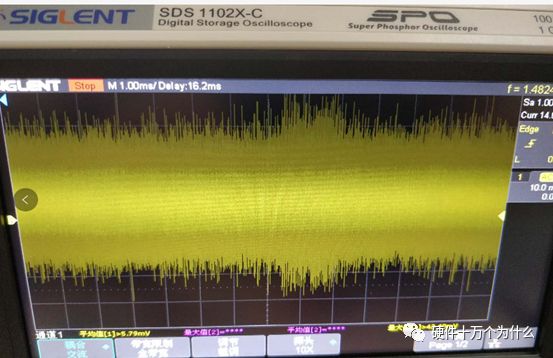

图18为输入电压的纹波测试图,是通过把示波器的耦合方式选择交流耦合测试出来的。从示波器上可以读出,输入电压纹波的峰峰值为40mV。

图18 输入纹波测试图

4输出电压测试

图19所示为输出电压的测试图,从示波器上可以看出,输出电压最大值是3.44V,输出电压上升沿平缓,没有振铃和电压过冲等现象。

图19 输出电压测试图

如图20所示为输出电压的纹波,从示波器中可以看出,纹波电压最大值为42mV。图21所示为把纹波时间轴缩小的测试图,从示波器中可以看出,纹波的峰峰值为3.96mV。

图20 输出电压纹波测试图

-

BUCK

+关注

关注

32文章

482浏览量

64123 -

电源电路

+关注

关注

48文章

995浏览量

65187 -

陶瓷电容

+关注

关注

3文章

435浏览量

23912

原文标题:一个BUCK电源电路设计测试过程

文章出处:【微信号:Hardware_10W,微信公众号:硬件十万个为什么】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求一份基于TL494的BUCK型电路设计详细资料

【技术探讨】BUCK电路设计技术要点

BUCK电路的降压过程是怎样的

TDR测试过程静电危害及其预防

解决测试过程中多路供电的难题

BUCK降压拓扑和锂电池充电电路设计

防静电ESD测试过程展示

buck芯片性能测试过程

BUCK电源电路设计测试过程分享

BUCK电源电路设计测试过程分享

评论