0 引言

AIS系统是一种船舶交通信息交换系统,船载AIS设备不断发送自身信息,如航向、吨位等,用以领航调度、避免碰撞。随着海运贸易的高速增长,迫切需要建立对大片海域船舶动态的实时监控系统,卫星平台因覆盖范围广而受到重视。加拿大等国家相继发射载有AIS信号接收设备的卫星[1]。AIS系统采用高斯滤波最小频移键控(Gaussian Filtered Minimum Shift Keying,GMSK)调制,可以通过相干方式或非相干方式解调。相干解调具有较好的抗噪声性能[2],但是需要准确恢复载波频率,而载有AIS设备的近地卫星轨道高度一般在500 km左右,多普勒频移可达±4 kHz,因此精确的载波恢复比较困难;非相干解调主要采用鉴频器,从接收GMSK信号中提取频率的变化信息,因此对频偏不敏感且结构简单,在很多GMSK移动通信系统中得到了应用[3-4],如GSM。目前,AIS接收机射频端多采用一级或二级下变频方案[5-6],这种方案使射频前端硬件比较复杂,硬件成本高。鉴于AIS信号是窄带信号,因此本文设计中对接收到的射频信号直接带通采样,以简化接收机硬件结构。

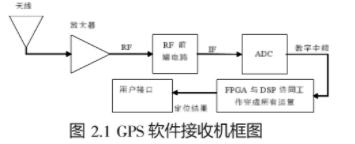

本文主要工作如下:在Xilinx xc4vlx80 FPGA上设计了基于带通采样的AIS非相干解调软件接收机,设计文件通过综合映射后下载到FPGA中,以实际AIS信号源作为测试信号,通过嵌入式逻辑分析工具Chipscope在PC上观察FPGA内部信号来验证设计,并给出了硬件资源消耗。

1 GMSK信号调制和非相干解调原理

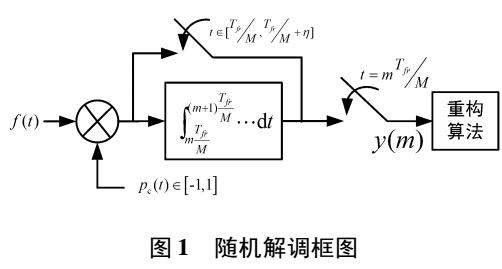

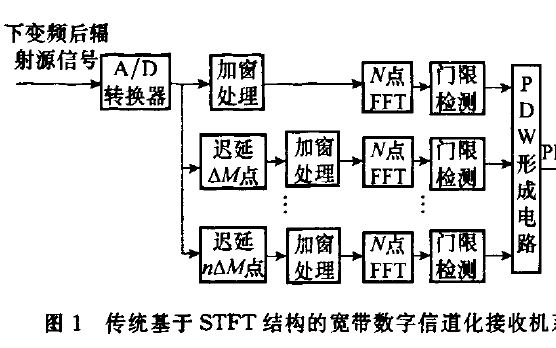

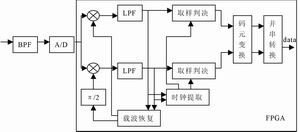

AIS信号是GMSK调制信号,其调制和非相干解调过程如图1所示。

发射端比特脉冲为:

比特流d(t)通过带宽时间积(Bandwidth-Time product,BT)为BbTb的高斯滤波器进行脉冲成型。Bb为高斯滤波器的3 dB带宽,Tb为比特速率。高斯成型滤波器的冲激响应为:

式中*表示卷积运算。最后通过电压/频率(V/F)转换,形成调频信号并调制到规定频段发射出去。

对于非相干解调的接收机,首先将接收信号进行正交下变频,滤除高频分量和带外噪声后得到基带正交信号I(t)、Q(t),再通过下式进行频率/电压(F/V)转换:

2 AIS接收机的FPGA设计

带通采样AIS非相干接收机系统结构如图2所示。

2.1 带通采样率

AIS信号有A、B两个发射频点,分别为161.975 MHz和162.025 MHz,数据速率Rb为9.6 kb/s,带宽不超过25 kHz,接收机射频前端的带通滤波器(Band Pass Filter,BPF)中心频率为162 MHz,带宽为250 kHz,因此可对BPF输出射频信号直接采样。理论上ADC的带通采样频率fS1只要满足下式即可:

式中,B为BPF的带宽,fH为采样信号的最高频率成分,[]表示取不超过该数的最大整数。采样频率越小,对FPGA的处理速度要求就越低。但实际系统中由于BPF过渡带的缓变特性,一些边带噪声不能被完全抑制,当采样频率过小时,采样得到的信号频谱周期重叠次数过多,导致更多的噪声叠加到有用信号上。因此,本系统采用的采样时钟频率为fS1=24 MHz。带通采样后AIS信号中心频率fC1可通过下式计算:

2.2 两级数字下变频结构

系统中FPGA和ADC共用时钟源,FPGA系统主频为fSYS=24 MHz。天线接收的AIS信号经过低噪放和带通滤波,再经过14 bit ADC采样后,输入FPGA。输入FPGA的AIS信号中心频率fC1=6 MHz、采样率fS1=24 MHz、带宽为250 kHz。由于信号带宽远小于采样频率,可以进行下变频和降采样处理,以减轻后级处理压力。首先将采样信号与FPGA内数控振荡(NCO)IP核产生的位宽为10 bit、频率fO1=6 MHz的正弦信号进行混频,再通过数据位宽为16 bit、截止频率为100 kHz的51阶低通滤波器,滤除高频成分;再对低通信号进行48倍降采样,得到的数据速率为500 kHz、中心频率为±25 kHz(A、B两个发射频点)的AIS信号;再将该信号与NCO产生的位宽为10 bit、频率fO2=25 kHz的正弦信号进行混频,再通过数据位宽为16 bit、截止频率为25 kHz的51阶低通滤波器来滤除高频分量,得到包含多普勒频偏(小于4 kHz)的基带正交信号。

采用这种两级下变频的好处,除了可以降低采样速率,减轻FPGA处理压力外,还可以减少逻辑资源消耗。如果对采样率为fS1=24 MHz的信号直接进行正交数字下变频,由于混频后的FIR低通滤波器驱动时钟频率(即系统主频fSYS=24 MHz)和输入滤波器的混频信号数据速率(即采样率为fS1=24 MHz)相同,那么FIR滤波器IP核经过综合后,需要26个乘法器。而正交下变频需要两个低通滤波器,因此共需要26×2=52个乘法器;采用两级下变频方案时,一级混频后的滤波器同样需要26个乘法器,降采样后,输入滤波器的混频信号数据速率降为fS2=500 kHz,而驱动时钟不变,仍为fSYS=24 MHz,因此在输入一个数据的周期内,最多可以复用该乘法器fSYS/fS2=48次,大于51阶FIR滤波器所需要的26个乘法器,所以正交下变频后的滤波器经综合,仅需1个乘法器即可,如图3所示。两级下变频中需要3个低通滤波器(如图2所示),然而需要的乘法器个数仅为26+1×2=28个。

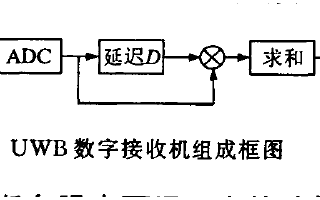

2.3数字鉴频以及后检测滤波

对正交下变频得到的基带正交信号进行式(6)所示的数字鉴频操作,提取频率信号。数字鉴频器的硬件主要由延时模块、乘法器、除法器、加法器和减法器构成。由于理论上数字鉴频是非线性操作,对噪声十分敏感,输出中会包含高频的噪声分量,因此有必要对鉴频器输出进行后检测低通滤波。图4是在MATLAB中,仿真采用不同截止频率的低通滤波器时AIS解调的误码率曲线,横坐标为信号功率和噪声功率比值。由图中可以看出,低通滤波器的截止频率Bo为0.4Rb(Rb为AIS比特速率)时,误码性能最好。因此,FPGA中后检测滤波的带宽设为0.4Rb=0.4×9.6 kb/s=3.84 kHz。

3 AIS信号解调实际测试

在Xilinx开发环境ISE13.2中设计AIS接收机各模块,将设计好的模块进行综合、映射、布局布线,生成下载文件。并调用Chipscope嵌入式逻辑分析仪IP核,通过JTAG仿真器来连接FPGA和PC,以便实时观察FPGA内部信号。利用实际AIS信号源作为测试信号,用同轴线将AIS信号源输出连接到模数转换器AD9246输入,带通采样信号读入FPGA进行解调。观察到各级信号如图5所示。在图5(d)中可以看到A、B两个不同频点AIS信号的24比特位同步序列00110011…0011以及帧起始标志01111110。设计所占用的Slice数为231,仅占总资源数的1%。

4 结束语

本文根据GMSK信号的非相干解调原理,在Xilinx FPGA上设计了带通采样的AIS非相干接收机,利用AIS窄带信号的特点,采用两级下变频方案,将数据速率降至合理范围,减轻FPGA处理压力,同时也大大减少了低通滤波器对硬件逻辑资源的消耗;在MATLAB中进行了AIS解调的理论仿真,设置了一个最优的数字鉴频后检测滤波器截止频率,以抑制实际环境中的噪声干扰;最后在硬件系统上对设计的接收机进行了测试,并观察到解调出的A、B两个频点的基带信号。该设计消耗的逻辑资源不到器件总资源数的1%,可以为AIS接收机小型化、批量化生产提供参考。

-

FPGA

+关注

关注

1629文章

21729浏览量

602953 -

AIS

+关注

关注

0文章

22浏览量

13147

发布评论请先 登录

相关推荐

如何实现基于多相滤波的数字接收机的FPGA?

中频采样多模式数字接收机的设计与实现

UWB定位系统中标签接收机的FPGA实现

DS/FH混合扩频接收机解扩及同步技术的FPGA实现

宽带数字信道化接收机的FPGA实现

高性能、双通道IF采样接收机

压缩采样接收机抗ADC非线性影响

基于带通采样的AIS非相干解调软件接收机的FPGA实现设计

基于FPGA-DSP平台实现GPS卫星导航接收机的设计

如何使用FPGA实现ADC的TR UWB数字接收机性能

如何使用FPGA实现高效的宽带数字接收机

关于带通采样星载AIS非相干接收机的FPGA实现

关于带通采样星载AIS非相干接收机的FPGA实现

评论