本文将探讨如何提高系统级设计(System-level design)的工作效率。

当下,许多模拟、射频和混合信号设计都需要在不同的衬底技术中集成多个IC以实现所需的性能目标。

鉴于当今芯片、封装和电路板的复杂性,不仅硅,包括其他非硅材料都需要被用在设计中以达到最优的系统性能。异构器件的集成使得设计人员能够实现用单片IC(SoC)设计方法无法轻易复制的设计结果。然而,异构集成也为设计人员带来了全新的挑战。

今天,在“系统级”(IC-封装-PCB)进行设计,会涉及到大量关于下游封装/PCB对芯片性能和可靠性影响的经验猜测。 传统上,vwin /射频IC设计人员只需仿真IC而无需考虑封装和PCB的影响。 然而通常来讲,封装包含一个或多个IC和互连元件,有时也可能包含IC工作所需的分立元件;同样地,PCB也包含多个封装、互连和分立元件。 因而,将整个系统统一起来进行仿真,对捕捉高频性能是非常重要的。由于IC设计和封装设计人员使用不同的原理图输入工具,IC设计人员不得不重新捕获封装系统原理图并放置于IC原理图的测试平台上,才能够对联合系统进行仿真。

为了在早期设计阶段和流片之前识别并消除潜在误差,建立一个紧密的设计和仿真环境从而帮助IC设计人员在整个PCB、封装系统和寄生效应的情景下实现IC的自动仿真是十分必要的 。我们已有一个相似的设计环境可以对数字IC的I/O与I/O互连进行仿真,现在,Virtuoso System Design Platform又使在包含寄生参数的完整PCB/封装电路中对模拟/射频IC进行仿真成为了可能,最大限度地减少了设计迭代次数。

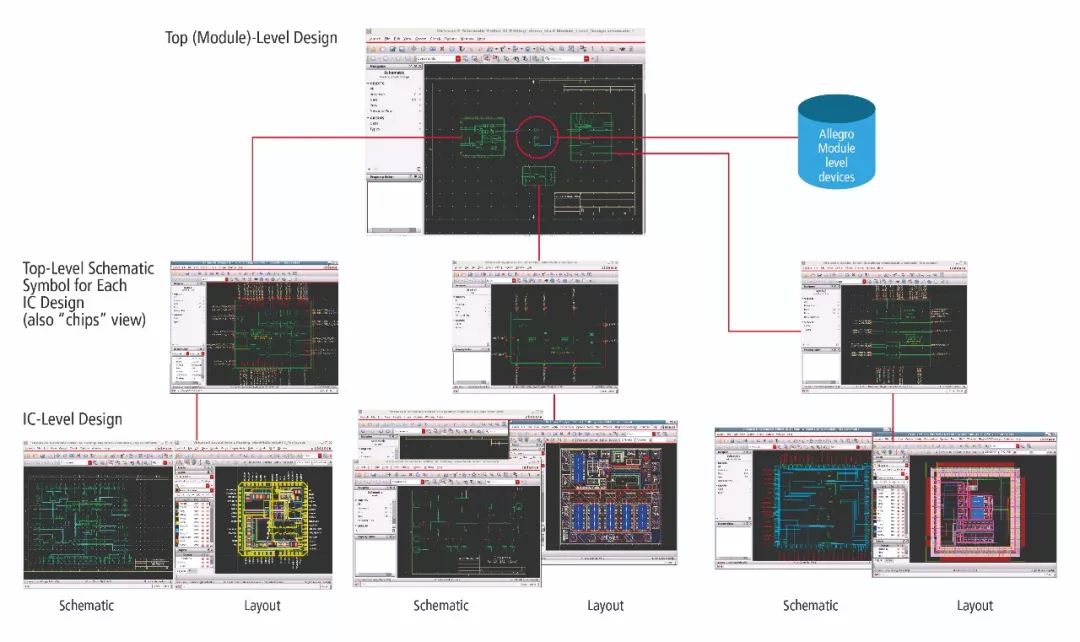

图1:Virtuoso系统设计平台

此流程提供了通过单个原理图编辑器,驱动IC和封装layout的能力。 通过使用同一原理图编辑器(Virtuoso Schematic Editor),IC设计人员可以在一个通用的环境中更好地进行系统级设计,包括预布线系统仿真(IC和封装一起),继而驱动各自领域的布线。该流程还通过生成Cadence SiP Layout中使用的芯片引脚使大部分封装级库的开发流程自动化。

芯片与封装之间的协同设计

高阶用户可以在芯片与封装之间协同设计,以实现更好的封装级布线和/或引线键合。该流程可以让设计人员在封装布局布线之前将封装的原理图放入Virtuoso Schematic Editor中进行设计。 进一步则可以从Virtuoso Layout套件中导出芯片引脚和符号,并利用它们进行封装原理图构建。 数据的双向流动可将原理图中所做的编辑动态地传递到SiP Layout,反之亦然。 设计人员还可以生成物料清单,以直观的方式可视化设计差异,并使用此流程查看layout报告。

图2:RS Pro Evikey

一旦封装或PCB被该流程设计完毕,基于分析的该流程将会被带入完整的仿真环境中,不需要对PCB或封装以及电磁仿真领域有专业认知也可以轻松完成。 这种方法将会显著提高生产力。此分析流程允许IC设计人员将PCB和封装layout及其相应的寄生模型(以S参数或SPICE表示)导入IC设计环境,进而对PCB或封装连接进行读取,并创建一个包含寄生模型的原理图。该原理图可以随时在PCB或封装系统的环境中进行仿真。

该设计平台有助于在包含封装/PCB互联和外部元件的条件下对IC进行集成和仿真。 由于IC、封装和PCB通常由不同的团队在不同地理位置使用不同的设计工具进行设计,并且在设计周期的不同阶段都各自独立,因此该设计平台尤为重要。该平台将封装和PCB级layout寄生效应共同纳入通用原理图中,实现了整个系统的跨区域仿真。这有助于在流片前确定关键的性能偏差。

然后,所需修改信息可以直接被传递给封装/ PCB团队。 这里有一个重要功能,即是可以智能地将寄生模型融合到仿真原理图中。如果模型中还包含分立器件,那么它们则会在创建仿真电路图时被自动滤除掉,从而不会在仿真中被重复计算。 自动滤除需要重新调整接口,以确保正确融合并去除所有SMD以避免冗余。

拥有这样一个强大的集成平台可以为设计人员带来以下三大优势:

通过使用通用的原理图编辑器,设计人员现在可以为封装的layout设计原理图。Virtuoso Schematic Editor是可以驱动IC和封装设计的统一的原理图编辑器。

设计人员可以创建封装或PCB带寄生效应的原理图,并利用Virtuoso Analog Design Environment进行仿真,其中包含的多重技术仿真是实现完整的系统仿真的重要机制。

设计人员可以同时通过协同设计芯片简要流程来设计IC和封装layout,最大限度地减少设计迭代次数并减少后期的布局规划和设计可行性问题。

简而言之,Virtuoso System Design Platform是一个全面的、基于系统的解决方案,实现由单一原理图驱动的IC和封装的仿真以及LVS检查。

该设计平台在2017年荣获Electronic Products网站评选的年度电子产品大奖。

-

芯片

+关注

关注

455文章

50711浏览量

423104 -

pcb

+关注

关注

4318文章

23079浏览量

397436 -

编辑器

+关注

关注

1文章

805浏览量

31162

原文标题:专家博客 | 如何提高系统级设计(System-level design)的工作效率

文章出处:【微信号:CadencePCB,微信公众号:CadencePCB和封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何将开关电源工作效率提高

浅谈提高氧化铝厂破碎系统的工作效率

如何提高微电机的工作效率低

方法介绍:微电机工作效率低?这样改进,提高效率

方法 | 微电机工作效率低?这样改进,提高效率

气密性测试仪如何提高工作效率

工业级路由器如何提高你的生产力和工作效率?

如何提高系统级设计的工作效率

如何提高系统级设计的工作效率

评论