本文研究AMD推出的服务器系统芯片 (SoC): AMD Epyc。许多客户会购买双插槽 (2S) 服务器,因为可以获得比英特尔单插槽 (1S) 服务器体系结构更多的可用 i/o 或内存容量。AMD Epyc 的1S 处理器和 i/o 资源有可能取代2S 服务器设计的许多工作负载。

图 1: AMD Epyc SoC-插座 (左), 底部视图 (右)

历史

多处理器服务器已经存在数十年了。在二十世纪八十年代, 它们是由每个处理器 (CPU) 的许多主板构建的, 之后是许多 "单板计算机"。单片微处理器使服务器设计人员能够将几个处理器插座放到一个主板上。这些 多插座主板被标记为 "n 处理器" (nP), 其中 "n" 是主板上的处理器数, 如1P、2P、4P 等。

今天, 一个服务器插座可以承载许多硬件线程。多插槽主板现在被标记为 "n 插座" (nS), 因此1S 服务器有一个包含多个处理器内核的处理器插座等。

图 2: 一个AMD Epyc SoC是2008年时四插槽系统的两倍线程

资料来源: TIRIAS 研究

在十年前AMD 推出AMD Opteron双核处理器时, 多核处理器进入主流服务器市场。多线程处理器内核在每个内核中都有额外的 CPU 资源, 可以一次运行多个软件执行线程, 在过去十年中也变得很流行。多线程、多核处理器引起从主板计数处理器到计数Socket的行业转变。计数Socket消除了处理器芯片可以处理的硬件线程数和主板上插槽中的物理芯片数量之间的混淆。

同期, 基于服务器的并行编程实践已停滞不前,大多数应用程序有8个以下的软件执行线程,很少有超过16个线程的。对于大多数主流商业应用来说都是如此。虚拟化的兴起是由于硬件性能的飞速发展, 而不是单个软件应用程序能够吸收硬件性能的增加。在 21世纪, 多核处理器的泛滥使得4S 系统能够取代更昂贵的8插槽 (8S) 市场, 因为4S 系统变得更强劲。然后, 在过去的十年中, 2S 系统从更昂贵的4S 系统中接管了许多工作负载。2S 系统现在被定义为企业级服务器的主流。

继续向每个服务器处理器中注入更多内核和线程的副产品是, 一个 AMD Epyc SoC CPU现在包含大约2008年时的双线程、四核、4S 服务器的线程执行资源的两倍 (见图 2)。这就引出了一个问题: 为什么2S 系统仍然是主流的服务器主板外形?是否有可能将主流服务器工作负载移动到1S 基础架构?1S 服务器可以是 "企业级" 吗?

2S还是1S?这就是问题所在

每个可调度任务或进程生成超过16个并发线程的工作负载很少,大多数情况下每个实例生成的线程不超过8个。在每个进程中生成超过16个线程的大多数工作负载都是 "令人尴尬的并行" 高性能计算 (HPC) 工作负载, 每个实例生成数量级更多的线程,它们更适合GPU或其他卸载加速,而不是扩展到更多的CPU。

大多数工作负载(例如在虚拟机中运行的业务逻辑和运行在容器中的云微服务)可以在1S服务器上以2S服务器上的速度和价格运行,如果现有的1S系统可用于2S服务器就只插一个插槽。

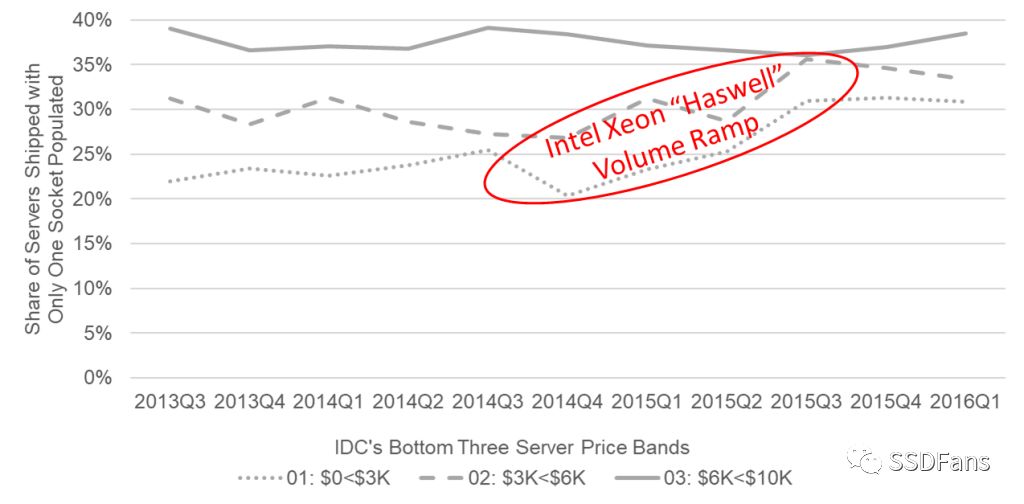

英特尔的服务器CPU功能和定价细分策略似乎旨在保持其可观的2S容量和利润率。由于核心数量的增加以及底层核心和缓存体系结构的改进, 2014年底英特尔至强“Haswell”的推出增加了只用一个插槽的2S服务器的数量。

图3显示, 在 Haswell CPU销量快速增长期间, 仅有一个插座填充的 3000美元以下 2S 服务器的数量增加了约 20% (从25% 到30% )。此外, 只有一个插座的3000美元 至6000美元 2S 服务器的出货量也跃升约 25%, (从27% 到35%)。

图 3: 仅装入一个套接字的2S 服务器共享

AMD的 Epyc 体系结构具有相同的核心数量和结构提升, 因此在市场上有机会产生同样的效果, 但值得注意的是AMD也有兴趣推广1S 市场。

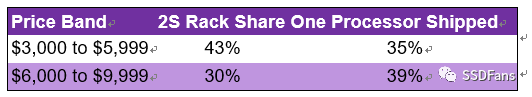

今天, 超过1/3 的2S 功能机架优化服务器只配备了一个处理器。有关两个最畅销2S 服务器价格区间的只配一个CPU的市场份额, 请参阅表1。

表 1: 2019年Q3:2S 机架优化服务器在Q1期间只配备了一个处理器

Source: IDC, 2016

特点

今天购买许多2S 服务器只是为了比英特尔1S服务器架构上更多可用的和不同的I / O容量或内存。要增加大量内存和 PCIe 通道, 需要添加第二个处理器。这些设计将2S 芯片组用于提供更多或不同的 I/O (主要是 PCIe、NVMe 和SATA), 而不是用于第二套插座的计算资源。

大多数企业和大规模服务器购买者不会为了省钱,从英特尔的带有缓存RDIMM等企业级功能的至强 E5 CPU换到只有无缓冲DIMM(UDIMM)等消费级PC功能的1U服务器中使用的Xeon E3 CPU。考虑到以后要升级到两个E5,所以购买至强 E3 与至强 E5 的价格差异, 让人觉得可以接受,可是实际上,财务成本实际上非常高, 因为几乎没有人购买一个只有一个至强 E5 的2S 服务器之后安装第二个处理器。

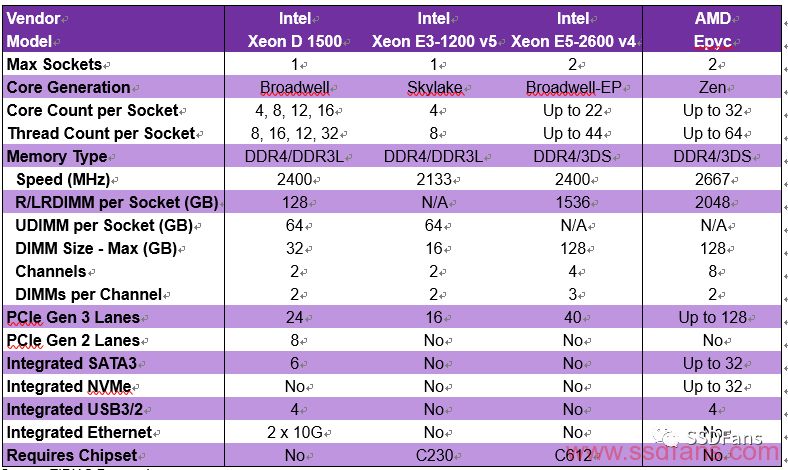

表2: Epyc 的竞争优势

Source: TIRIAS Research

表2显示了 AMD Epyc 和竞争性英特尔至强产品的比较。表3中的所有信息都适用于1S 配置, 尽管 Epyc 和至强 E5 都支持双插槽。该表清楚地表明,AMD Epyc不仅超越了Xeon E3的限制,而且还超越了至强E5 v4的集成和功能。

对于两个处理器插座都主要用于增加内存容量和PCIe通道的情况, 这不仅增加了主板面积、机箱体积和第二个处理器的额外支出, 而且还由于第二个处理器的额外功耗, 持续运营成本增加。

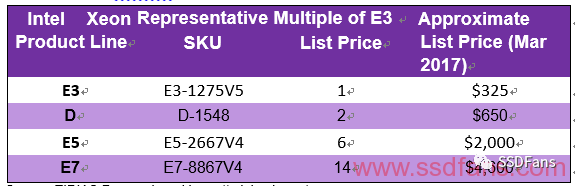

表3显示,英特尔定价Xeon D 1S SoC的价格是可比Xeon E3处理器的两倍,但Xeon E3需要额外的南桥芯片,网络和I / O支持。相比之下,英特尔正在为Xeon E5处理器定价,这也需要额外的南桥芯片,网络和I / O支持,价格是同类E3 SKU的六倍 - 对于只有一个插座的2S板,E5是可升级性所需(如上所述,很少发生,但仍在购买决策中考虑)。随着2S板的两个插座的填充,英特尔双E5处理器的定价是单个E3处理器价格的12倍。

表 3: 英特尔至系列价格比较

Source: TIRIAS Research and https://ark.intel.com/

提升

有两种方法可以查看升级:

升级两个插槽中的处理器以提高速度和其他体系结构改进。当每新一代处理器通过时钟速率提高和体系结构改进提高了性能时, 这种技术就能良好运行。不幸的是, 英特尔目前的 x86 处理器核心体系结构正在成熟, 而且由于流程缩短,摩尔定律不再自动生成更快的时钟速度。因此, 一代又一代的性能改进通常在一位数内。今天的服务器通常是在它们发生故障之前保持服务状态, 直到它们不受支持, 或者直到它们无法运行特定的工作负载。

首先使用一个处理器, 然后添加一个处理器以添加更多功能。有趣的是, 从与 许多云和企业 IT 商店交谈, 大多数服务器不会打开其机箱盖以升级服务器的任何部分。对于仅用一个处理器的2S 服务器也是如此。虽然从应用软件的角度来看,二十年前添加第二个处理器是一个合理的选择,但现代应用程序倾向于通过添加更便宜的服务器来很好地扩展,而不是购买昂贵的扩展服务器,这些服务器是虚拟化的许多应用程序的过度构建 机器托管部署。 如今,横向扩展以增加容量要容易得多。 如果运营商打算投入人力来打开服务器机架并拔出机箱 - 他们也可以更换整个机箱,而不是试图安装额外的CPU,散热器和更多内存。

AMD 的新服务器体系结构和设计

AMD 的 Epyc SoC 旨在解决潜在的1S 服务器需求,虽然英特尔已经推进到昂贵而且没必要的2U 服务器, 以及高性能2U 服务器的需求。

Epyc SoC 可以直接连接多达32个 SATA 或 NVMe 设备。在设计主板时, 将 Epyc 的 PCIe Gen3 通道配置为 NVMe、SATA 或2S 插座互连。在2S 配置中, Epyc 的系统内存容量加倍到 2/4TB的内存 (RDIMM/LRDIMM), 但系统 I/O 与1S 解决方案相同,一半的 I/O 通道用于两个 SoC 插座之间的高速链接。

图 4: AMD Epyc 1S 开发板 (左) 和2S 预生产板 (右)

Source: TIRIAS Research

经济

服务器成本有两个经济组成部分: 资本支出CAPEX和 OPEX。资本支出是一个完整服务器的买方价格, 而 OPEX 主要是服务器的功耗和管理开销成本。

在1S 和2S 的经济学之间推广比较是有点模糊的。表4列出了主要比较的特征。

表 4: 资本和 OPEX 对1S 和2S 服务器成本差异的贡献

Source: TIRIAS Research

还有一个OPEX软件许可组件,但是很难在各种应用程序中进行概括。

我们估计典型的1S和2S主板之间的定价增加了200到300美元(由于额外的元件,增加的电路板成本等) - 接近Xeon E3和Xeon E5之间单处理器价格的差异。对于更大和更复杂的电路板设计,以及第二个处理器或SoC插座所需的支持组件(电源调节器,插座等),这种价格差异是正常的。

此外, 即使从不填充第二处理器插座,也会用容量更高、价格更贵的电源, 在2S设计中用于为附加处理器和支持组件供电。

虽然额外的2S主板组件导致功耗增加,但同样,处理器功耗相比其他主板组件相形见绌。英特尔的1S Xeon E3系列功耗规格范围为25W至80W,Xeon D功耗规格范围为45W至60W。英特尔的2S Xeon E5系列功耗范围从50W到145W。相比之下,DIMM插槽的功耗为7.5W,因此四个DIMM可能消耗高达30W的功率,而八个DIMM可能消耗高达60W的功率。

然而, 主板的价格差异约为600美元, 从英特尔1S 至强 E3 系列处理器移动到2S 至强 E5 系列处理器的价格相差甚远。适合2S 系统的 Epyc SoCs 也将适合1S 系统,不会降低每个插座的功能 (见表 2)。

内存和I/O

无论是1S 还是2S 设计, 每个 Epyc SoC 都具有相同的内存带宽和容量。这将极大地影响系统设计者创建高性能1S 系统的能力, 因为英特尔通过限制1S 内存带宽和容量来细分其1S 和2S 产品线, 这将使 "向上销售" 客户对2S 设计产生影响。

将 Epyc 从1S 扩展到2S 会消耗一些 I/O 通道。Epyc 2S 设计使用每个 soc 的高速 i/o 通道中的一端连接到另一个 soc 插座。但1S 和 2S Epyc 主板支持相同数量的 PCIe 车道。

从表2可以看出,至强 D 和至强 E3 的内存容量有限, 并且至强 E3 不支持服务器标准 RDIMM。

结论

AMD 的 Epyc 架构将支持功能强大的1S 服务器解决方案。TIRIAS 的研究认为, 性价比高, 加上内存和 i/o扩展, 足以证明 数据中心的客户可以批量采用1S 设计, 因为 AMD 的 Epyc SoC 可靠地解决了大多数1S 的架构和价格的问题。

换句话说,一旦Epyc 1S服务器普遍可用,我们认为购买过度配置的2S服务器将会浪费资金。这是服务器市场在AMD推出双核AMD Opteron和英特尔以实物方式响应后所经历的转变,导致8S和更高的系统销售陷入4S细分市场。从那时起,公共云提供商几乎完全忽略了4S服务器,支持其元服务(MaaS),基础架构即服务(IaaS)和平台即服务(PaaS)中的2S配置。

从软件开发的角度来看, 开发 Epyc 1S 解决方案与开发其他服务器处理器没有什么不同。此外, 客户还可以设计性能最佳的的Epyc 2S 解决方案,他们可以使用完全相同的 Epyc sku 实现这一目标。

从客户的角度来看, 每个服务器都应该支持给定应用程序 (用户数、事务数、吞吐量等) 的基准性能。无论服务器是1S 还是 2S, 只要它满足或优于企业的基准性能水平即可。目前的挑战是, 在 Epyc 之前, 供应链中所有模块都不同。Epyc 的高核心计数和强达的功能应使 AMD 能够将仅有一个处理器的2S 服务器的简单增长转化为专用1S 服务器设计的扩展市场。

AMD 设计了 Epyc 来解决企业级服务器部署问题。我们期待 Epyc 性能指标和 TCO 分析作为其推出日期方法, 以进一步量化其1S 优于英特尔至强处理器的优势。

-

amd

+关注

关注

25文章

5466浏览量

134081 -

服务器

+关注

关注

12文章

9123浏览量

85320 -

系统芯片

+关注

关注

0文章

38浏览量

18369

原文标题:AMD服务器CPU EPYC将终结Intel暴利时代!

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于浏览器/服务器体系结构实现设备远程监控系统的设计

Microarchitecture指令集体系结构

了解体系结构 - 介绍 Arm 体系结构

Arm的DRTM体系结构规范

ARM服务器基础系统体系结构7.1平台设计文档

MicroWindows 体系结构及应用程序接口

LTE体系结构

网络体系结构,什么是网络体系结构

软件体系结构的分析

Linux内核的处理器体系结构的详细资料说明

AMD的新服务器体系结构和设计

AMD的新服务器体系结构和设计

评论