问:我购买了一个双通道ADC,并配置成数字下变频器。但现在有人说其实我有四个转换器!!!难道是我买数据转换器时没留神参加了“买一赠一”活动?

答:自从第一枚单片式硅基模数转换器(ADC)诞生以来,ADC技术一直紧跟硅加工技术快速发展的步伐。

这些年来,硅加工技术已发展到非常高的程度,现在已经能采用经济的方式设计具有很多强大数字处理功能的ADC。早先的ADC设计使用的数字电路非常少,主要用于纠错和数字驱动器。新一代GSPS(每秒千兆样本)转换器(也称为RF采样ADC)利用成熟的65 nm CMOS技术实现,可以集成许多数字处理功能来增强ADC的性能。当采样速率(在GSPS范围内)较高时,庞大的数据负载(每秒比特数)也随之而来。就以AD9680为例,这是一款14位、1.25 GSP S/1GSPS/820 MSPS/500 MSPS JESD204B双通道模数转换器。在达到最高采样速率1.25 GSPS时,ADC数据流为:

14 bits × 2 converter channels × 1.25 Gbps = 35 Gbps

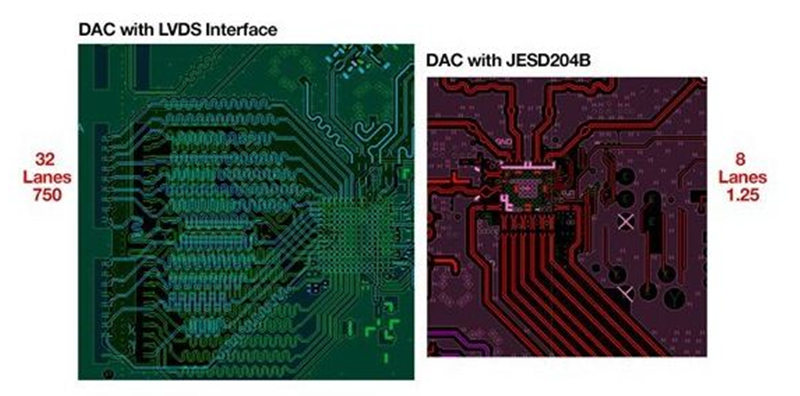

这样的数据量将需要使用大量的LVDS路由通道来提取数字数据。为便于实现如此庞大的吞吐量,JESD204B标准应运而生。JESD204B是一种高速数据传输协议,采用8位/10位编码和加扰技术,旨在确保足够的信号完整性。针对JESD204B标准,总吞吐量变为

通过使用JESD204B标准,以每通道12.5 Gpbs对四个高速串行通道上的数据吞吐量进行划分。将其与LVDS接口(其中线路速率电容约为1 Gbps/通道)比较,芯片可能需要超过28对!快速查阅AD9680数据手册可以发现,就连设置链路都要面对一大堆字母组合。早先的LVDS ADC比较易于实现,而新一代JESD204B ADC则稍微复杂一些。如果考虑到内部数字下变频器(DDC)的设置,则会更加复杂。尽管如此,ADC设置主要取决于三个字母:

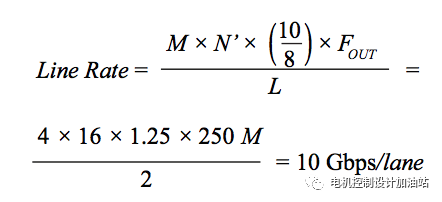

L = 每条JESD204B链路的通道数M = 每条JESD204B链路的转换器数F = 每条JESD204B链路中每帧数据的8位字节数

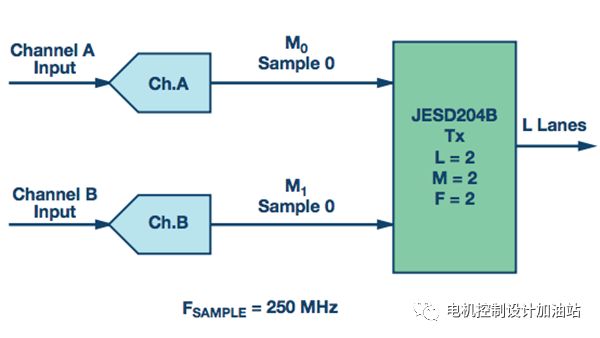

就以AD9250为例,这是一款14位、250 MSPS JESD204B双通道模数转换器。图1显示了AD9250采用默认设置的框图。

图1. 设置AD9250。

在此设置中,由于AD9250中没有其他数字处理任务,所以JESD204B链路(JESD204B发射器)一目了然。对于JESD204B链路来说,通道A为转换器“0”( M0 ),而通道B为转换器“1”(M1),这就意味着“M”的值为2。此设置的总线路速率为

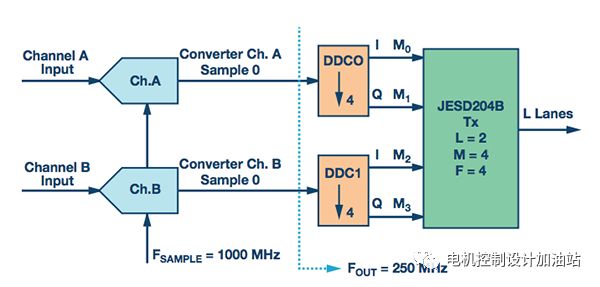

将其与采样速率为1 GSPS的AD9680进行比较—在后面这种情况下,有两个数字下变频器(DDC)用于复数(I/Q)设置。图2显示AD9680使用数字下变频器(DDC)对1 GSPS采样数据进行4倍抽取。因此,输出采样速率(FOUT)为250 MSPS。

图2. 设置AD9860-1000,两个DDC设为4倍抽取。

从图2中可以明显看出,AD9680可以通过内部数字下变频器(DDC)有效降低采样速率。由于每个DDC输出一个16位数据流,此时实际的(物理的)转换器位流已与JESD204B字母汤中的“M”参数互不相干。依照标准,M为每条链路的转换器数。

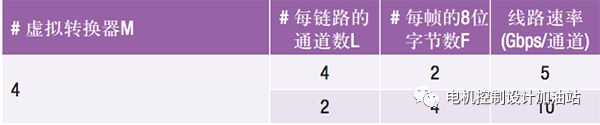

在修改后的情形中,“M”变成一个“虚拟”转换器的参数。虽然从物理上看AD9680只有两个ADC通道(A与B),但是当DDC启用复数输出模式后,就会有四个不同的(16位)数据流通向JESD204B接口。对于JESD204B接口来说,这就相当于此时有四个转换器在发送位流。所以,“M = 4”或转换器乘法发挥了作用。在这种情况下,输出线路速率变为:

这里可以明显看出AD9680 JESD204B接口的灵活性,因为其提供了两个可用选项,具体取决于接收逻辑(ASIC或FPGA)对线路速率的可接受性。表1列出了图2所示AD9680设置中JESD204B接口的可用选项。

表1. AD9680 ADC的JESD204B输出接口配置选项

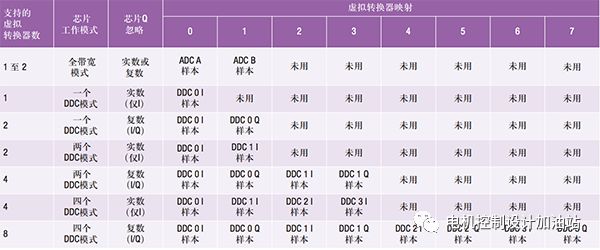

对于双通道ADC(如集成四个DDC的AD9680),表2显示了用于各种配置的虚拟转换器映射。

表2. AD9680 ADC的JESD204B输出接口配置选项

-

转换器

+关注

关注

27文章

8694浏览量

147080 -

变频器

+关注

关注

251文章

6547浏览量

144509 -

DDC

+关注

关注

2文章

90浏览量

37088

原文标题:说变就变!通过DDC魔法乘以ADC的虚拟通道数

文章出处:【微信号:motorcontrol365,微信公众号:电机控制设计加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

JESD204B串行接口时钟的优势

FPGA高速数据采集设计之JESD204B接口应用场景

JESD204B协议介绍

JESD204B的优势

基于JESD204B高速数据传输协议 通过DDC魔法乘以ADC的虚拟通道数

JESD204B SystemC module 设计简介(一)

JESD204B标准及演进历程

JESD204B协议相关介绍与具体应用实例

JESD204B使用说明

为便于实现如此庞大的吞吐量,JESD204B标准应运而生

为便于实现如此庞大的吞吐量,JESD204B标准应运而生

评论