为了及时完成捷变射频收发器设计,使用针对宽带而优化的高性能转换器及其相关的高速FPGA是有必要的,但许多设计人员还需要其它资源。由于器件的复杂性,考虑到互连格式和协议的挑战,以及电路板布局的微妙,“独自一人”或“几乎独立”地完成设计已不再可行。

传统上,SDR平台需要多种技能结合才能实现完整的SDR解决方案,包括RF和ADC设计、数字硬件、SOC装配、DSP硬件和软件开发技能。克服技能缺陷的一种办法是利用参考设计和MatLab等支持工具来帮助完成一个有效实例。

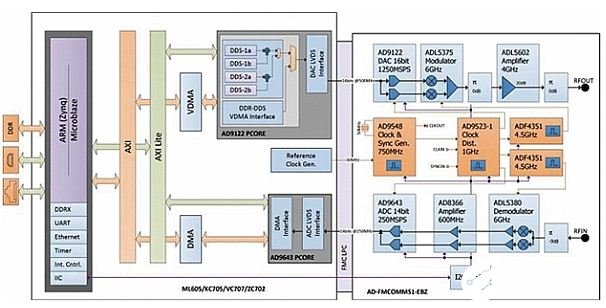

图1:FMCOMMS1-EBZ为众多计算密集型FPGA无线电应用(包括SDR)提供vwin 前端。与FPGA开发平台一起使用时,FMCOMMS1-EBZ能够在物理层实现从基带到RF的一系列无线通信功能。

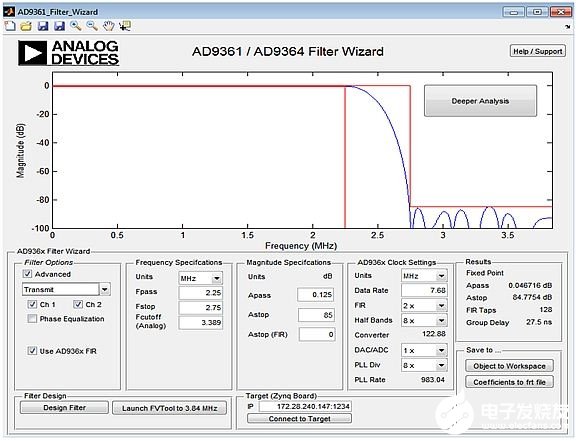

例如,一个常见的SDR挑战是设计可编程滤波器。SDR平台内有可编程TIA滤波器、低通滤波器、数字半带滤波器和可编程FIR滤波器。 每个滤波器都会影响器件链中的下一滤波器。因此,当出现异常时,设计人员可能会发现很难确定问题所在。

利用参考设计,设计人员可以看到不同的滤波器级,了解各滤波器级如何在通带中产生独特的幅度滚降和群延迟。通过了解该独特的幅度滚降和群延迟是如何及在哪里发生的,设计人员就能补偿FIR滤波器中的延迟,进而在数字基带器件中实现平坦的通带响应。ADI公司wiki知识库提供了很好的参考设计资源。

设计人员的另一个挑战是如何设计FIR滤波器,使其补偿之前所有级的累积影响。这里,可以利用一个滤波器设计MATLAB小应用程序来设计发送器和接收器的FIR滤波器,帮助设计人员考虑来自滤波器链中其它模拟和数字滤波器级的幅度和相位响应。

通过选用具有合适特性的器件,并辅以评估工具、应用支持、参考设计以及第三方技术和产品,开发团队将更有可能达成多个设计目标,并满足成本和时间上的要求。

图3:MathWorks的MATLAB可用于无线SDR系统和器件中的复杂滤波器设计。这里,AD-FMCOMMS2-EBZ和AD-FMCOMMS4-EBZ SDR开发平台上集成的ADI公司AD9361和AD9364 RF收发器的模型,显示了如何利用一个示例系统设计中产生的系数来为内部FIR滤波器设计一个滤波器。

无论系统工程师喜欢使用FMC还是商用SDR平台,借助支持工具和资源将令系统工程师领先一大步。

责任编辑:gt

-

收发器

+关注

关注

10文章

3424浏览量

105960 -

射频

+关注

关注

104文章

5573浏览量

167694 -

SDR

+关注

关注

7文章

233浏览量

50460

发布评论请先 登录

相关推荐

有关SDR平台咨询

软件无线电(SDR)平台带你从频谱共享到5G研发

基于AD9361的SDR商用平台

Spartan 6是否支持SDR SDRAM?

介绍SDR的技术原理 以SDR LTE系统为例进一步解析SDR系统的工作流程

5G网络架构,5G中的SDR和SDN是什么?

利用捷变收发器来简化SDR平台设计复杂度并提高实际运算效能

SDR的技术原理介绍及案例分析

基于DSP和赛灵思Spartan-6的SDR系统设计与实现

RF SDR设计:ADI/Xilinx SDR原型制作系统、工具流程资料下载

SDR平台如何借助支持工具和资源在设计系统中实现应用

SDR平台如何借助支持工具和资源在设计系统中实现应用

评论