设计工程师通常在FPGA上实现FIFO(先进先出寄存器)的时候,都会使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其针对性变差,某些情况下会变得不方便或者将增加硬件成本。此时,需要进行自行FIFO设计。本文提供了一种基于信元的FIFO设计方法以供设计者在适当的时候选用。这种方法也适合于不定长包的处理。

FIFO在数字通讯芯片领域中有两个主要的作用,缓冲数据和隔离时钟。对于FIFO的设计,最关键的问题是如何实现RAM的读写双方的信息交换。一般情况下,设计者都直接调用厂商为自己的FPGA专门打造的FIFO核。基本单元是FIFO所使用的RAM的一次读写操作的最小单元,如一个字节,一个字或者是一个双字。所谓操作粒度,即FIFO的读写双方的信息交换是基于这些基本单元。

ATM应用中的FIFO设计

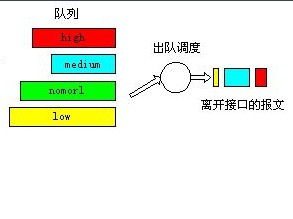

以ATM的设计为例,在ATM的相关设计中,设计者则更多希望一个FIFO对外给出的信息是“现在FIFO中还剩下几个信元”。要实现这一功能通常有两种方法:

1. 调用厂商提供的以操作粒度为基本单元的通用FIFO,然后在这个FIFO的外面再加上一个“套子”。这个套子里面设计一些计数器,根据计数内容对外提供相应的信息。

2. 设计操作粒度为信元的定制FIFO。这样对外直接提供设计者最希望得到的信息,即FIFO中还有多少个信元。

设定FIFO最多可以存放4个信元。基本单元为字节,因此RAM的数据宽度为8位,一个信元的长度为53字节。

把RAM分成4个信元区域,读写地址的高二位指明信元区域,低六位指明信元区域内的字节地址,这样组合成8位读写地址。读写双方的信息交换是互相通知对方还有多少个信元在FIFO中。读写双方都拥有自己的记分牌(Scoreboard),这个记分牌可以由一个四位的寄存器来实现,每一位对应一个信元区域。当一个信元区域中有一个完整的信元的时候,记分牌的相应的寄存器被设置为‘1’,否则为‘0’。读出方读出一个信元,修改自己记分牌的动作叫做清位。写入方写入一个完整信元,修改自己记分牌的动作叫置位。

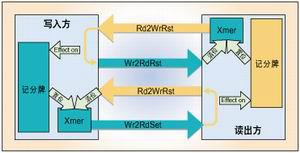

从逻辑上说,只需要读出方把自己的记分牌的信息(清位信息)传送给写入方,同时写入方把自己的记分牌的信息(置位信息)传送给读出方就可以了,即只要构成两条逻辑通道就可以满足需求。但是,在硬件上的实现却要比这种只从逻辑上的思考要复杂。由于读写双方有可能处在不同的时钟域,所以当读写双方交换信息的时候就需要处理信号采样的亚稳态情况。我们使用下面的方法来处理信号亚稳态。

消除信号亚稳态

在读、写入方之间建立下面的四条单向数据通道:传送写入方到读出方的置位信息(Wr2RdSet);写入方到读出方的清位信息(Wr2RdRst);读出方到写入方的清位信息(Rd2WrRst);读出方到写入方的置位信息(Rd2WrSet)。由于读出方只发生清位信息,而写入方只发生置位信息,所以信息本身只有两个。四条通道可以被划分为两个信息组:一个组(Rd2WrRst和Wr2RdRst)传递清位信息,叫清位信息组;一个组(Wr2RdSet和Rd2WrSet)传递置位信息,叫置位信息组。读出方使用清位信息组,写入方使用置位信息组。这样做的目的是为了建立起一个稳定的握手机制。在读出方设置一个专门的发送电路,当此发送电路通过Rd2WrRst发出了清位信息后,等待写入方通过Wr2RdRst通道送回关于这个信息被接收的确认。当收到这个信息的确认后,读出方发送电路复位。同样的,写入方也有一个发送电路,操作过程同读出方一致,无非是使用置位信息组。这两个发送电路都各由四个寄存器组成,一位对应一个信元区域。

为了解决Rd2WrRst进入写入方时引起的信号亚稳态,需要在写入方设置一个专门消除亚稳态的电路模块。根据Rd2WrRst和Rd2WrSet特点不一样,这个模块有多种设计方法,但是其宗旨都是使用连续两次采样的方式。

这里介绍一种比较简单的方法。在设计的时候,把Rd2WrRst和Rd2WrSet的信号都设计为电平方式,即当读出方要发送一个信元区域的清位信息的时候,就把Rd2WrRst信号通道里对应的信元区域位设置为‘1’。这个‘1’电平一直保持到写入方的确认到达。当这个‘1’电平被写入方采样的时候,由于‘1’同步于读出方的时钟,所以很有可能会产生写入方第一次采样为一个不确切值,即通常意义上的亚稳态状态。但是,由于读出方一直保持‘1’电平,所以写时钟在第二次采样的时候就会得到一个稳定的采样样本,从而消除了Rd2WrRst的亚稳态。对于解决Wr2RdSet进入读出方的时候引起的信号亚稳态的方法和读出方一样。

对于Rd2WrSet通道里面的信息,其实是读出方给写入方的置位确认。这个信号的源头是写入方发出的Wr2RdSet,读出方对Wr2RdSet不做任何处理,只是单纯地把它里面的信息拷贝到Rd2WrSet通道并回送写入方,当Rd2WrSet进入写入方的时候,进入消除亚稳态电路,最后复位写入方的发送电路。对于Wr2RdRst通道里面的信息操作也和Rd2WrSet的信息一样。整个电路的结构如图所示。

对于信元字节的计数,和通常的方式一样,发生在FIFO的外部,外部的电路需要为FIFO提供基于信元字节计数到信元尾的信息。这个信息用来使得FIFO的读写地址指针从一个信元区域跳到下一个信元区域。FIFO向外部电路提供FIFO有多少个信元的信息。这个信息加上外部电路自己产生的计数信息,可以知道FIFO是否将满,FIFO是否将空等一系列信息。

通过上面的描述,可以看到外部电路能够非常自由地控制FIFO的读写地址的变化,这是通用FIFO所不具备的功能。由于FIFO给出的是信元的信息,设计者在做有关UTOPIA协议的电路的时候,可以很方便地使用这个信息。同时,如果设计需要UTOPIA的查错功能,这样的情况更需要外部电路能控制FIFO的地址变化。从而使得写地址指针回跳以覆盖原先写入的数据。显然,这一功能也是通用FIFO很难实现的。

本文小结

对于这样的FIFO应用还可以延伸到对于非定长包的处理,比如说以太包。由于以太包的特点,要在FPGA中完全存储一个以太包需要的硬件资源很大,所以,有时候对于以太包的处理都会先把其分为固定长的数据块,并把每一数据块伴以相应的标识以识别他们是属于哪一个以太包。这样一来,就变成了对固定长数据块的处理。因此,上面所述的FIFO的设计方法又可以用来缓存以太包。

-

FPGA

+关注

关注

1629文章

21728浏览量

602953 -

寄存器

+关注

关注

31文章

5336浏览量

120224 -

RAM

+关注

关注

8文章

1368浏览量

114638

发布评论请先 登录

相关推荐

基于信元的FIFO设计如何在FPGA上实现?

异步FIFO结构及FPGA设计

基于PCI接口芯片外扩FIFO的FPGA实现

在FPGA中基于信元的FIFO设计方法实战方法

基于FPGA的FIFO设计和应用

LabVIEW FPGA模块实现FIFO深度设定

基于FPGA的FIFO设计和应用

异步FIFO在FPGA与DSP通信中的应用解析

基于FPGA的异步FIFO设计方法详解

在FPGA上实现自行FIFO设计的方法

在FPGA上实现自行FIFO设计的方法

评论