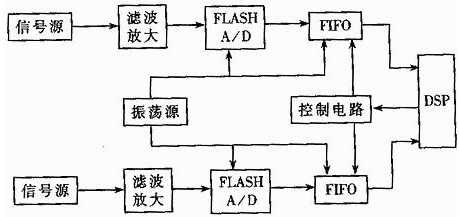

在科学技术高度发展的现代社会,超高速数据采集处理系统越来越广泛地应用于雷达、通讯、图像、军工以及医疗化工等领域。本文介绍的是一种基于12位闪烁式模/数转换器AD9224、大容量FIFO芯片UPD42280及高性能浮点型数字信号处理器TMS320C32的高速数据采集与处理系统。该系统能对两路信号同时采样,存入FIFO缓存器反再按需要由DSP控制进行分时处理。由于缓存的容量较大(256K字节),因此在高达33.3MHz的频率下仍允许对信号连续采样几周波,以保证采样的高度连续。其硬件原理图如图1所示。

1 高速A/D数据采集

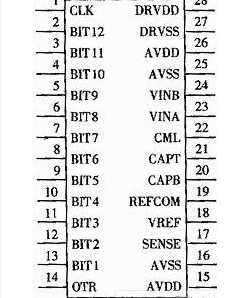

A/D变换器选用了AD公司的AD9224。图2为其管脚图,说明如下:

1(CLK) 时钟输入

2(BIT12) 数据输出最低位LSB

3~12(BIT11~BIT2) 数据输出

13(BIT1) 数据输出最高位MSB

14(OTR) 数据溢出标志位

16、25(AVSS) 模拟地

17(SENSE) 参考选择

18(VREF) 输入参考选择

19(REFCOM) 通用参考(AVSS)

20、21(CAPB、CAPT) 减噪管脚

22(CML) 共模方式

23(VINA) 模拟输入(+)

24(VINB) 模拟输入(-)

27(DRVSS) 数字地

28(DRVDD) 数字电源

AD9224是一种高性能、单电源+5V、最高采样频率为40MSPS的12位ADC。在本设计中,由于FIFO读写时间限制,A/D采样频率最高做到了33.3MHz。AD9224采用CMOS工艺制造,内部集成了基准电压源、宽带输入采样保持放大器等,并且采用四级流水线式结构,前三级每级包括一连接到开关电容器DAC、级间剩余放大器DMAC的闪烁式A/D,第四级只包括闪烁式A/D。闪烁式A/D是目前转换速率最快的ADC。。AD9224采用CMOS工艺制造,内部集成了基准电压源、宽带输入采样保持放大器等,并且采用四级流水线式结构,前三级每级包括一个连接到开关电容器DAC、级间剩余放大器MDAC的闪烁式A/D,第四级只包括闪烁式A/D。闪烁式A/D是目前转换速率最快的ADC。AD9224采用多级流水线结构对输出错误进行逻辑纠正,以保证在整个工作范围内不失码,其数据以二进制形式输出,并带有信号溢出指示位。AD9224在+5V电源下功耗较低,为376mW。其微分非线性误差为0.7LSB,信噪比和失真率为67.5dB。

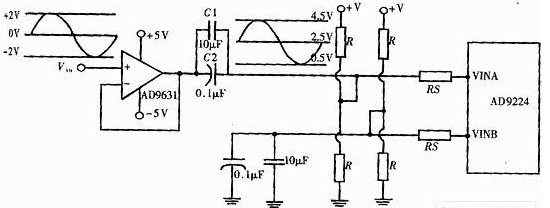

AD9224的输入可以是单端或差分方式。本设计采用的是交流耦合单端输入方式。信号经过由放大器AD9631和并联电容组成的电路后被偏置为关于AVDD/2(2.5V)对称的正弦波,C1和C2由0.1μF的陶瓷电容和10μF的钽电容并联,电容和电阻共同组成了一个高通滤波器。图3所示为A/D部分的电路设计图。

2 数据缓存

A/D采样一点转换一点。由于本系统的采样速率高达几十MSPS,如果存储控制系统不能及时接收数据的话,则上次转换的数据马上就被下一个数据所覆盖,很容易造成数据混乱。一般常用的DMA控制器所能达到的传输速率约为5Mb/s,即使是高性能的DSP芯片TMS320C32,其自带的DMA通道所允许的A/D最高采样速度也只达到15MSPS,并且受指令执行时间的限制,依然不能直接接受A/D数据线上的数据,因此必须采用高速缓存。目前常用的缓存多为FIFO(先入先出)、SRAM、及双口RAM等。双口RAM和SRAM一般存储量较大,但必须用到复杂的地址发生器。FIFO芯片数据顺序进出,且输入输出口独立,在电路设计上相对简单得多,但由于数据不能按址查询,而是遵循先入先出的原则输出,在软件处理上要复杂一些。FIFO一般价格较贵,且存储量不大。本设计所采用的FIFO是NEC公司生产的UPD42280,其容量为8位256K(实际是262224)字节,数据读写时间为30ns,是一种比较理想的FIFO芯片。该芯片内部采用动态RAM结构,能够自动刷新,当读写完最后一个存储单元后,又会自动回到第一个存储单元。由于A/D有13条数据线(包括OTR位),所以每路用了两片FIFO来接收数据。

3 DSP主处理器及控制电路

主处理器采用的是TI公司生产的TMS320C32PCM40。它是一种高性能的32位浮点型数字信号处理器,内部包括通用寄存器组、程序高速缓冲存储器、专用辅助寄存器单元(ARAU)、两个存储器、两个DMA通道。DSP所具有的高存储空间(32位/16M)、多处理器接口、内部及外部产生的等待状态、一个外部接口端口、两个32位定时器、一个串行口以及多重中断结构等,使其应用得到了很大的加强。

为了加快数据流的传输,克服瓶颈问题,DSP内部采用了哈佛总线结构(指令和数据有各自存储空间,寻址或存取数据、指令有各自的传输总线)而不是通用处理器采用的冯诺依曼结构(指令和数据使用同一存储空间,经由同一总线传输);为了进一步加快数据流的传输,DSP还采用了提高处理器的时钟速度以及先进的处理方法(如流水线处理和并行处理)。这些都使得DSP的各项运算和处理能在一个时钟周期内完成。DSP处理器的运算/处理功能单元要包括乘法器/乘加器(MAC)、算术运算单元(ALU)、移位器、数据地址发生器(DAG)。

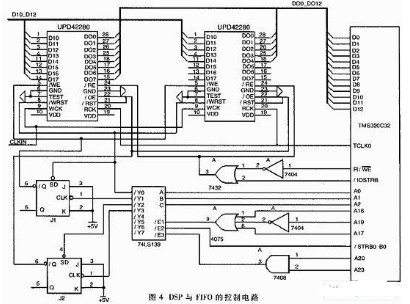

TMS320C32能与8/16/32位数据存储器接口,并且可以进行8/16/32位程序引导,程序存储器可以是16位或32位。它支持广泛的系统寻址方式,实际上属于间接寻址,是一种高效有用的寻址方式。另外,在寻址方式中TMS320C3X提供了一种循环寻址方式,可以在单周期内对整数或浮点数进行并行的乘法和算术逻辑单元(ALU)操作。图4为本设计中一路FIFO与DSP的控制电路。

本设计中由于A/D有13条数据线(包括OTR位),所以每路用了两片FIFO来接收数据。两片FIFO的/WE管脚都连接到上路JK触发器J1的/Q管脚上,以便由DSP控制使其同时接收数据。FIFO的读片管脚/OE与读复位管脚/RST接下路JK触发器J2的/Q端,另一路接Q端以控制上下路选择,FIFO的读时钟由DSP的定时器TCLK0给出。

系统工作过程如下:

上电后,AD9224加上时钟信号即开始数据的转换。写数据时,DSP经过译码电路首先使/Y0输出为低,则两片FIFO的/WRST为低电平,FIFO垢写指针位于0地址处;同时J1被预置,使/WE为低,两片FIFO从0地址开始同步接收A/D转换的数据。由于FIFO没有存储器写满标志,A/D没有控制转换起止标志,因此只能通过软件控制,由DSP延时t(t为FIFO开始转换到写满的时间)后,写74LS138使/Y1为低,J1发生翻转,/WE变为高,写操作被禁止。读数据时,在DSP控制下使/Y2为低,J2被置位,/Q为低,上路FIFO的/RST和/OE同时变低,读指针处于0地址处并允许DSP对其进行读操作。读数据是通过对R/WE、/IOSTRB的共同操作完成的。DSP的处理完该路数据之后,再次写译码器使/Y3为低,J2翻转,/Q为高,上路FIFO的访问被禁止;同时,Q变低,允许读取下路FIFO的数据。

由于FIFO的读烈军属时间所限,本设计的采样时钟没有做到40MHz,而是采用了最高33.3MHz的时钟。时钟信号由66.6MHz的晶振振荡器经过分频后分别接到A/D的CLK端和FIFO的WCK端,以便使FIFO和AD9224采用同一时钟源,保持时序的严格同步。

本设计为通用系统。采用高性能的12位模/数转换器AD9224进行采样,数据精度较高。尽管由于FIFO的读取时间所限,最高采样频率只做到了33.3MHz,但是由于FIFO的容量较大,因此可以连续不同断地采样256k个点。这对于要求高速连续采样的系统是非常适用的,而且省去了大容量的RAM,在一定程序上节省了硬件开支。

-

芯片

+关注

关注

455文章

50712浏览量

423108 -

转换器

+关注

关注

27文章

8694浏览量

147080 -

滤波器

+关注

关注

161文章

7795浏览量

177989

发布评论请先 登录

相关推荐

LTC1294单片12位数据采集系统

基于DSP和以太网的数据采集处理系统

基于DSP 和以太网的数据采集处理系统

基于SOPC的数据采集与处理系统设计

摩擦试验机数据采集与处理系统设计

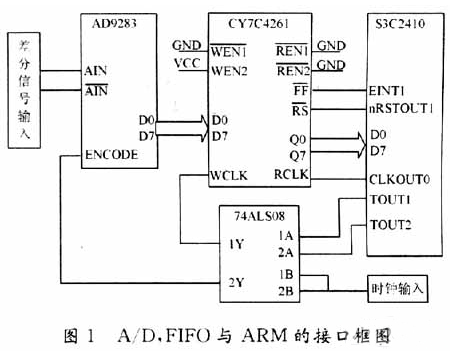

基于FIFO存储器实现高速AD转换器与ARM处理器的接口设计

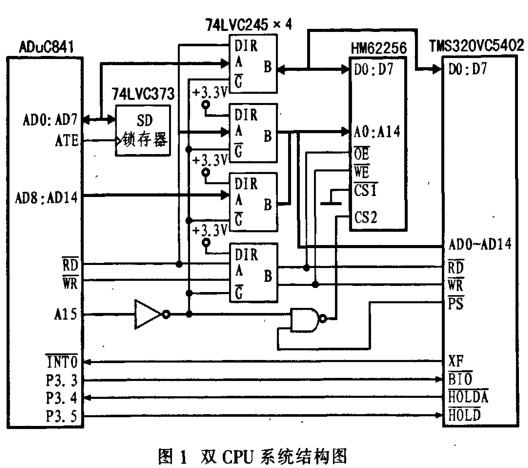

基于TMS320VC5402芯片和ADuC841转换器实现数据采集处理系统的设计

基于12位模/数转换器与FIFO芯片的数据采集处理系统

基于12位模/数转换器与FIFO芯片的数据采集处理系统

评论