随着数字化与测井技术的发展,对测井系统的稳定性、可靠性、兼容性、可升级性等性能提出了更高的要求,本文提出了一种适用于测井系统设备的CPCI(Compact PCI)高性能数据采集板卡硬件设计方案,能够有效地处理来自井下的复杂信号,并通过256 MB/s 高速CPCI总线桥接到主控设备。

本板卡实现的主要功能是井下Encoder(深度脉冲)、Tension(张力)、MMD(Magnetic Mark Detection)和CCL(Casing Collar Locator)等信号的实时采集,采集数据在DSP中完成预处理,通过CPCI总线送入主控制器分析使用,此外,板卡还实现上电自诊断,关键数据在FRAM中的及时存储,RS232 串口定时发送深度数据和接收控制命令等其他功能。

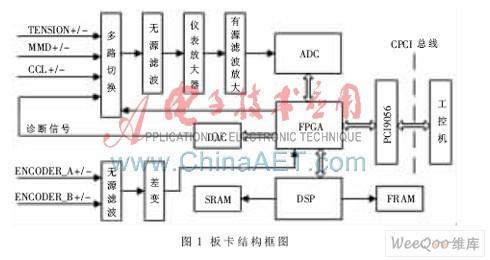

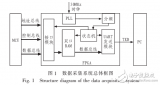

1 板卡总体结构

整个板卡由FPGA、PCI桥片、DSP、A/D和D/A五大部分组成,其中FPGA选用Altera公司高性能低功耗Cyclone III系列芯片,PCI桥片选用PLX公司32 bit 66 MHz PCI9056芯片,DSP选用TI公司TMS320F2812芯片,A/D选用ADI公司16 bit 200 kS/s高精度高速采集芯片AD974,板卡结构框图如图1所示。该板卡工作过程是:板卡上电后,PCI9056向FPGA发出指令控制D/A产生诊断信号,诊断信号经由板卡各级vwin 通路后环回到FPGA,然后FPGA把采集到的诊断信号送入DSP,DSP再通过FPGA把数据送回CPCI总线,完成整个板卡硬件的自诊断。自诊断完成后,D/A处于非工作状态,各信号由井下电缆送入,经过多级滤波放大后进行A/D采集,FPGA完成Tension、MMD和CCL等信号的采集和Encoder信号的处理,最终把数据送入DSP进行预处理,经DSP处理好的数据由CPCI总线送回主控制器。

2 板卡硬件设计

2.1 FPGA控制器的总体设计

本板卡的数字系统共有2个主控制器,分别为数据采集板卡上的DSP和CPCI总线上的CPU主控机,板卡使用PCI9056桥片实现CPCI总线与局部总线间的转化, DSP与CPCI总线通过中断方式实现数据交换。其中FPGA调用QUARTUS软件自带IP核实现32 KB双口RAM,并把双口RAM分成大小相等的两部分,一部分用于CPCI总线向DSP传输数据,另一部分用于DSP向CPCI总线传输数据,避免了总裁的使用和数据的丢失。FPGA作为数据采集板卡数据中转站的同时,主要实现A/D数据的采集,Encoder脉冲信号的去抖动处理、计数和相位判断。FPGA实现功能框图如图2所示。

2.2 A/D数据采集模块设计

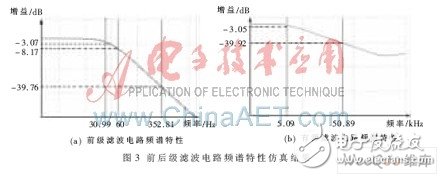

Tension、MMD和CCL等信号均是来自井下的低频微弱小信号,并且由于井下环境复杂,信号容易被干扰,处理不当容易造成数据失效,所以本板卡对三种信号在模拟电路上做了多级滤波放大处理。经实际环境测试,三路信号的主要输入干扰集中在60 Hz以上,因此在输入端设计40 Hz、70 Hz和120 Hz三阶RC滤波电路做前级滤波处理,使滤波器具有窄的过渡带,有效的滤除60 Hz以上的干扰信号,避免干扰信号进一步放大无法滤除,图3(a)为前级滤波电路的频谱特性仿真结果。为了便于信号的采集,需设计运放电路将信号放大至A/D量程范围,这就不可避免会引入PCB、运放等造成的中高频噪声,所以在信号进入A/D前做了进一步有源滤波处理,图3(b)为有源滤波器的频谱特性仿真结果。实际测试结果也证明经过多级滤波,电路抗干扰能力明显增强。

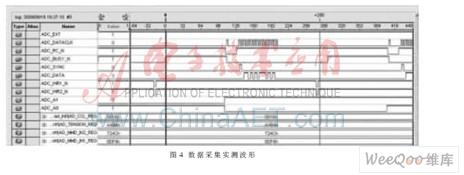

本设计选用了高速高精度ADC AD974芯片,在4个通道间以轮询方式进行采样,每个通道的实际采样转换率为50 kS/s,在FPGA中设置一个数据更新寄存器,进行每一次数据采集完成的实时跟踪。此种工作方式是否能可靠稳定地采集数据关键有两点,一是外部时钟频率是否适中,本设计采用12 MHz的频率,二是要保证A/D内部的采样时间(Acquisition Time)不能小于1 μs,并且4个通道在轮询切换时,地址锁存信号WR1和WR2要在采样前一个周期设置完成。

AD974在板卡上电后用Quartus II SignalTap实时观测的时序如图4所示。其中ADC_A0和ADC_A1为A/D4个通道地址编码信号,ADC_WR0_N和ADC_WR1_N为地址锁存信号,低电平有效,当前锁存地址作为下一次采集通道有效地址。当ADC_RC_N信号置为低电平时A/D开始将采集到的模拟信号向数字信号转换,并在此时送出一个时钟周期的ADC_DATACLK信号,使能A/D同步信号,此时如果A/D空闲则ADC_BUSY_N信号自动拉低,表示A/D已经开始转换数据,随后将ADC_RC_N置高并送出采样时钟信号,便可在ADC_DATA上开始读前一次转换完成的数据。当本次A/D数据转换完成后ADC_BUSY_N信号将自动置高,表明A/D本次转换完成,进入下一次模拟信号采样。

2.3 Encoder信号处理模块设计

Encoder信号在实际设备上分为两路信号,分别为A信号和B信号,当井下设备上提时A信号相位超前B信号90°,当井下设备下放时A信号相位滞后B信号90°,脉冲信号的数量体现测井设备在井下的深度,此信号是测井系统的重要信号之一,如果测量不准, 可能会导致测井资料作废, 甚至带来生产事故。实测Encoder信号从井下设备传送到地面时,会有尖峰脉冲干扰引入,所以本板卡在硬件上采用RC无源滤波器去除信号的尖峰脉冲,通过FPGA在软件上对信号进行去抖动处理、计数和相位判断,能够准确计数并与系统时钟同步。

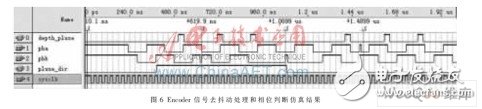

FPGA中对Encoder脉冲信号的去抖动处理和相位判断设计电路见图5,其中depth_pluse为去抖动后的脉冲信号,结合depth_dir完成脉冲计数,当depth_dir为正时,计数脉冲自加,depth_dir为负时,脉冲计数自减。本文用QUARTUS软件自带仿真工具对Encoder信号做的仿真波形,见图6,如波形所示,在时间节点619.9 ns、1.069 9 μs和1.489 9 ?μs处分别对A信号和B信号加入了干扰脉冲,但结果表明本设计可以对干扰脉冲完全滤除。

本文给出了一种高性能测井数据采集板卡的设计方法,板卡在设计中,模拟部分采用多级滤波、高精度A/D,使得数据采集稳定可靠,Encoder深度脉冲信号在硬件滤波的基础上做了软件优化处理,明显增强了抗干扰能力,数字部分采用FPGA和DSP相结合,使板卡具有很高的灵活性、可靠性和可升级性。经大量测试,板卡运行稳定,并在实际系统中得到应用。

-

FPGA

+关注

关注

1629文章

21729浏览量

602964 -

芯片

+关注

关注

455文章

50714浏览量

423115 -

数据采集

+关注

关注

38文章

6053浏览量

113618 -

总线

+关注

关注

10文章

2878浏览量

88051 -

CPCI

+关注

关注

6文章

70浏览量

32829

发布评论请先 登录

相关推荐

基于PCI总线的微弱信号采集模块的设计方案

数据采集卡/分布式采集模块/无线通讯采集模块/嵌入式系统

基于FPGA的数据采集控制器IP核的设计方案和实现方法研究

基于FPGA的高速数据采集系统该怎么设计?

基于ARM和FPGA的微加速度计数据采集设计方案

一种测井数据采集系统设计

DSP+FPGA实现测井数据采集系统

CPCI数据总线接口的设计与实现

基于CPCI总线与FPGA芯片的测井数据采集智能IO板卡设计方案

基于CPCI总线与FPGA芯片的测井数据采集智能IO板卡设计方案

评论