引言

硬件描述语言(HDL)是相对于一般的计算机软件语言如C,Pascal而言的。HDL是用于设计硬件电子系统的计算机语言,它描述电子系统的逻辑功能、电路结构和连接方式。设计者可以利用HDL程序来描述所希望的电路系统,规定其结构特征和电路的行为方式,然后利用综合器和适配器将此程序变成能控制FPGA和CPLD内部结构,并实现相应逻辑功能的门级或更底层的结构网表文件和下载文件。VHDL(VeryHigh Speed Integrated Circuit Hardware descriptionLangtuage)主要用于描述数字系统的结构、行为、功能和接口。与其他的HDL语言相比,VHDL具有更强的行为描述能力,从而决定了它成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结构。从逻辑行为上描述和设计大规模电子系统的重要保证。在文献中作者从不同的角度阐述了EDA技术的应用,它具有功能强大、描述能力强、可移植性好、研制周期短、成本低等特点,即使设计者不懂硬件的结构,也能进行独立的设计。本文以Alter公司提供的Max+PlusⅡ为平台,设计一个可变速的彩灯控制器,可以在不修改硬件电路的基础上,仅通过更改软件就能实现任意修改花型的编程控制方案,实现控制16只LED以8种花型和4种速度循环变化显示,而且设计非常方便,设计的电路保密性强。

1设计原理

用VHDL进行设计,首先应该理解,VHDL语言是一种全方位硬件描述语言,包括系统行为级,寄存器传输级和逻辑门级多个设计层次。应充分利用VHDL“自顶向下”的设计优点以及层次化的设计概念,层次概念对于设计复杂的数字系统是非常有用的,它使得我们可以从简单的单元入手,逐渐构成庞大而复杂的系统。

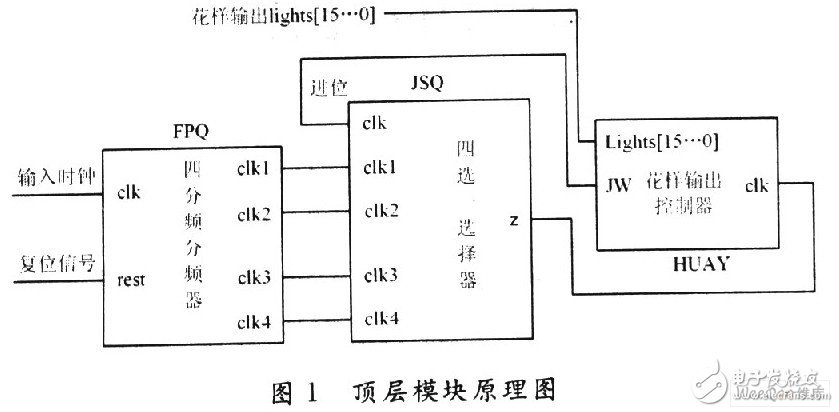

首先应进行系统模块的划分,规定每一个模块的功能以及各模块之间的接口,最终设计方案分为三大模块:16路花样彩灯控制器、四频率输出分频器、四选一控制器。四选一控制器从分频器中选择不同频率的时钟信号输送到彩灯花样控制器,从而达到控制彩灯闪烁速度的快慢和花型的的变换。

下面是本次设计的顶层模块原理图如图1所示。

2 子模块及其功能

(1)四频率输出分频器。根据要求有4种速度的变化,每种都要显示8种花样,就要用到三位计数器和16位数字译码器。其次,速度有4种变化,而只有一个输入的时钟信号,所以要对输入的时钟信号进行分频,本次设计采用了二分频、四分频、八分频和15分频得到4种不同频率的信号。

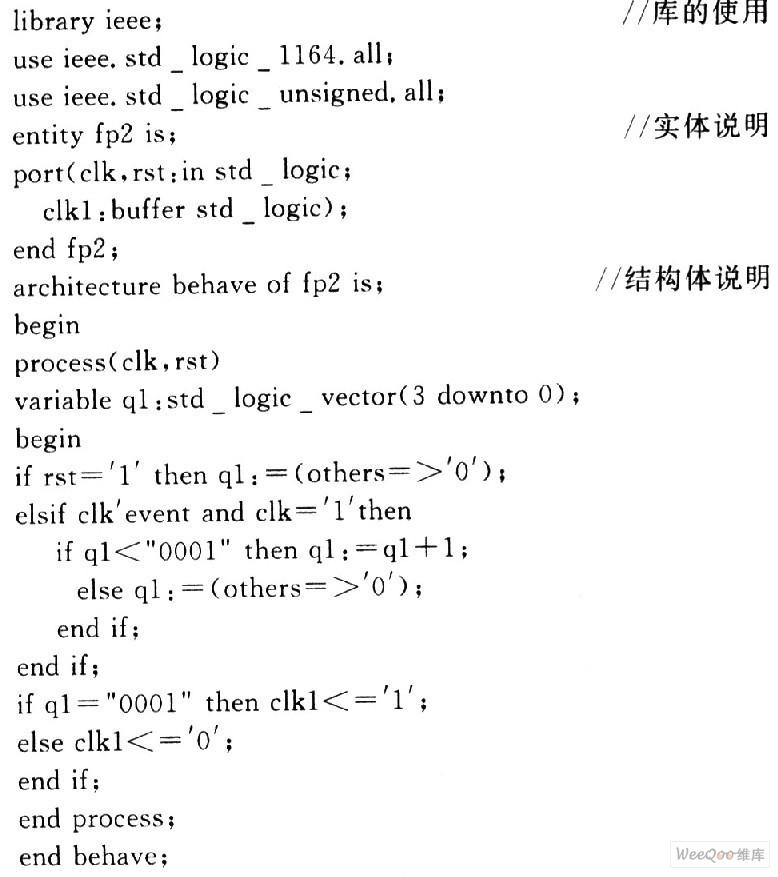

二分频电路的程序代码如下:

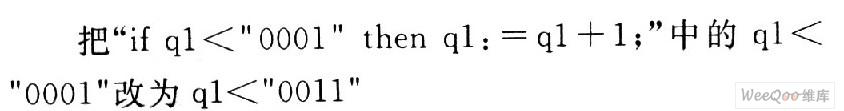

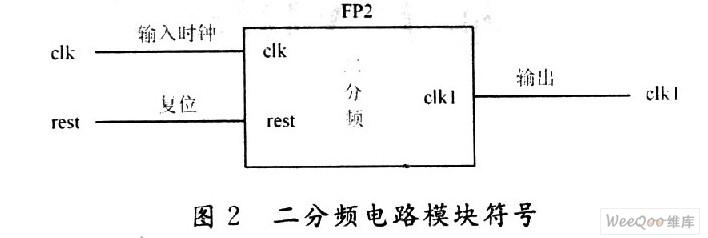

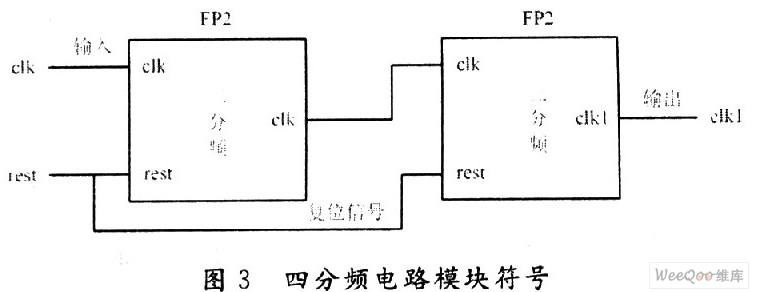

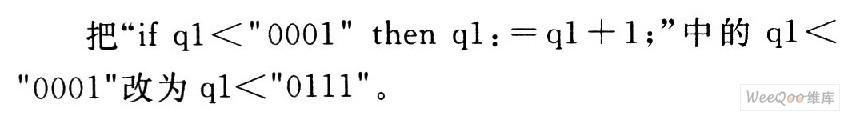

四分频电路的设计有两种方案:一是把两个二分频电路串联起来(见图2,3),实现四分频;二是修改二分频电路的程序代码来实现,做如下修改:

同理,八分频电路的设计也有两种方案:一种是把两个四分频电路串联起来,实现八分频;一种是修改二分频电路的程序代码,只需做如下修改即可:

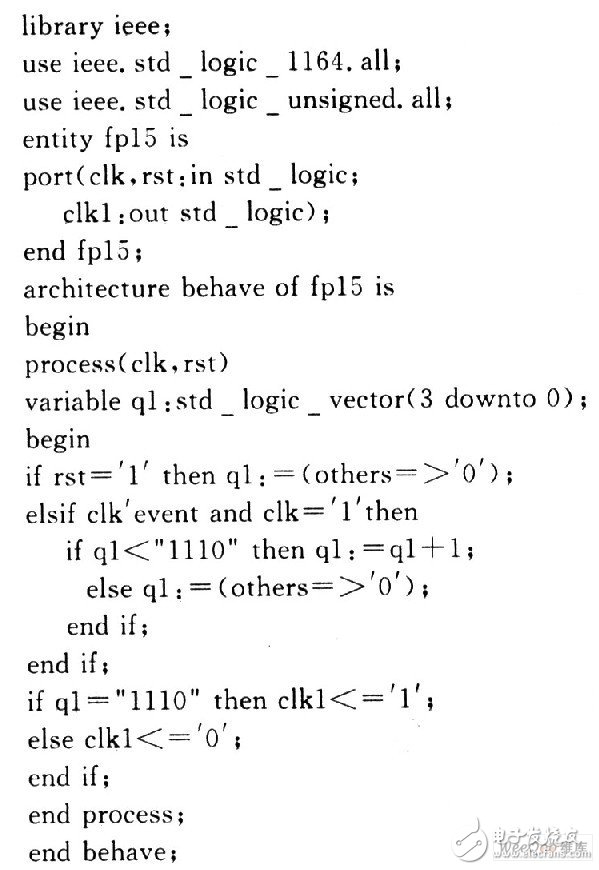

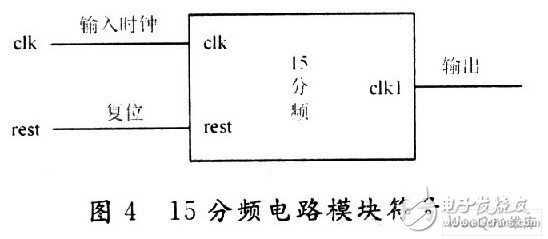

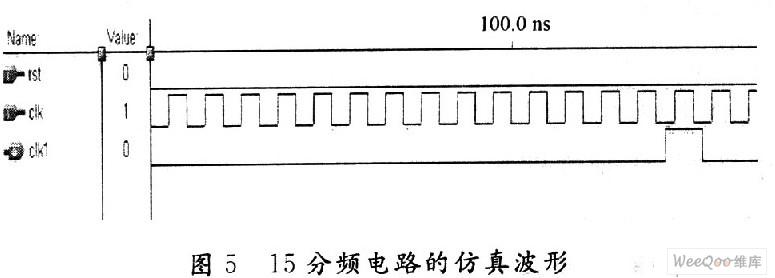

15分频电路如图4所示,仿真图如图5所示。代码如下:

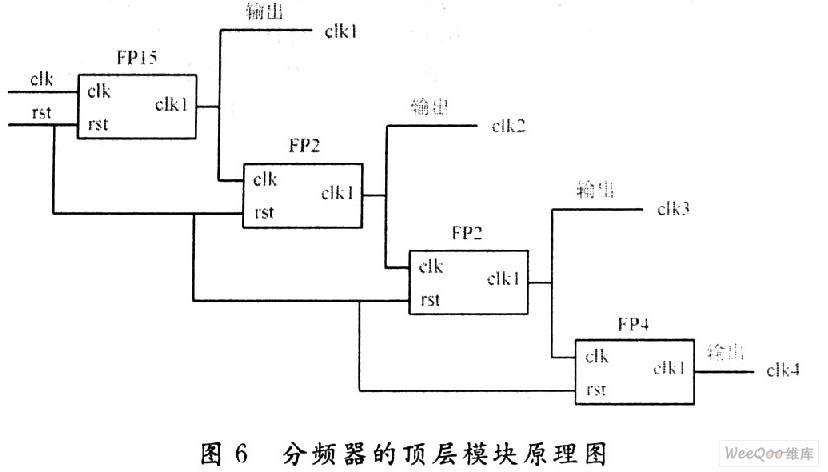

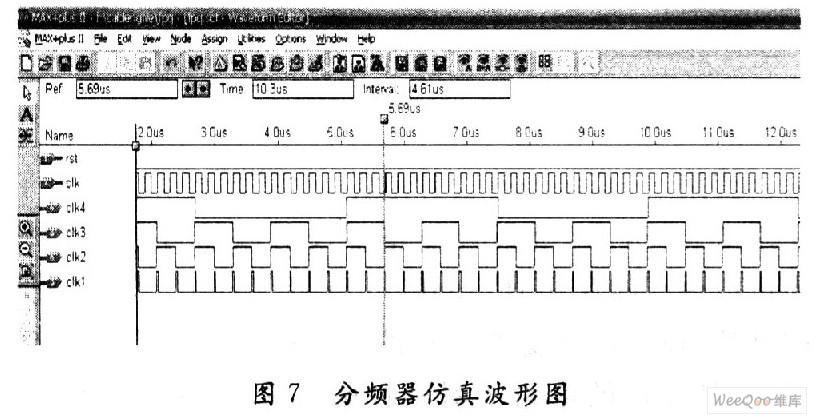

四频率输出分频器的顶层模块原理图如图6所示,仿真波形如图7所示。

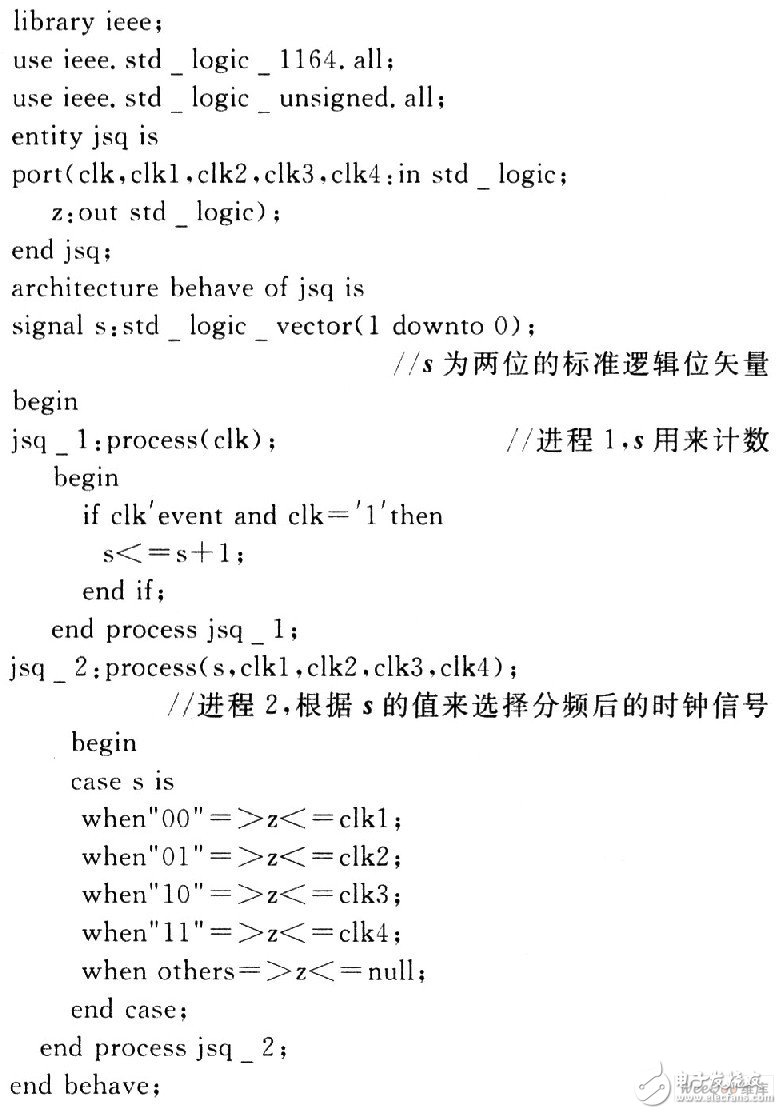

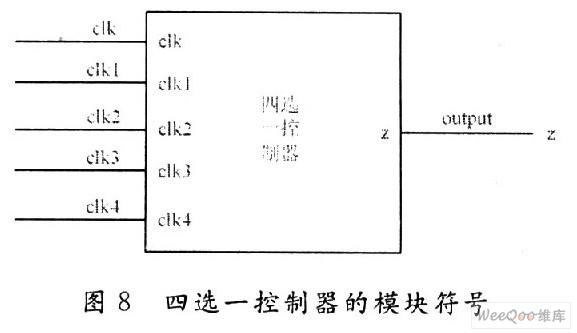

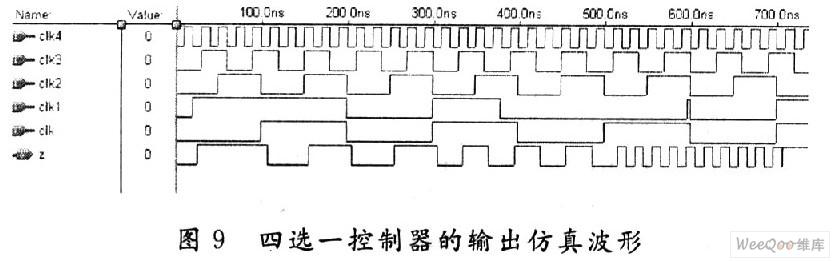

(2)四选一控制器。四选一控制器的功能是从分频器中选择不同的时钟信号送给彩灯控制器,实现彩灯闪烁频率的变化,如图8,9所示。源代码如下:

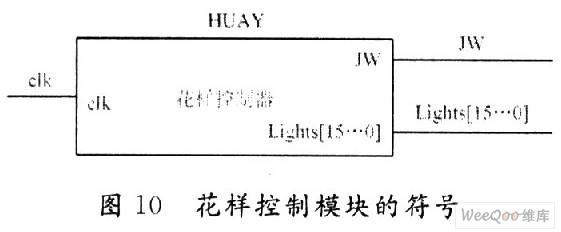

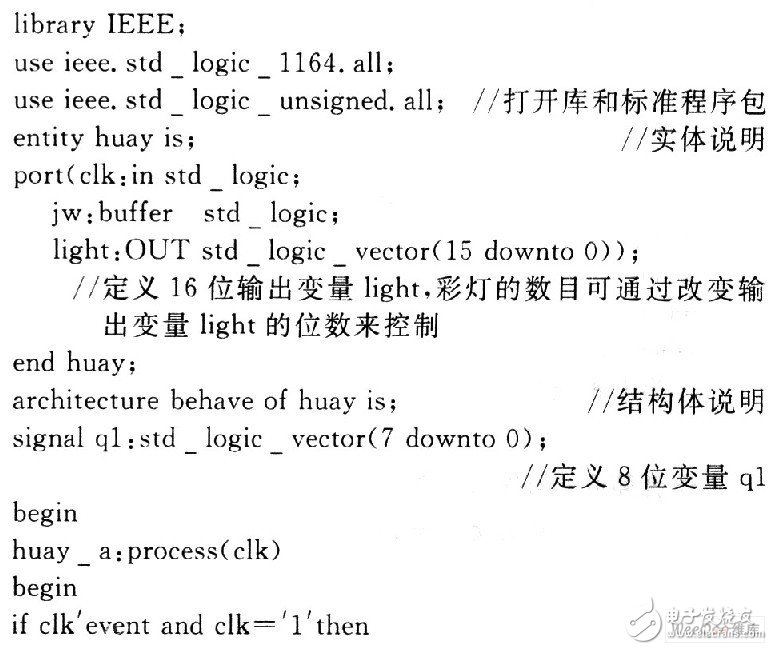

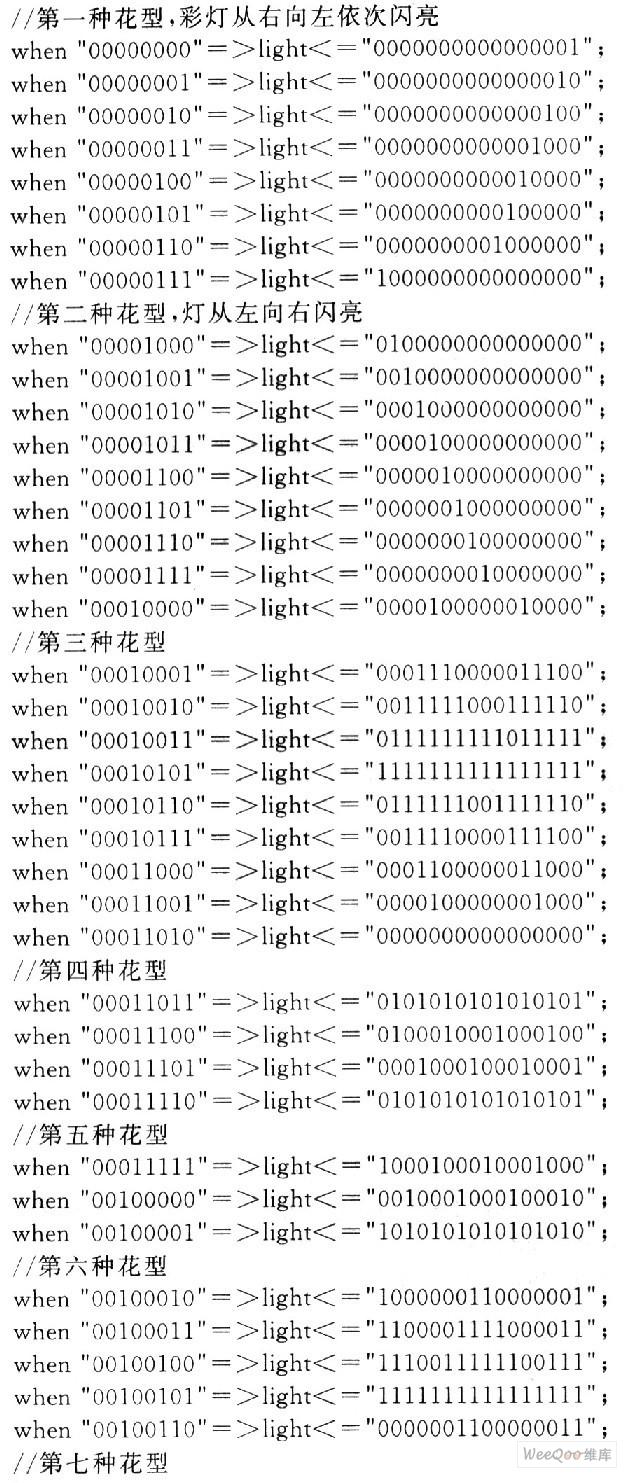

(3)彩灯控制器。彩灯控制器电路是整个设计的核心,它控制整个设计的输出效果也就是图案的样式变化。在电路中用1代表灯亮,用O代表灯灭,由0,1按不同的规律组合代表不同的灯光图案,同时使其选择不同的频率,以实现多种图案及多种频率的花样功能显示。该程序充分证明了用VHDL设计电路的灵活性,即可以通过改变程序中输出变量的位数来改变彩灯的数目。如图10,1l所示。

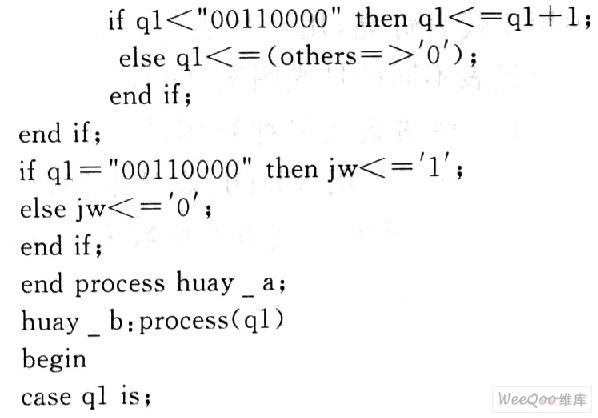

代码如下:

3 结语

使用VHDL语言设计电路,思路简单,功能明了。使用Max+PlusⅡ设计电路不仅可以进行逻辑仿真,还可以进行时序仿真,使用PLD不仅省去了电路制作的麻烦,还可以反复进行硬件的实验,非常方便地修改设计,且设计的电路的保密性强。总之,采用EDA技术使得复杂的电子系统的设计变的简单易行,提高了设计的效率。

-

控制器

+关注

关注

112文章

16332浏览量

177806 -

寄存器

+关注

关注

31文章

5336浏览量

120230 -

vhdl

+关注

关注

30文章

817浏览量

128119

发布评论请先 登录

相关推荐

Verilog与VHDL的比较 Verilog HDL编程技巧

Verilog vhdl fpga

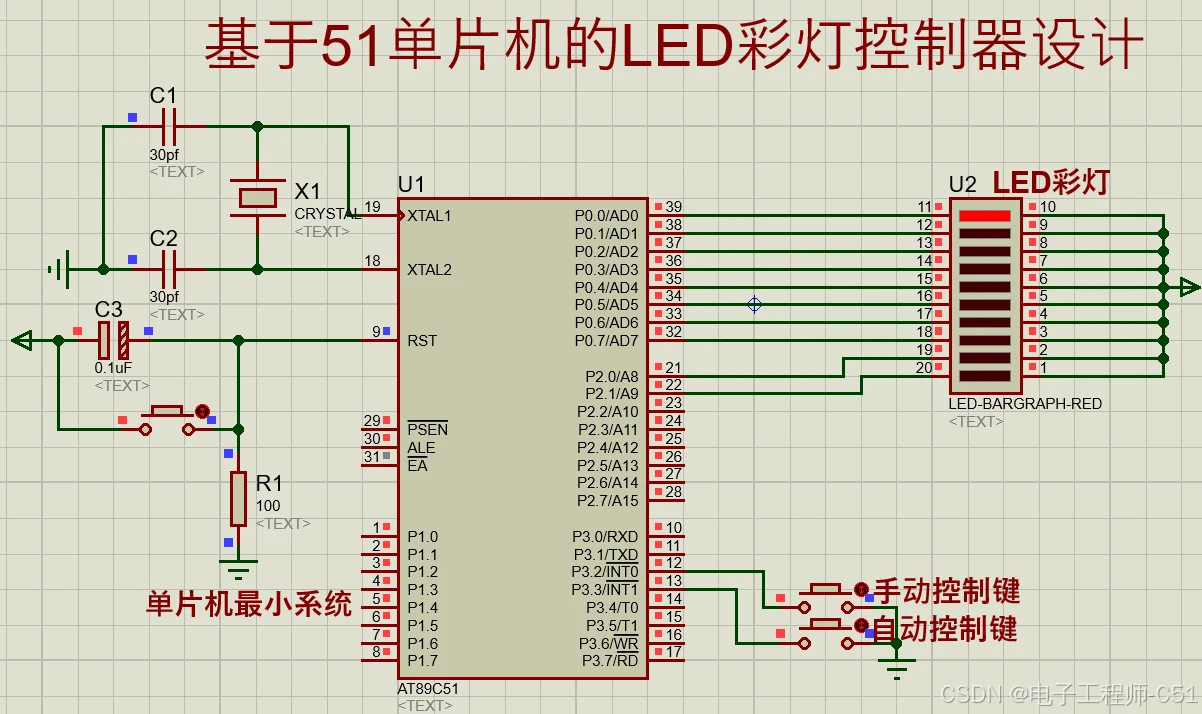

基于51单片机的LED彩灯控制器设计

运动控制器的主要功能是什么?

PID控制器与PWM控制器的区别

PID控制器与开关控制器的区别

基于非线性自适应学习控制器的四轴飞行器避障方案

麦爵士madrix麦觉仕幻彩灯条灯带智能像素灯工程安装经验详解

使用VHDL语言设计可变速彩灯控制器

使用VHDL语言设计可变速彩灯控制器

评论