初识Verilog描述-1

“Verilog不同于C,Python,JAVA等软件语言,Verilog是以数字电路知识为背景支撑,以对数字电路系统进行描述的一门语言。因此用Verilog描述数字电路,必须要有数字电路知识为背景支撑。否则描述出来的电路性能将会很差。本篇我们先了解一下最基本的Verilog对数字电路描述的方法与代码风格,具体语法细节在这不做过多解释。”

在了解Verilog基本构成之前,先要了解数字电路里面有什么元素需要被描述。

如下图所示,为一个实例电路外部原理图:

从外部看一个电路需要描述的元素如下:

电路名字

输入端口以及位宽

输出端口以及位宽

端口描述有两种方式。

以上图为例:

(1)

module share_1(

clk,

rst_n,

a,

b,

data_out

);

input clk;

input rst_n;

input[7:0] a;

input[7:0] b;

output[8:0] data_out;

(2)

module share_1(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output [8:0] data_out

);

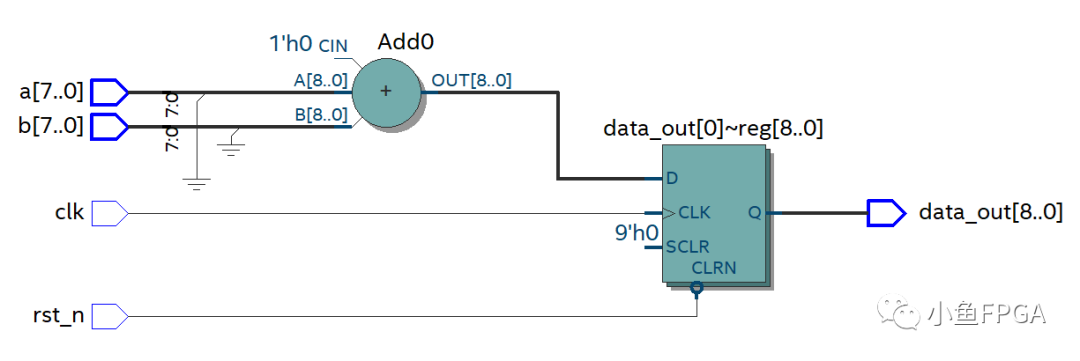

下图为其内部电路结构:

电路内部需要描述元素有:

信号的类型:reg型(所有在always电路里面将要做改变的信号),wire型(电路信号连线)

如上例电路:输入信号本来就为电路信号连线,且在端口声明中已经声明,无需再做wire 声明。

输出信号data_out是寄存器的输出,因此声明为: reg[8:0] data_out;

节点信号add_out(对应电路上的OUT),为加法器的输出。如果加法器是用always块实现的,如下:

always @( * ) begin

add_out = a+b;

end

则声明为reg型: reg[8:0] add_out;

如果加法器是用assign语句实现的,如下:

assign add_out = a+b;

则声明为wire型: wire[8:0] add_out;

注意:所有声明必须带上位宽,否则系统工具将其默认为单位宽,如上信号add_out为9位宽,因此声明为 reg [8:0] add_out;

组合逻辑电路: 可以利用 assign 或者 always @(*) 语句描述。一般复杂的组合逻辑电路利用 always @(*)语句块描述。如上加法器的实现既可以用always语句实现,也可以利用assign语句实现。

寄存器(有如下几种常用的不同的寄存器模型):

(1) 时钟信号上升沿驱动,复位信号低电平有效,与时钟异步复位:

always @( posedge clk or negedge rst_n ) begin

if( !rst_n )

data_out <= 8h00;

else

data_out <= data_in;

end

(2)时钟信号上升沿驱动,复位信号高电平有效,与时钟异步复位:

always @( posedge clk or posedge rst ) begin

if( rst )

data_out <= 8h00;

else

data_out <= data_in;

end

(3) 时钟信号下降沿驱动,复位信号高电平有效,与时钟同步复位:

always @( negedge clk ) begin

if( rst_n )

data_out <= 8h00;

else

data_out <= data_in;

end

(4)时钟信号上升沿驱动,复位信号低电平有效,与时钟同步复位,并且带有高电平使能信号:

always @( posedge clk ) begin

if( !rst_n )

data_out <= 8h00;

else if( enable )

data_out <= data_in;

else

data_out <= data_out;

end

给出两种完整的描述方式,大家自行体会,电路功能为带寄存器输出的8位无符号数加法器:

(1)

module share_1(

clk,

rst_n,

a,

b,

data_out

);

input clk;

input rst_n;

input[7:0] a;

input[7:0] b;

output[8:0] data_out;

reg[8:0] data_out;

wire[8:0] add_out;

assign add_out = a+b;

always @( posedge clk or negedge rst_n ) begin

if( !rst_n )

data_out <= 9h00;

else

data_out <= add_out;

end

endmodule

(2)

module share_1(

input clk,

input rst_n,

input [7:0] a,

input [7:0] b,

output [8:0] data_out

);

reg[8:0] data_out ;

reg[8:0] add_out;

always @( * ) begin

add_out = a+b;

end

always @( posedge clk or negedge rst_n ) begin

if( !rst_n )

data_out <= 9h00;

else

data_out <= add_out;

end

endmodule

注:这里只是带着大家从电路入手,宏观的了解一下Verilog描述数字电路的结构与注意事项,具体语法可自行学习。

-

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

Verilog

+关注

关注

28文章

1351浏览量

110074 -

数字电路

+关注

关注

193文章

1605浏览量

80578

原文标题:初识Verilog描述-1

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字电路和模拟电路的工作各有何特点?

什么是数字电路

数字电路的应用介绍

新编数字电路与数字逻辑

《VHDL与数字电路设计》

什么是模拟电路 什么是数字电路

数字电路比模拟电路的优点

VHDL概述及在描述数字电路时的结构

数字电路里面有什么元素需要被描述?

数字电路里面有什么元素需要被描述?

评论