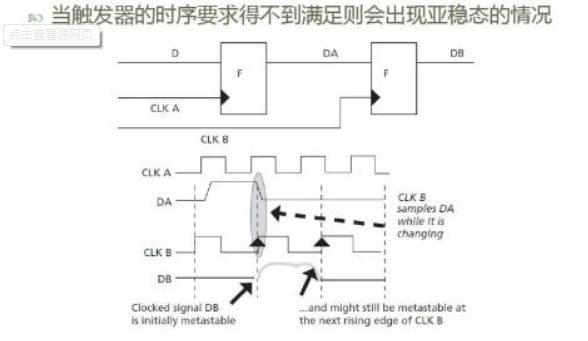

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在亚稳态期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

解决方法主要有:

(1) 降低系统时钟;

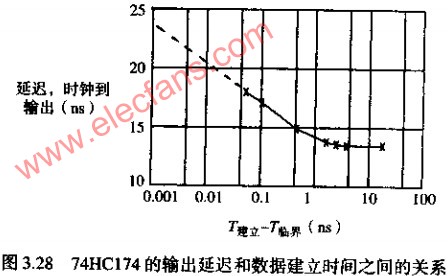

(2) 用反应更快的触发器(FF),锁存器(LATCH);

(3) 引入同步机制,防止亚稳态传播;

(4) 改善时钟质量,用边沿变化快速的时钟信号;

(5) 使用工艺好、时钟周期裕量大的器件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网

网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

触发器

+关注

关注

14文章

2000浏览量

61129 -

亚稳态

+关注

关注

0文章

46浏览量

13267

原文标题:【M博士问答】如何解决亚稳态?

文章出处:【微信号:Mouser-Community,微信公众号:贸泽电子设计圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

xilinx资料:利用IDDR简化亚稳态

`作者:Primitivo Matas Sanz,技术专家,西班牙马德里Telefonica I+D 公司,技术专家现身说教,使用触发器链(赛灵思FPGA 中ILOGIC 块的组成部分)限制设计中

发表于 03-05 14:11

FPGA触发器的亚稳态认识

的问题。亚稳态的特点: 1. 增加触发器进入稳定状态的时间。 亚稳态的坏处之一是会导致触发器的TCO时间比正常情况要大。多出来的时间tR (resolution time) 就是

发表于 12-04 13:51

FPGA设计的D触发器与亚稳态

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的

D触发器与亚稳态的那些事

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的

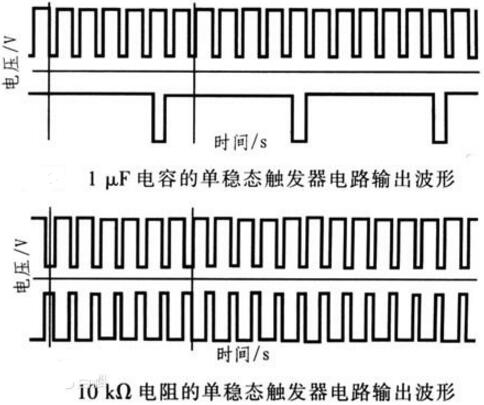

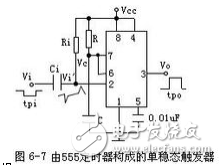

单稳态触发器的暂稳态时间与什么有关

单稳态触发器是一种能够在某个时间间隔内将输入信号的电平转换为期望的输出信号电平的数字电路。在单稳态触发器中,暂稳态时间是指当

单稳态触发器暂稳态由什么来维持

单稳态触发器(Monostable Trigger)是一种数字电路,它在接收到一个触发信号后,能够保持输出状态一段时间,然后自动返回到初始状态。单稳态

如何解决触发器亚稳态问题?

如何解决触发器亚稳态问题?

评论