FPGA调试时硬件设计中及其重要的一步,本文就在FPGA调试过程中存在3种常见的误解,进行一些讨论:

误解#1:调试工作的存在, 是因为工程师不够称职。

误解#2:单一处理方法应解决所有调试问题。

误解#3:FPGA调试硬件总是“浪费”资源。

首先针对误解#1,调试工作是设计过程的一部分

可以很负责的说:即使是最好的工程师也需要进行调试验证工作。

如果“Debugging”这个个词会让你觉得厌烦的话,我们可以换一种说法“功能验证”、“功能测试”、性能检测”等。目前虽然可以通过工程师改进技术、实现方法、以及凭借自身经验和能力解决验证过程中出现的大多数问题。但仍然取代不了验证设计在工程设计中的核心地位。在工程设计中调试工作往往会带来一定程度的复杂性,这使得调试工作已经成为电子系统设计中一个极其复杂的任务过程。

其次针对误解#2,单一处理方法无法解决所有调试问题调试工作涉及多种技术、工具,而工程师关键工作在于选择正确的技术以更有效地实现目标。

工程师常常抱怨硬件验证不能提供类如同仿真一般的可视化。但是我相信此问题的关键在于传统嵌入式LA (ILA) 受限于存储容量的大小,无法可视化足够多的调试信息。如采用合适的调试工具,则可实现理想的可视化效果。如下图可Exostiv实现大容量调试数据追踪,实现理想的可视化调试。

高达8GB的外部存储器,从而提供比现有嵌入式仪器解决方案大100.000倍的总跟踪容量

EXOSTIV超过1小时以突发方式捕获8GB数据

最后针对误解#3,调试不可能“凭空”进行,合理的调试工作是 “浪费” 节省资源。如何选择调试方案,才是“浪费”与否的关键

在调试中我们通常需要预留一部分“资源”。比如众所周知,调试工作需要预留硬件资源:如I/Os, logic and memory等FPGA资源;如连接器或者用于数据收集并保证信号完整性的某些PCB资源。

除此之位以项目的角度来分析,调试工作同样需要“工程资源”——通常是工程团队用于查找所选调试策略的错误所花费的时间。

综上情况都会使我们的项目预算产生额外的成本开销

-

PCB上用于调试的额外硬件成本;

-

逻辑分析仪或示波器的成本;

-

实施特定调试策略的工程小时成本。

如何平衡成本开销(硬件资源和工程资源),则成为选择何种调试方案的重中之重。

针对受调试工作困扰的FPGA工程师们,新的调试方案来了!!!FPGA调试利器——EXOSTIV

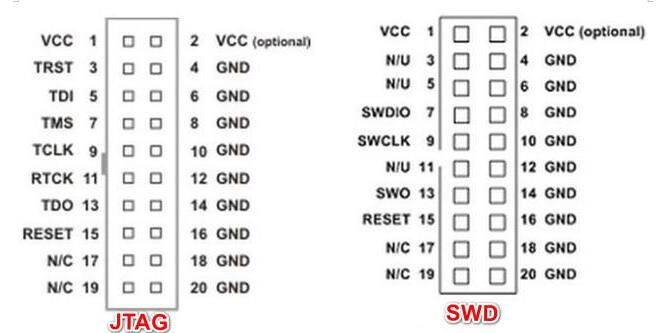

EXOSTIV™是一款面向FPGA开发的创新调试解决方案。他提供了远超JTAG调试工具的采样数据存储深度,却只使用远比逻辑分析仪少的IO资源。它对FPGA逻辑资源使用影响很小,并且能够进行TB级波形数据的分析,可大大缩短FPGA开发的调试周期。EXOSTIV支持全系列Xilinx All Programmable器件,支持Intel Stratix 10、Arria 10、Cyclone 10系列器件的调试。

EXOSTIV具有以下特色:

-

采用FPGA的串行收发器将捕获到的数据流放到一个外部存储器,并提供高达8GB的存储空间

-

最高支持32768个内部信号的连续重复捕获,可在FPGA运行速度下同时捕获数据

-

Exostiv IP提供动态多路复用控制器,可添加尽量多的捕获信号,以减少重新编译FPGA的次数

-

数据集采样的动态开关控制,充分利用收发器带宽用于更深层次的捕获

-

高达4x12.5Gbps的数据传输带宽,支持通过SFP/SFP+/QSFP/QSFP+/HDMI/FMC接口与FPGA板卡连接

Exostiv 的主营业务:

Exostiv Labs是Byte Paradigm sprl的一个部门,主要提供FPGA调试创新解决方案。

依元素科技的服务依元素科技是 Xilinx官方授权培训合作伙伴,我们除了在本地为您提供Exostiv的高性能FPGA调试工具与技术支持,我们还有全球最新的Xilinx 官方培训课程服务供您选择,能够为您的项目提供全方位的支持,缩短您的项目开发周期。

原文标题:FPGA调试的那些事.....

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

瓦克总裁预估:多晶硅价格下滑趋势不可避免

宝马:不可避免地会推出纯电动M系性能车

对工业制成品隐含能的估值需要作出的不可避免的简化和假设

传统FPGA调试方案与EXOSTIV Probe硬件调试仪

自动驾驶汽车慢慢步入低谷,既不可避免同时也是好兆头

2019年高端家电市场的价格战火不可避免

微晶体管和芯片的更新换代是不可避免的

单片机常用的调试接口有哪些

单片机常用调试的接口有哪些

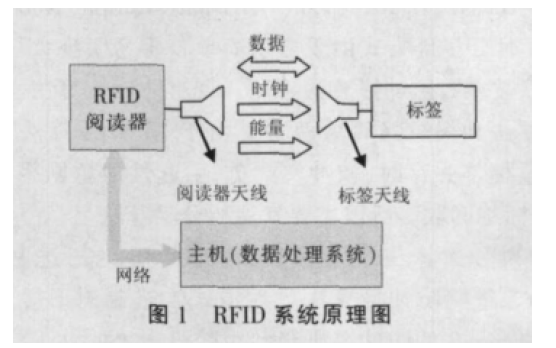

RFID技术中不可避免的碰撞问题应该如何解决

FPGA调试存在哪些不可避免的问题

FPGA调试存在哪些不可避免的问题

评论