降低PWMDAC纹波的方法通常有两种:一种是降低低通滤波器的截止频率,另一种是提高PWM信号的频率。然而,前一种方法会加长上升时间,后一种方法会导致分辨率降低。本设计实例讨论了在不使用上述两种方法的情况下,如何降低PWM DAC的纹波。

我们大多数人都知道PWM DAC(数模转换器)。它们很容易实现,也很便宜,非常适合一些低性能的应用。

实现它们的方法是滤除PWM信号中的高频分量,只留下正比于占空比的低频或直流分量。但是低通滤波器并不能完全滤除PWM频率,因此低频/直流信号中通常都会有一定程度的纹波。

减少PWM DAC纹波的方法一般有两种。一种是降低低通滤波器的截止频率,另一种是提高PWM信号的频率。然而不可避免的是,更低的截止频率会延长上升时间;如果是在给定时钟频率点通过减小计数器尺寸实现的,那么更快的PWM频率会降低分辨率。

下面要讨论的设计实例非常有趣,着重介绍了另外一种降低PWM DAC纹波的方法。

事实上,我们可以使用相位差为180°的两个PWM信号来降低上述纹波。从直觉上,当两个相同频率的正弦波的相位相差180°时,它们会相互抵消,因此我们使用相位差为180°的两个PWM信号也能将彼此的谐波分量抵消干净,是这样吗?确实是这样,但并不是PWM信号的所有谐波分量都能抵消,有些分量可以抵消,有些却抵消不了。这与傅里叶级数有关,比较复杂,这里就不罗列一大堆数学公式来进行解释了。

两个PWM信号之间180°的相位差是如何实现的呢?我使用了TI的MSP320FR5969 LaunchPad,这种方法很常用。为了实现相位移动,需要两个定时器。其中一个定时器必须包含两个比较-捕获-PWM(CCP)模块,另一个只需要一个CCP模块。

在包含两个CCP模块的定时器中,可以用一个CCP模块来设置该定时器的PWM频率和占空比,另一个CCP模块产生中断,用于启动另一个定时器,两者的延时等于PWM周期的一半。另一个定时器中的CCP模块用于设置相同的PWM频率和占空比。你还必须对这个延时进行“微调”,因为软件会在PWM信号之间增加额外的时间。举例来说,在我的代码的102行,我将比较寄存器的值从(timer_period+1)/2改为了(timer_period+1)/2-27。

我做了一些小调查,想看看其它微控制器是否具有相同的硬件和能力来实现我所用的方法:许多Atmel微控制器都有1个以上的定时器,每种控制器通常都有两个CCP(比如ATmega 328),因此实现这种方法应该是可能的。另外一个常见的例子是STM32F051R8(这是一些流行的ST电路板使用的微控制器),它有11个定时器,其中许多定时器都有1个以上的CCP。TI基于ARM的微控制器通常有独立的PWM和定时器模块(如TM4C123GH6PM),因此应该更容易实现相移。使用其中一个定时器,两个PWM模块就可以以一半PWM周期的延时开启。

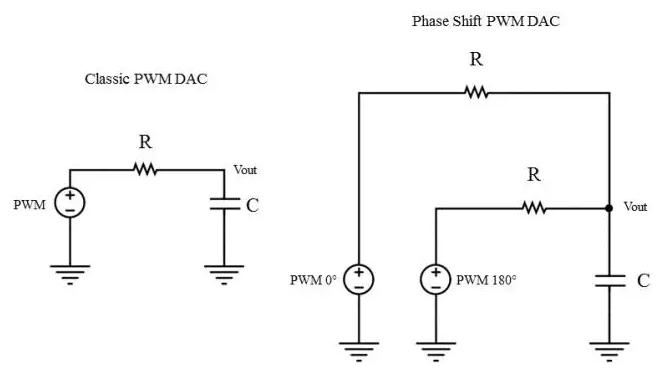

图1:单路和双路PWM电路。

在相移DAC的Vout端,两个PWM信号被累加在一起,结果有些谐波分量彼此抵消,最终实现了降低纹波的效果。

我们看看使用三种不同电阻值时的情况。每个PWM信号都是占空比为25%、频率为100kHz。

图2:上面的波形是传统PWM,下面的波形是双路相移PWM。从左到右每格的电压递减100mV、50mV、4mV。

从图中的结果可以看出:首先,峰-峰纹波降低了;其次,传统PWM DAC的纹波基频等于 PWM信号的频率(100kHz)。相移PWM DAC的纹波基频等于PWM信号的二次谐波(200kHz),这意味着我们用相移DAC成功地删除了PWM信号的一次谐波。

这种方法的一个优点是不用增加上升时间也能降低纹波(或者相同的纹波只需一半的上升时间)。

另外一个潜在优点是,将两个PWM设置为相隔一个计数值可以获得中间值,进而实现DAC有效分辨率的翻倍。虽然这会导致少许的不对称并增加纹波,但是影响很小可以忽略不计。

- PWM

+关注

关注

114文章

5026浏览量

211655 - 微处理器

+关注

关注

11文章

2206浏览量

81875 - 定时器

+关注

关注

23文章

3209浏览量

113346

发布评论请先登录

相关推荐

嵌入式微处理器体系结构 嵌入式微处理器原理与应用

嵌入式微处理器的分类 嵌入式微处理器的种类和型号

嵌入式微处理器主要组成 嵌入式微处理器的分类和特点

嵌入式微处理器的类型与特点 嵌入式微处理器技术的优缺点

嵌入式微处理器有哪几类 嵌入式微处理器包含哪些重要参数

嵌入式微处理器的功能 嵌入式微处理器原理与应用

什么是嵌入式微处理器? 嵌入式微处理器的区别

嵌入式微处理器的分类特点 嵌入式微处理器作用

主流嵌入式微处理器的结构与原理是什么 常见的嵌入式微处理器类型包括

什么是嵌入式微处理器?嵌入式微处理器有哪些?

嵌入式微处理器的原理和应用

如何降低微处理器中PWM DAC的纹波

如何降低微处理器中PWM DAC的纹波

评论