1. FPGA学习经历

阶段一:当我们刚开始学习FPGA时,一定会问到一个问题:学习Verilog还是VHDL?

阶段二:等我们学习FPGA到一定程度时参加面试时,面试者也会同样问你一个问题:你以前用Verilog还是VHDL开发?

阶段三:你已经习惯某种语言,也发现语言不是学习FPGA时需要区分的问题,它仅仅是硬件描述语言而已。可是,当你发现一份和你使用语言不同的代码作为参考时,你又开始想:我以后的工作是不是要二种语言都会,这样工作才会得心应手?

阶段四:已经很少人用硬件描述语言了,都用C语言等高级语言开发了?

.....................

当然阶段四纯属个人的对未来的推测,但是,近年来,FPGA也高速发展,明显有当年汇编语言开发到C高级语言开发的趋势,我们是不是应该不局限于只学习FPGA,而要学习下嵌入式知识,特别是Xilin最新推出的ZYNQ就是最好的切入点,集ARM和FPGA开发与一体。但是,做FPGA的人很难入门嵌入式ARM/Linux,而做ARM/Linux的也很难入门FPGA,对于集ARM和FPGA开发一体的ZYNQ,更是入门难,很多公司都要多个人开发ZYNQ,但未来的趋势肯定是FPGA2嵌入式,这也是本人开公众号的目的。

言归正传,本节内容要说的是,对于我们做FPGA开发人员来说,如何快速在Verilog和VHDL之间互转,加快开发产品的进度,而不是因为只懂某一种语言而局限了自己的开发。

2. Verilog和VHDL之间如何互转

个人目前总结的有2种方法推荐给大家:

2.1 使用EDA软件自带的语言模板

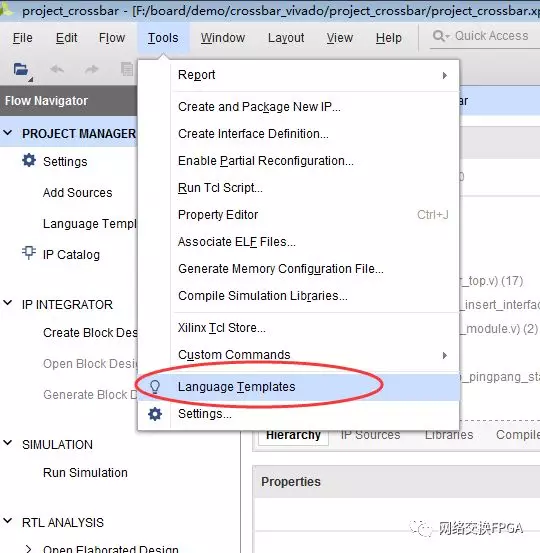

在这里,以Vivado为例,打开它里面的语言模板后,可以对比查看Verilog和VHDL之间的差异,如下图:

也可以搜索关键字,查看对应的语言模板,如下图,查看always和process时对应的语言模板:

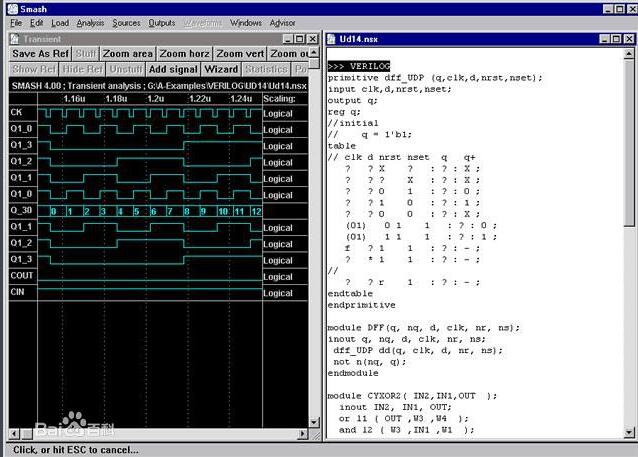

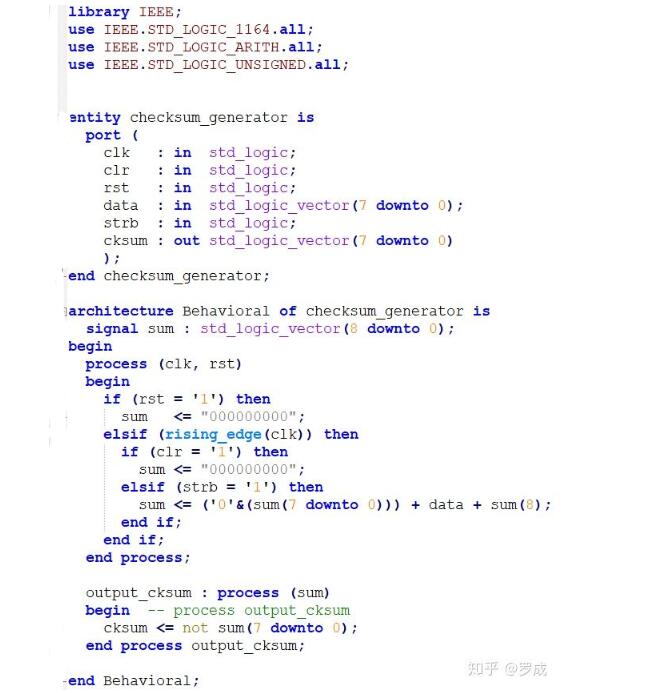

2.2 使用XHDL软件完成Verilog与VHDL之间的转换

另外,我们可以使用XHDL软件来完成互相转换。虽然它有一定的局限性,但还是足够我们用。需要注意的是:语言代码之间转换时,要求代码无语法错误,注释为英文,不能为中文,否则就会互转失败。

XHDL软件界面

XHDL测试文件(Verilog)

XHDL软件运行完成后

XHDL生成的目标文件(VHDL)

上面大致说明了XHDL的功能,但它也有一些限制,大家可以到网上下载后详细适用,如果找不到源文件,可以私信我传一份给你。

3. 总结

XHDL毕竟只是一个工具,能帮我们的有限,无法帮我们把所有的代码一键互转,还是需要我们增强自己的基本理论,记住FPGA编程中和嵌入式语言开发不同的思维方式:即一切皆硬件的思维方式。

-

Verilog

+关注

关注

28文章

1351浏览量

110073 -

C语言

+关注

关注

180文章

7604浏览量

136680 -

vhdl

+关注

关注

30文章

817浏览量

128118

原文标题:Verilog与VHDL之间互转工具(XHDL)推荐

文章出处:【微信号:FPGAer_Club,微信公众号:FPGAer俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何快速在Verilog和VHDL之间互转

write_vhdl与write_verilog有什么差异?

VHDL和Verilog 黄金参考手册

VHDL和Verilog HDL语言对比

Verilog HDL与VHDL及FPGA的比较分析

VHDL,Verilog,System verilog比较

vhdl和verilog的区别_vhdl和verilog哪个好?

vhdl转换为verilog_VHDL和Verilog谁更胜一筹

探讨VHDL和Verilog模块互相调用的问题

Verilog到VHDL转换的经验与技巧总结

Verilog和VHDL之间如何互转

Verilog和VHDL之间如何互转

评论