由Xilinx,Barefoot Networks,NetcopeTechnologies和MoSys提供的OFC 2017小组会议讨论了P4的采用,P4是用于数据包处理的新兴高级语言,以及用于FPGA和ASIC目标的P4的早期实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表德赢Vwin官网 网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- FPGA

+关注

关注

1620文章

21471浏览量

597976 - asic

+关注

关注

34文章

1171浏览量

119870 - 数据

+关注

关注

8文章

6672浏览量

88177 - 赛灵思

+关注

关注

32文章

1794浏览量

130886

发布评论请先登录

相关推荐

P4Suite for FPGA面市P4Suite for FPGA主要功能解析

发展为虚拟蜂窝基站路由器 (vCSR) 等各类网络应用打开了新大门。

P4Suite for FPGA是一项

高级设计工具, 有望变革整个网络行业。它能够基于

P4描述自动生成

数据包

使用AT SAVETRANSLINK时UDP数据包丢失怎么解决?

Android 发送一个小 UDP

数据包(5 字节)。这个小

数据包被我的微控制器在UART上接收到。微控制器将更大的

数据包(可变长度,约 100 字节)发送回 UART。ESP在UART上接

发表于07-18 07:17

在Iphone4上运行UDP接收器,数据包丢失怎么解决?

;255.255.255.255\",48899 现在使用 AT CIPSEND 每秒发送 1 个

数据包并非所有的Iphone似乎都受到严重的影响,但Iphone

4是最糟糕的。 在

发表于07-18 06:56

能否在ESP结束之前通过串行端口停止传入的UDP数据包的传输以解析下一个UDP数据包?

丢弃在ESP完成之前不需要的

数据包,以便通过串行端口发送它以接收下一个

数据包, 如果没有,我必须按顺序读取所有传入的

数据包,需要的和不需要的, 而且波特率不足,主机

处理器开销大, 我

发表于07-16 06:18

如何在AIROC GUI上获取良好数据包和总数据包?

使用 IQxel-MW LifePoint 作为发生器并发送波形BT_1DH5_00001111_Fs80M.iqvsg,但无法在 AIROC 工具中接收

数据包。 以下是从 IQxel 发送

发表于05-22 06:39

STM32H7接收数据包异常,一包接收的数据出现两包发送的内容怎么解决?

、接收到的

数据包:be1c01016de1000000000000000001000000000000000200000000000000030000000000000082ed 前

4个字

发表于03-08 08:05

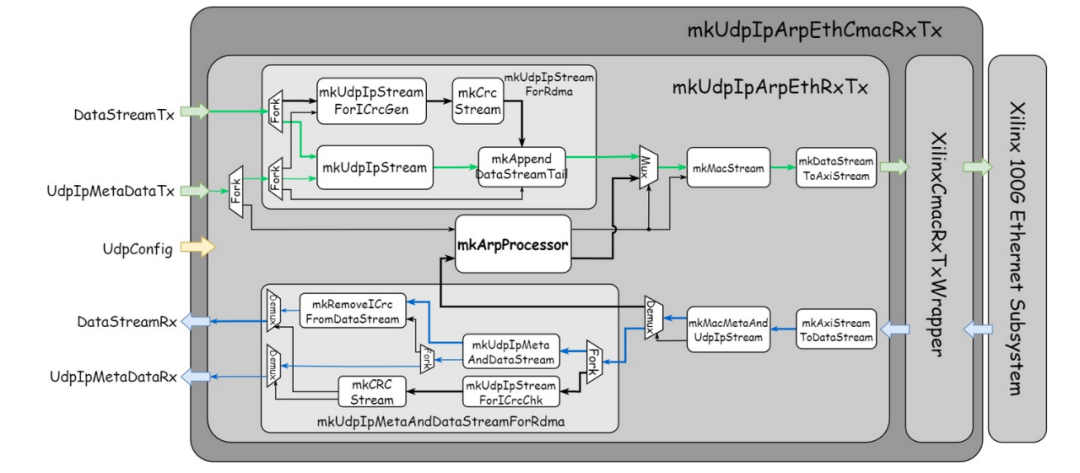

blue-ethernet高性能FPGA网络数据包处理项目简介

blue-ethernet项目使用Bluespec SystemVerilog(BSV)硬件描述

语言实现了一系列在FPGA上加速网络

数据包

处理的硬件模块。

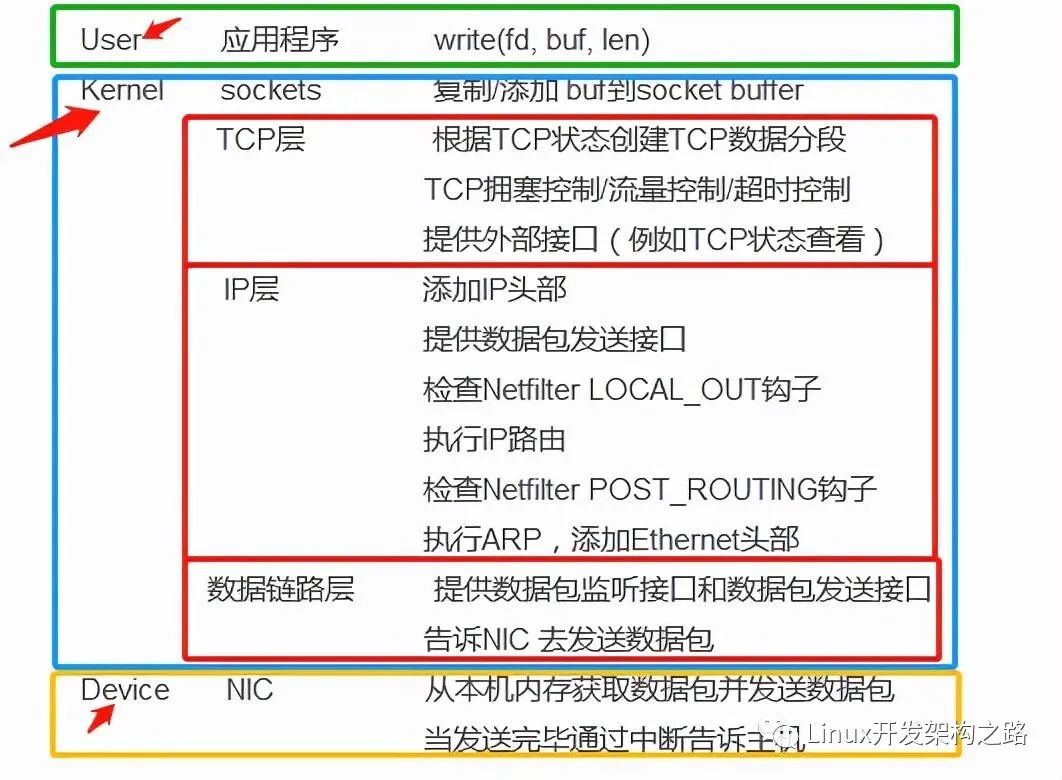

Linux场景下数据包是如何在协议层传输的

数据应用层发送

数据的过程大致如下: 我们把上述

处理过程的区域大致分为: User区域 Kernel 区域 Device区域 在user和kernel区域的任务都是由本机cpu执行,这两个区域合并称为host区域,以区分devi

用于数据包处理的高级语言P4的探讨

用于数据包处理的高级语言P4的探讨

评论