PCB设计中提高电磁兼容性能的电路措施有哪些?

答:(1) 可用在PCB走线上串接一个电阻的办法,降低控制信号线上下沿跳变速率 。

(2) 尽量为继电器等提供某种形式的阻尼(高频电容、反向二极管等)。

(3) 对进入印制板的信号要加滤波,从高噪声区到低噪声区的信号也要加滤波,同时用串终端电阻的办法,减小信号反射。

(4)MCU无用端,要通过相应的匹配电阻接电源。或接地或定义成输出端,集成电路上该接电源、地的端都要接,不要悬空。

(5) 闲置不用的门电路输入端,不要悬空,而是通过相应的匹配电阻接电源或接地。闲置不用的运放正输入端接地,负输入端接输出端。

(6) 为每个集成电路设一个高频去耦电容每个电解电容边上都要加一个小的高频旁路电容。

(7) 用大容量的钽电容或聚酯电容而不用电解电容作电路板上的充放电储能电容。使用管状电容时,外壳要接地 。

2.AD18安装好后每次打开软件都会弹出这句话,请问是怎么一回事?Could not start Vault Explorer. Please,make sure that VaultExplorer extension is installed properly

答:可能是本地程序没有河蟹干净,建议重装,先把根目录的原AD文件全部删除干净,再次安装破解时,先把杀毒软件关掉。

3.最近在使用ad 09的时候出现Preferences选项无法打开?

答:可能是软件BUG了。也可以试试快捷键TP ,也能进入此设置页面。

4.怎么把AD16的F1键进入网页的操作给取消?

答:在pcb工具栏的空白处有键选择最后一项:

进入快捷键修改栏,进行修改。

5.PCB设计中消除串扰的方法有哪几种?

答:1、两种串扰的大小均随负载阻抗的增大而增大,所以应对由串扰引起的干扰敏感的信号线进行适当的端接。

2、尽可能地增大信号线间的距离,可以有效地减少容性串扰。进行接地层管理,在布线之间进行间隔(例如对有源信号线和地线进行隔离,尤其在状态发生跳变的信号线和地之间更要进行间隔)和降低引线电感。

3、在相邻的信号线间插入一根地线也可以有效减小容性串扰,这根地线需要每1/4波长就接入地层。

4、对于感性串扰,应尽量减小环路面积,如果允许的话,消除这个环路。

5、避免信号共用环路。

6、关注信号完整性:设计者要在焊接过程中实现端接来解决信号完整性。采用这种办法的设计者可专注屏蔽用铜箔的微带长度,以便获得信号完整性的良好性能。对于在通信结构中采用密集连接器的系统,设计者可用一块PCB作端接。

6.我在等长绕线怎么是方形的?怎么换成有折角形状?

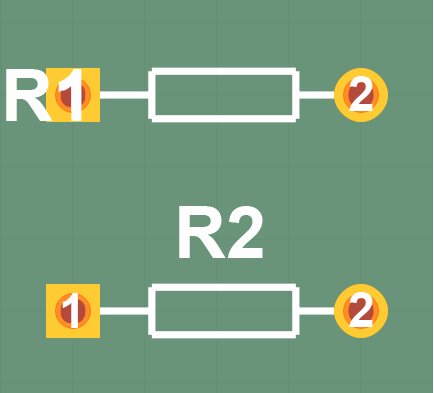

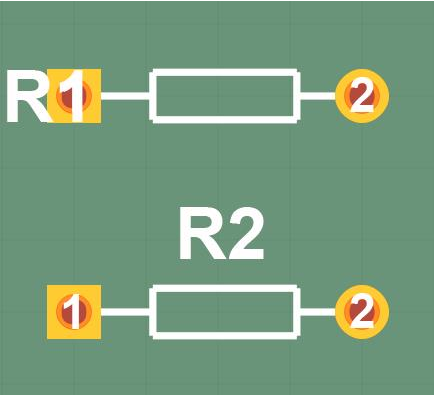

这个是设置不到位引起的 可以在等长的时候按 字母键盘上面的数字键“1”“2”来调整这个弧度,其中1为减小弧度 2位增大弧度如下图所示:

7.AD19只要我一打开pcb就一直弹错误,软件崩溃。

答:19很吃电脑配置,如果正常破解成功,出现这种情况,一般是配置跟不上,建议换个低版本。

8.新人入门,跟着老师学习AD17 89C51开发板实操,设置啥的都是跟着老师一步步弄得,但是敷铜完成后不是红色的,这是怎么回事?怎么解决呢?求大神指导

答:快捷键进TGM入进入铜皮管理器可以很清晰的看到你铜皮的情况。之后可以根据情况加以修改。

9.如何导入导出AD规则?

答:按快捷键 DR进入规则管理器然后再左侧单机右键选择Export-rule 全选所有的规则 就可以导出了。

10.PCB布局时需要排除哪些低级错误 ?

答:● 印制板尺寸是否与加工图纸尺寸相符?能否符合PCB制造工艺要求?有无定位标记?

● 元件在二维、三维空间上有无冲突?

● 元件布局是否疏密有序,排列整齐?是否全部布完?

● 需经常更换的元件能否方便的更换?插件板插入设备是否方便?

● 热敏元件与发热元件之间是否有适当的距离?

● 调整可调元件是否方便?

● 在需要散热的地方,装了散热器没有?空气流是否通畅?

● 信号流程是否顺畅且互连最短?

● 插头、插座等与机械设计是否矛盾?

● 线路的干扰问题是否有所考虑?

- 集成电路

+关注

关注

5357文章

11093浏览量

357499 - 电阻

+关注

关注

85文章

5279浏览量

170569 - pcb

+关注

关注

4280文章

22690浏览量

392037

原文标题:【技术问答】PCB布局有哪些低级错误?PCB设计中怎么消除串扰?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先登录

相关推荐

关于PCB设计中的低级错误检查步骤心得(针对于AD15)

AD15软件中对PCB低级错误检查的步骤

仪表放大器PCB布局三大常见错误_仪表放大器PCB布局的正确方法

PLC编程时最容易犯的低级错误汇总

PCB布局约束及其对组装的影响

DFM-BOM智能分析,不再出现低级错误

可能毁掉您设计的PCB布局样式错误

有可能毁掉您设计的PCB布局样式错误

PCB布局有哪些低级错误?

PCB布局有哪些低级错误?

评论