本文将从小数锁相环的需求,Delta-Sigma 小数锁相环的逻辑以及Delta-Sigma的特性三方面展开。

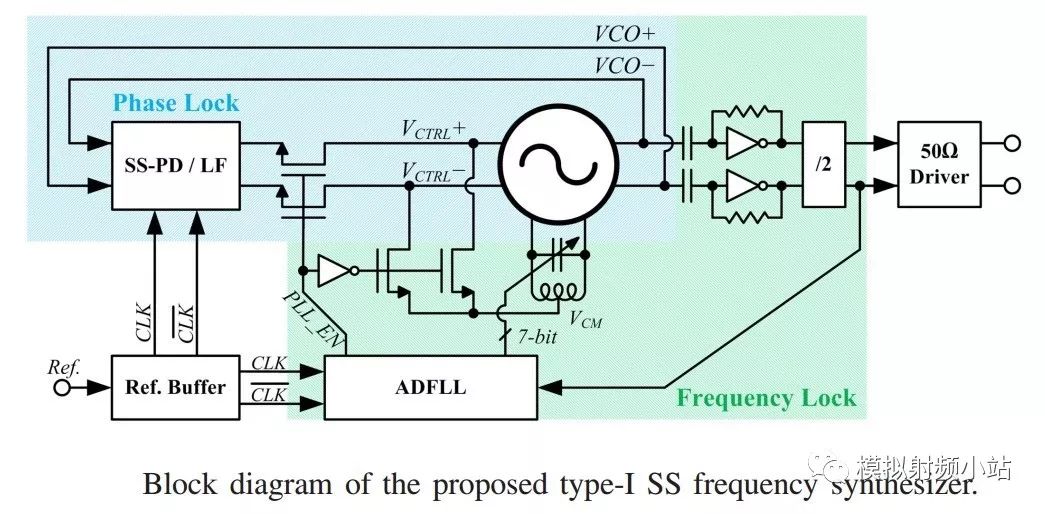

小数锁相环相对于整数锁相环来说可以极大地提高鉴频鉴相器的频率。这主要是由于系统而非器件水平的限制,因为小数分频的引入使得在较高频率鉴频鉴相器情况下也可以获得很小的输出信号频率步进。提高了鉴频鉴相器的频率带来的好处是巨大的。主要体现的可以获得更大的带宽以缩短环路锁定时间和减小输出信号相位噪声上。如果认真思考过锁相环系统传输函数就知道反馈分频系数的减小可以全方位地减小参考,VCO和电路噪声对输出信号相躁的贡献(可以参见PLL系列之二当中的系统函数)。正是基于这个系统函数的特点,才想出了以混频器代替反馈分频器和现在学术界很热门的sub-sampling(欠采样)(近年来多篇sub-samplingPLL 发表在IC界最高水平的JSSC上)等方式来优化输出的相躁。下图是SS-PLL的一个例子:

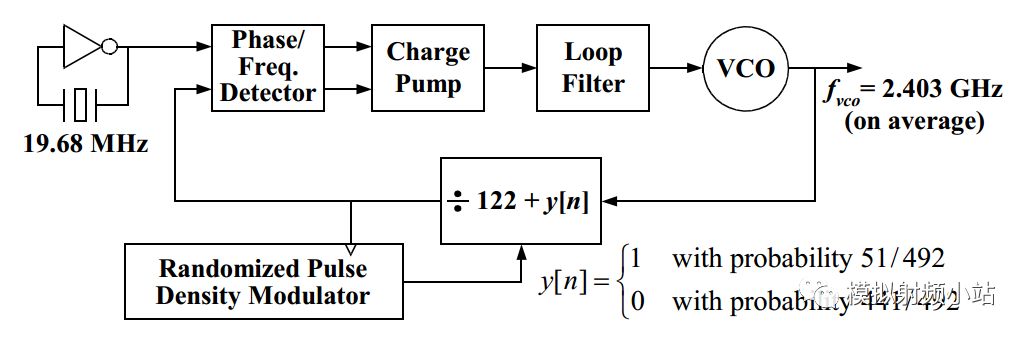

小数锁相环当中很重要的是小数分频器的实现,小数分频器有多重实现方式,近几年工业界或学术界研究比较多的是Phase-interpolator。后面有机会将另篇做介绍。在此还是介绍下传统的N/N+1双系数法,Delta-Sigma调制器也主要是跟这种方式结合在一起。举一个简单的例子,比方说我想获得10.1的频率,那么我一个采用9次10分频和1次11分频再通过平均来实现10.1的分频,怎么实现平均以及为什么可以通过平均的方式来实现?还是要回到PLL传输函数上来,正是由于环路对分频器来说是低通的特性使得这种方案跟PLL很好地结合。但事情并没有就此结束,如果我每次都是采用固定的先9次10分频再一个11分频的方式,会导致两个问题。一方面是在时间轴内不够平均,另一方面是存在周期性。以10次为轮回的循环,这将使得输出信号产生固定频率的杂散(Spur)。为了抑制这个spur就必须将整个环路带宽设置的很低。这将使得锁定时间加长同时失去了根据系统不同部位噪声水平来调节环路带宽优化相躁的自由度,这些都不是我们期望的。为了解决这个问题我们引入随机序列调制器,也就是说让10和11分频出现的时间点不规则。如下图所示的系统框图:

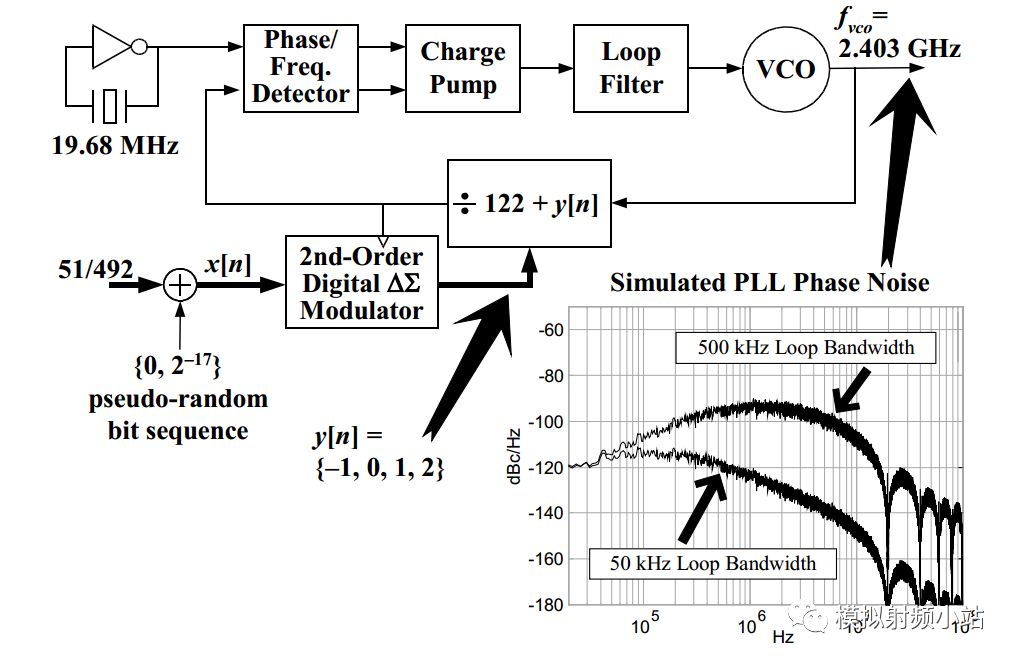

这解决了固定spur的问题,但在带内依然引入了白噪声使得输出相躁恶化。为了减小白噪声,又引入了Delta-Sigma调制器。基于Delta-sigma调制器的锁相环系统框图如下:

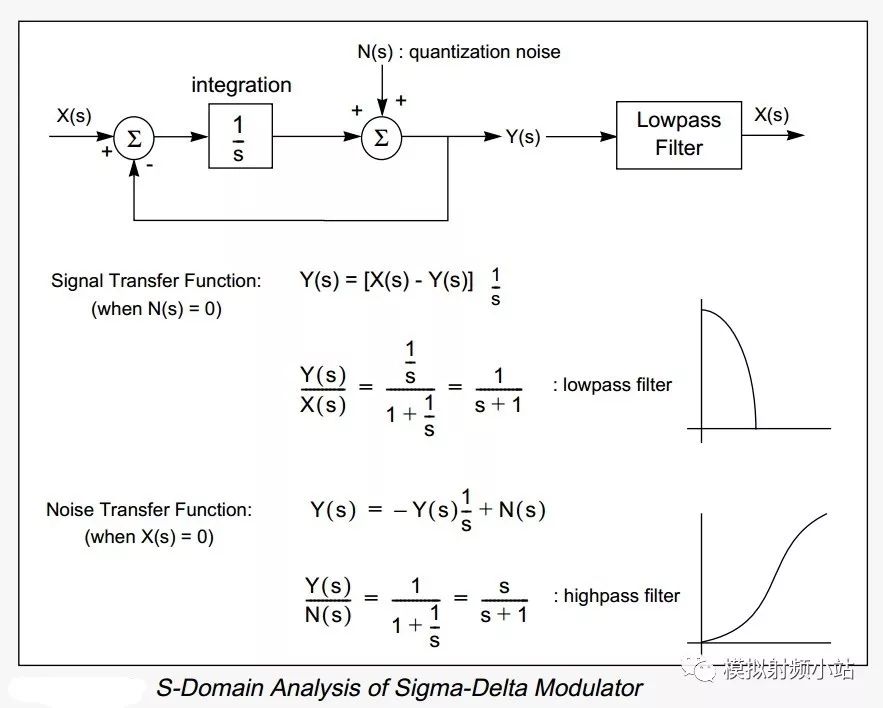

Delta-Sigma调制器的特点就是在于其对信号本身和噪声有不同的特性,将噪声推到带宽。Delta-Sigma的S域系统和频响特性如下图:

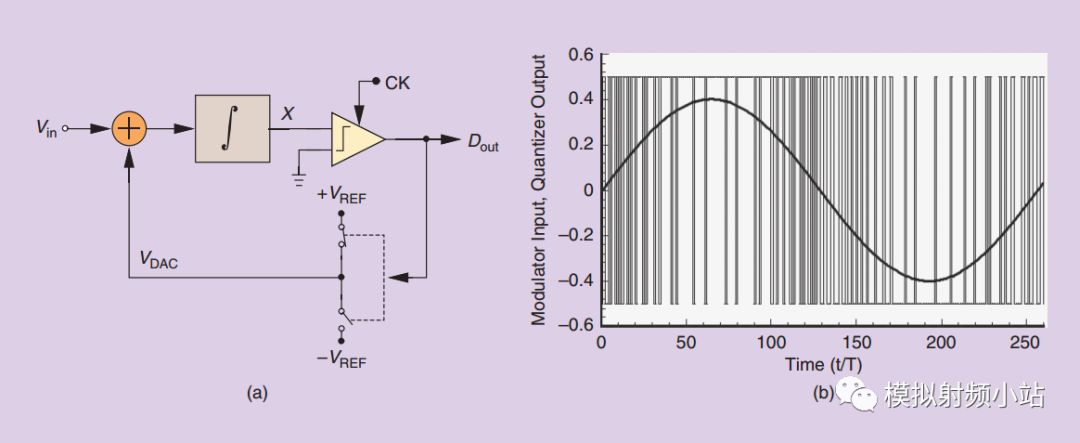

从上图可以看到整个系统对输入信号表现为低通,对噪声表现为高通,也就是压制了低频段噪声。同时上图的机智在于并没有给出量化器的精度表达了量化误差。这也就鲜明地给出了1bit和多bit量化器系统的区别仅在于多bit量化器可以减小噪声的绝对值。下图为最简单的一阶一比特量化Delta-Sigma的结构图和输入输出信号时域图:

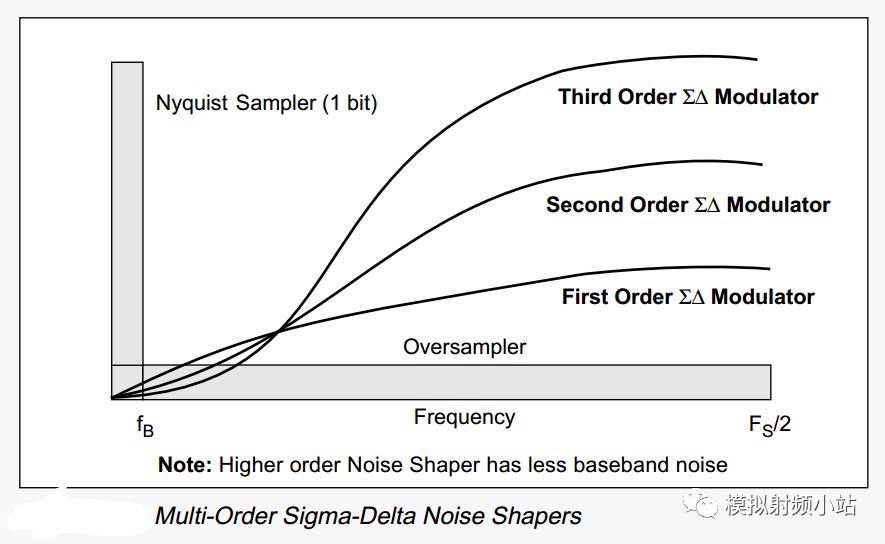

同时我们也可以通过采用更高阶的Delta-Sigma调制器或获得对低频段噪声更强的压制。高阶调制器有多重方式,最简单的方式是采用多个一阶调制器进行级联。不同阶数调制器对噪声的频响特性下图。

至此我么就讨论完了Delta-Sigma 小数锁相环。但值得注意的是这次所讨论的小数分频是用在反馈路径的分频,也就是说是闭环内的分频器。这是Delta-Sigma噪声整形技术的局限。推出可以使用在VCO之后输出级的开环小数分频技术将对工业界具有重要意义。好消息是siliconlabs 公司在这方面已经有了很成熟的产品。其时钟芯片的输出级分频也可以支持任意小数分频,也就意味着同一个VCO可以支持多个时钟域信号的输出,极大地提升了时钟芯片的灵活性。同时能够获得在12K~20MHz积分范围内jitter小于100fs。

-

锁相环

+关注

关注

35文章

584浏览量

87734

原文标题:Delta-Sigma小数锁相环解说

文章出处:【微信号:gh_025d37bb233e,微信公众号:模拟射频小站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RZ MPU Delta-sigma的工作原理 Delta-Sigma的应用简介

锁相环的原理,特性与分析

基于0.35μm工艺的Delta-Sigma ADC实现

求教delta-sigma调制的FPGA实现原理啊。

请问delta-sigma调制的FPGA实现原理是什么?

什么是Delta-Sigma转换器?ADS1232特点及应用是什么?

delta-sigma调制过后的高频噪声是怎么去掉的?

AMC1203 (Isolated Delta-Sigma

Delta-Sigma转换器的原理和应用

Accounting for delay from multiple sources in delta-sigma ADCs

Delta-Sigma小数锁相环的逻辑及特性

Delta-Sigma小数锁相环的逻辑及特性

评论